- 1JAVA海外短剧国际版系统源码的使用流程_短剧平台搭建java教程

- 2蓝桥杯练习——基础篇(10)_蓝桥杯编程竞赛指南第一章第十节

- 3什么是 Web3.js - Web3.js 库简介

- 4负载均衡_负载均衡地址能主动去向外发起访问吗

- 5手把手教你学Python之分支结构_python多分支结构怎么写句子

- 6短剧机器人插件

- 7bug解决:本地无法连接虚拟机docker中的数据库_主机访问不到虚拟机中docker数据库

- 8阿里云飞燕点灯(Linkkit-python)_阿里飞燕点灯

- 9字符串处理StringTokenizer_stringtokenizer问题

- 10vue3 + vite 项目搭建 - 配置eslint_vue3+vite devdependencies

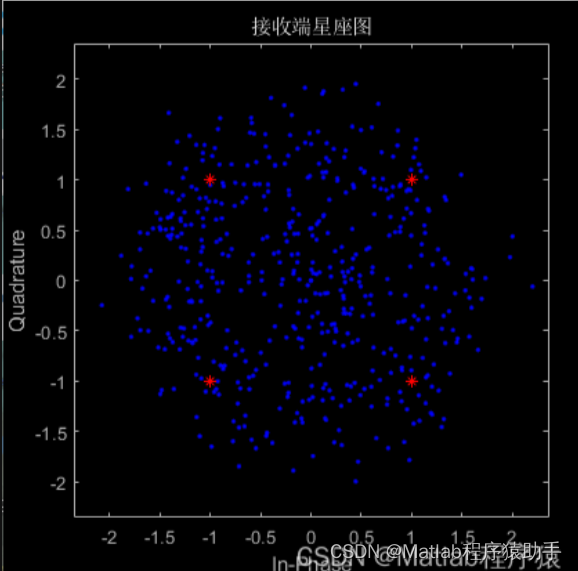

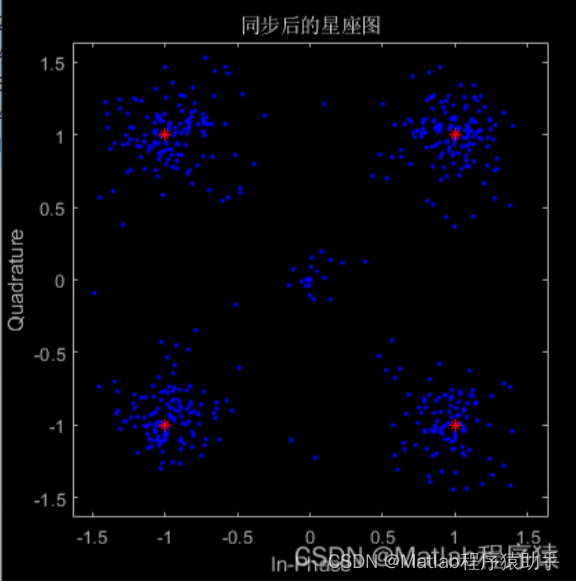

【MATLAB源码-第27期】基于matlab的QPSK定时同步仿真,采用gardner算法,Costa锁相环。

赞

踩

操作环境:

MATLAB 2022a

1、算法描述

QPSK,有时也称作四位元PSK、四相位PSK、4-PSK,在坐标图上看是圆上四个对称的点。通过四个相位,QPSK可以编码2位元符号。图中采用格雷码来达到最小位元错误率(BER) — 是BPSK的两倍. 这意味著可以在BPSK系统带宽不变的情况下增大一倍数据传送速率或者在BPSK数据传送速率不变的情况下将所需带宽减半。

数学分析表明,QPSK既可以在保证相同信号带宽的前提下倍增BPSK系统的数据速率,也可以在保证数据速率的前提下减半BPSK系统的带宽需求。在后一种情况下,QPSK的BER与BPSK系统的BER完全相同。

由于无线电通讯的带宽都是由FCC一类部门所事先分配规定的,QPSK较之于BPSK的优势便开始显现出来:QPSK系统在给定的带宽内可以在BER相同的情况下可以提供BPSK系统两倍的带宽。采取QPSK系统在实际工程上的代价是其接收设备要远比BPSK系统的接收设备复杂。然而,随着现代电子技术的迅猛发展,这种代价已经变得微不足道。

较之BPSK系统,QPSK系统在接收端存在相位模糊的问题,所以实际应用中经常采取差分编码QPSK的方式。

**锁相环(PLL)** 是一种控制系统,用于将一个参考信号的相位与一个输入信号的相位同步。它在许多领域中都有应用,如通信、无线电、音频、视频和计算机系统。锁相环通常由以下几个关键组件组成:

1. **相位比较器(Phase Comparator):** 这个组件比较输入信号和参考信号的相位差异,并输出一个反映这种差异的电压或数字信号。

2. **低通滤波器(Low-Pass Filter):** 这个组件用于平滑相位比较器的输出,以便获得一个稳定的控制电压或信号。

3. **振荡器(Oscillator):** 这是一个产生频率稳定的信号的元件,其频率可以通过调节控制电压来改变。在锁相环中,振荡器的频率可以被控制,以便使其输出的信号与参考信号的频率和相位保持同步。

4. **分频器(Divider):** 这个组件将振荡器的输出分频,生成一个或多个较低频率的信号,用于各种应用中。

**Gardner同步算法** 是一种数字通信系统中的时钟同步算法,适用于传输信道可能引入不确定延迟的情况。以下是算法的详细步骤:

1. **采样阶段:** 接收端以恒定的采样率对接收信号进行采样,得到一系列采样值。

2. **差异计算:** 算法计算相邻两个采样点之间的差异,即它们之间的信号值差。这个差异值代表了信号在传输路径中可能遭受的延迟。

3. **错误计算:** 对于每对相邻采样点,将差异值乘以它们的乘积,得到一个误差值。这个误差值可以指示接收时钟的相位相对于发送时钟的偏移。

4. **相位调整:** 根据误差值的正负,调整本地时钟的相位。如果误差为正,表示接收时钟比发送时钟快,因此需要减小本地时钟的相位;如果误差为负,则需要增加本地时钟的相位。

5. **循环迭代:** 重复以上步骤,直到接收时钟的相位与发送时钟的相位基本一致,从而实现精确的时钟同步。

总体而言,Gardner同步算法通过不断计算信号差异和调整本地时钟相位,逐步减小时钟偏移,从而实现精确的时钟同步,即使在信道质量不佳的情况下也能够有效工作。这对于数字通信系统中的数据恢复和解调至关重要。

2、仿真结果演示

3、关键代码展示

略

4、MATLAB 源码获取

点击下方原文链接获取