- 1fftw_plan_dft_1d 函数原型

- 2EasyPusher:开源RTSP直播推流Android UVC外接摄像头推送源码_android uvc rtsp推流

- 3一步步带你解锁Stable Diffusion:SD 图生图功能保姆级入门指南「上」_sd图生图怎么与原图相似

- 4鸿蒙移动开发实战:UIAbility、页面及组件的生命周期

- 5【转】微软Azure Functions使用入门_azure functions 有几种模式

- 6宝塔面板mysql无法启动的问题_宝塔mysql启动不了

- 7第一个solidity程序_spdx license

- 8TCP网络编程最佳实践_net.ipv4.tcp_rto_min

- 9主控板 & 基带板_bbu主控板和基带板作用

- 10Unity关于Oculus Quest2开发环境配置_oculus quest2开发者版本

计算机组成原理-第三章 存储系统【期末复习|考研复习】

赞

踩

前言

总结整理不易,希望大家点赞收藏。

给大家整理了一下计算机组成原理中的重点概念,以供大家期末复习和考研复习的时候使用。

参考资料是王道的计算机组成原理和西电的计算机组成原理。

第三章 存储系统

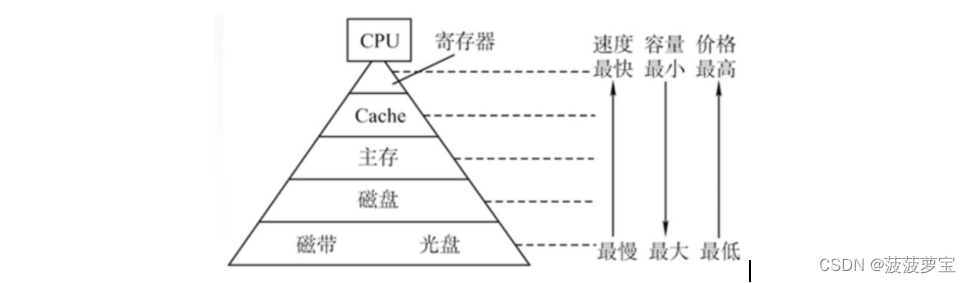

3.1 存储器的分类

按层次分:

1、主存储器(主存),CPU可以直接随机地对其进行访问,也可以和高速缓存器及辅助存储器交换数据。

2、辅助存储器(辅存),不能与CPU直接相连,用来存放当前暂时不用的程序和数据。

3、高速缓冲存储器,位于主存和CPU之间,用来存放正在执行的程序段和数据。

按存取方式分:

1、随机存储器(RAM)。存储器的任何一个存储单元的内容都可以随机存取,而且存取时间与存取单元的物理位置无关,主要用作主存或高速缓冲存储器。

2、只读存储器(ROM)。存储器的内容只能随机读出而不能写入。即使断电,内容也不会丢失。3、 串行访问存储器。

按信息的可保存性分:

1、易失性存储器,如RAM。

2、非易失性存储器,如ROM,磁表面存储器和光存储器。

3.2 存储层次化结构

主存-辅存:实现虚拟存储,解决主存容量不够。

Cache-主存:解决CPU和主存速度不匹配的问题。

3.3 半导体随机存储器

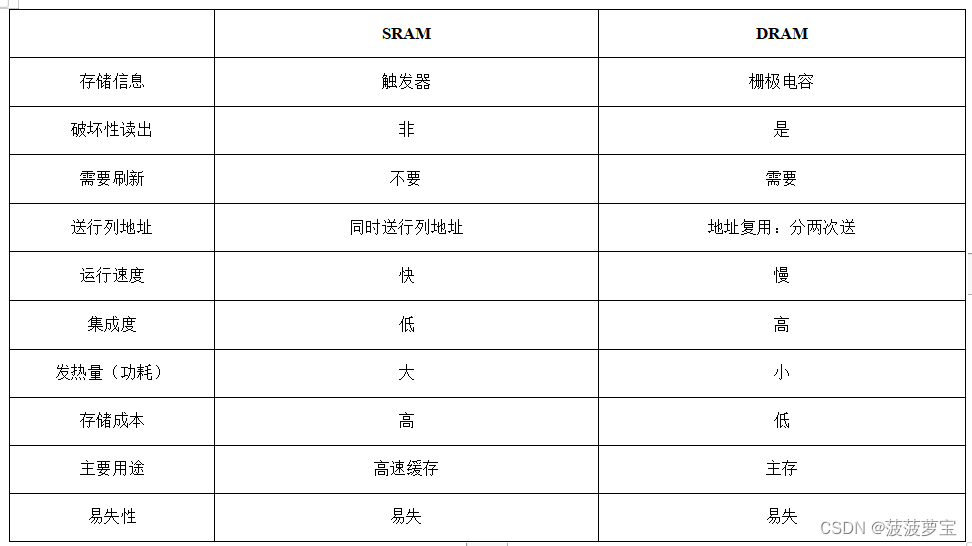

3.3.1 SRAM和DRAM(非非非非常重要)

主存由DRAM实现,Cache由SRAM实现

SRAM(静态随机存储器)的存储元是双稳态触发器,非破坏性读出,存取速度快,但集成度低,功耗较大。

DRAM(动态随机存储器)的存储元是栅极电容的电荷,采用地址复用技术,地址线为原来的一半,地址信息分行和列两次传送。具有容易集成,价位低,容量大,功耗低的特点。

DRAM的刷新时间为2ms,以行为单位,需要行地址。

刷新方式分为:

1、分散刷新,前一半读写,后一半刷新。优点:没有死区;缺点:加长了系统的存取周期。

2、集中刷新:专门有一段时间用于刷新。优点:读写不受刷新影响;缺点:有死区。3、异步刷新:隔一段集中读写时间刷新一次。既可以缩短死区,又可以充分利用刷新时间。

3.3.2 只读存储器

ROM具有结构简单,可靠性高的特点。

容量1024×8bit 前1024是地址线,后8bit是数据线。

引脚数目由地址线、片选线、数据线、读写控制线组成。

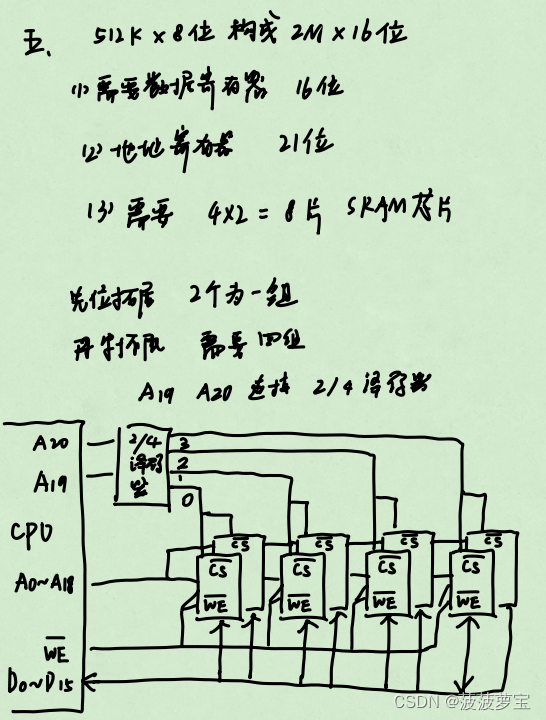

3.4 主存储器的扩展(非非非非常重要)

扩展方式跟后面的CPU那块一样重要

主存容量的扩展:

1、位扩展法:8片8K×1bit的chip连接八根数据线组成一个8K×8bit的存储器。

2、 字扩展法:用2/4或3/8译码器来区分个芯片的地址位置。

3、字位同时扩展法:两者结合。

片选信号的产生分为 :

1、线选法 :简单,不需要译码器。

2、译码片选法 。

3.5 双口RAM和多模块存储器

3.5.1 双端口RAM

双端口RAM:指同一个存储器有左、右两个独立的端口,分别具有两组相互独立的地址线、数据线和读写控制线,允许两个独立的控制器同时异步地访问存储单元。采用忙信号来从逻辑上判断暂时关闭哪个端口。

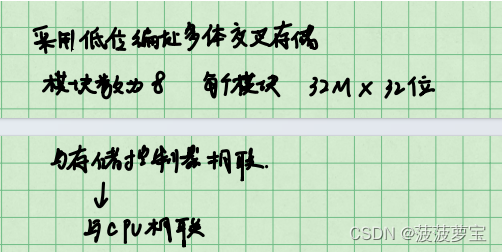

3.5.2 多模块存储器

单体多字存储器 :存储器中只有一个存储体,每个存储单元存储m个字,总线宽度也为m个字。一次并行读出m个字,地址必须顺序排列并处于同一存储单元。缺点:指令和数据必须连续存放。

多体并行存储器 :由多体模块组成,每个模块都有相同的容量和存取速度,各模块都有独立的读写控制电路、地址寄存器和数据寄存器,既能并行工作,又能交叉工作。

多体并行存储器由分为高位交叉编址(顺序方式)和低位交叉编址(交叉方式)

高位交叉编址 :高位地址表示体号,低位地址为体内地址。

低位交叉编址 :低位地址为体号,高位地址为体内地址。地位交叉编址更适合顺序连续访问,存取模块可以并行访问。二高位交叉编址只能串行访问。

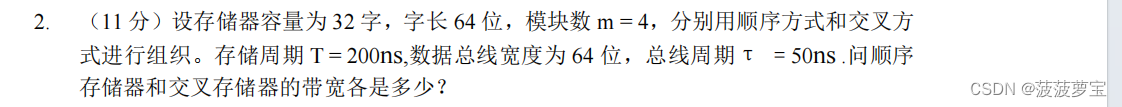

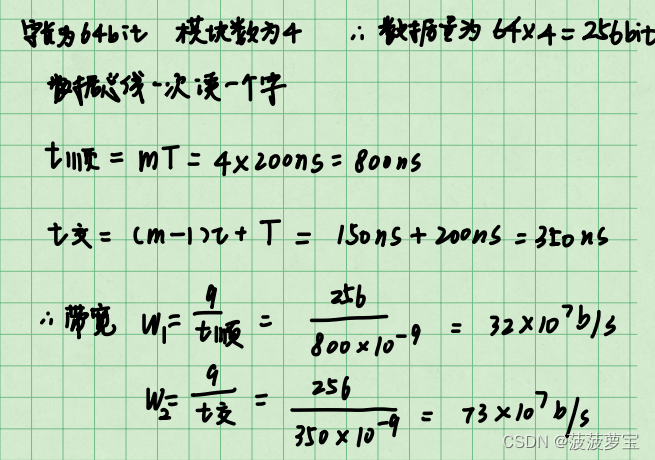

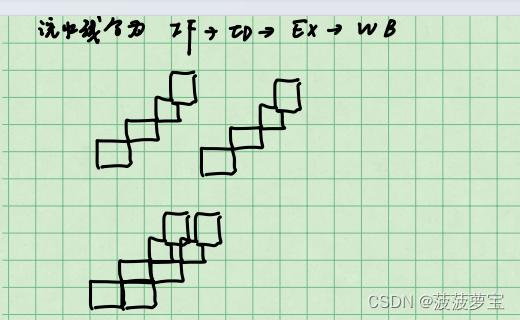

流水线方式,存储器交叉模块数应大于等于 m=T/r (T为存取周期,r为总线传送周期),连续读取m个字所需时间为t1=T+(m-1)r,而顺序方式连续读取m个字所需时间为t2=mT

低位交叉的多体存储器,俗称双通道。

3.6 高速缓冲存储器

高速缓冲技术就是利用程序访问的局部性原理 。

当CPU发出读请求时,如果访存地址在Cache中命中,就将此地址转换成Cache地址,直接对Cache进行读操作,与主存无关;如果Cache不命中,则仍需访问主存,并把此字所在的块一次从主存调入Cache内。若此时Cache已满,则需根据某种替换算法,用这个块替换掉Cache中原来的某块信息。CPU与Cache之间的数据交换以字位单位,而Cache与主存之间的数据交换以Cache块为单位。

3.6.1 Cache和主存的映射方式

直接映射(对号入座):

主存中的每一块只能装入Cache中的唯一位置,若位置已有内容,原来块将无条件被替换出去。直接映射关系可表示为:j = i mod 2^c(j是Cache的块号,又称行号,i是主存的块号,2 ^c是Cache的总块数)。

直接映射地址结构:标记、Cache行号、块内地址。

访问过程:先访问行号c位,找到在Cache中的位置,然后再对标记位进行对比,若相等且有效位为1,则命中,反之不命中,CPU从主存读出该地址送到相应Cache并且有效位置为1,标记设为地址中高t位,且将内容送到CPU。优点:实现简单。缺点:不够灵活,冲突概率最高,空间利用率最低。

全相联映射(随意放):

优点:比较灵活,冲突概率低,空间利用率高,命中率也高。缺点:标记比较较慢,通常采用昂贵的按内容寻址的相联存储器进行地址映射。

组相联映射(按号分组,组内随意放):将Cache分为大小相同的组,组间采用直接映射,组内采用全相联映射。

3.6.2 Cache中主存块的替换算法

1、随机算法RAND:没有依据程序访问的局部性原理。

2、先进先出算法FIFO:没有依据程序访问的局部性原理。

3、近期最少使用算法LRU。

4、最不经常使用算法LFU

3.6.3 Cache写策略

对于Cache写命中 :

1) 全写法 (写直通法write-through):必须把数据同时写入Cache和主存

2) 写回法 (write-back):只修改Cache的内容,而不立即写入主存,只有当此块被换出时才写回主存

对于Cache写不命中 :

1) 写分配法 (write-allocate):加载主存中的块到Cache中,然后更新这个Cache块

2) 非写分配法 (not-write-allocate):只写入主存,不进行调块

非写分配法通常与全写法合用,写分配法通常和写回法合用。各级Cache之间采用全写法+非写分配法。Cache和主存之间采用写回法和写分配法。

3.7 虚拟存储器

同时具有虚拟页式存储器(有TLB)和Cache的系统中,访问顺序为TLB->页表->Cache->主存。

虚拟存储器和Cache的不同之处 :1)Cache主要解决系统速度,而虚拟存储器是为了解决主存容量。2)Cache全由硬件实现,是硬件存储器,对所有程序员透明;而虚拟存储器由OS和硬件共同实现,是逻辑上的存储器,对系统程序员不透明,但对应用程序员透明。3)虚拟存储器系统不命中时对系统性能影响更大。4)Cache不命中时主存能和CPU直接通信,同时将数据调入Cache中;而虚拟存储器系统不命中时,只能先由硬盘调入内存中,而不能直接和CPU通信。

4 基础练手题

4.1

4.2

4.3

4.4

4.5

4.6

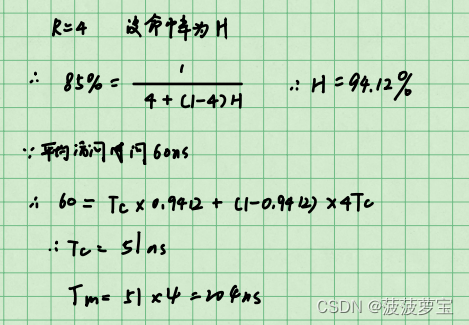

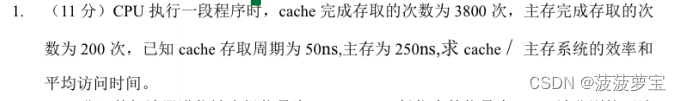

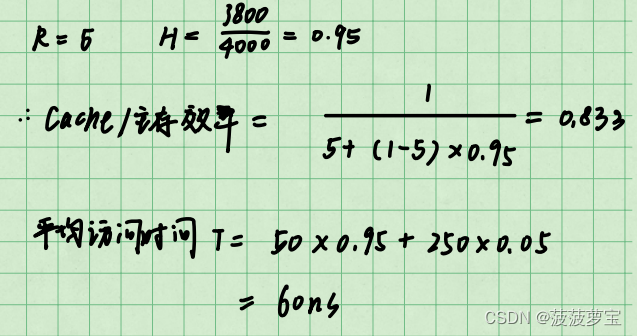

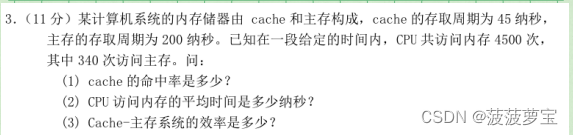

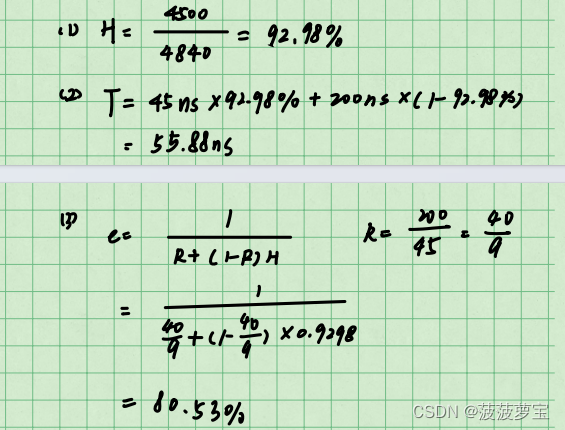

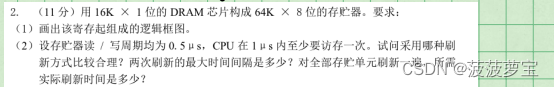

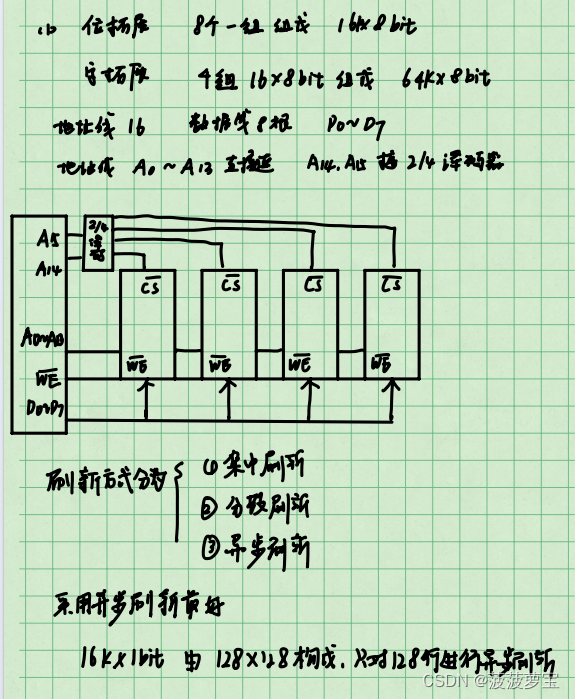

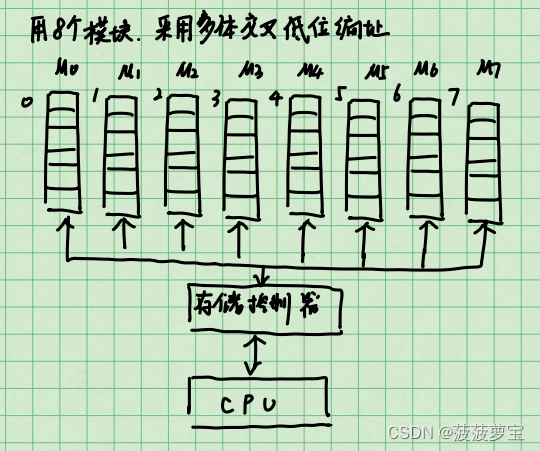

5 综合练手题(非常非常非常非常重要)

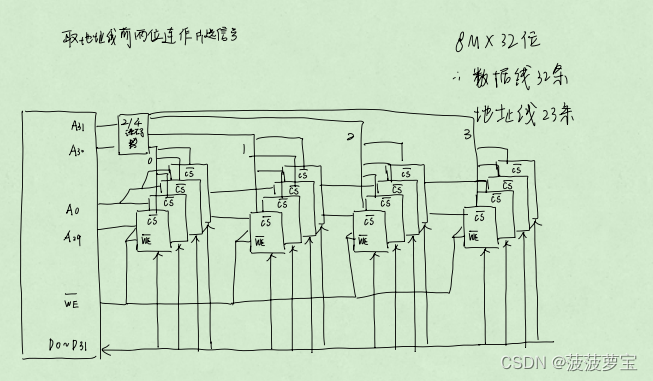

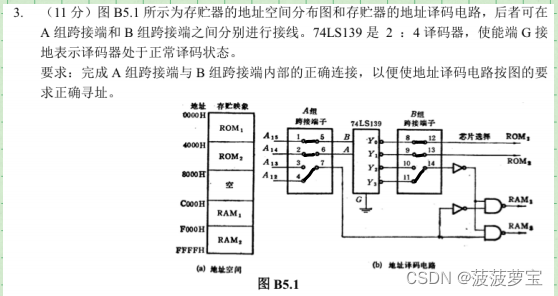

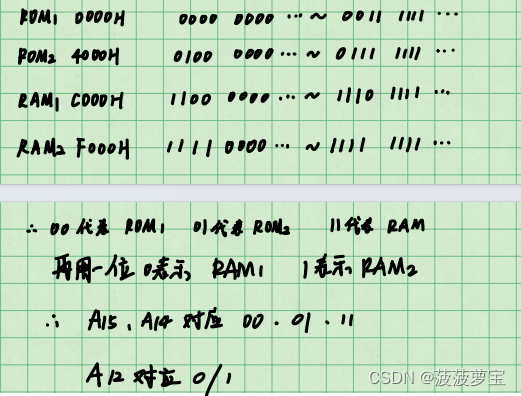

5.1

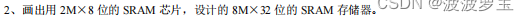

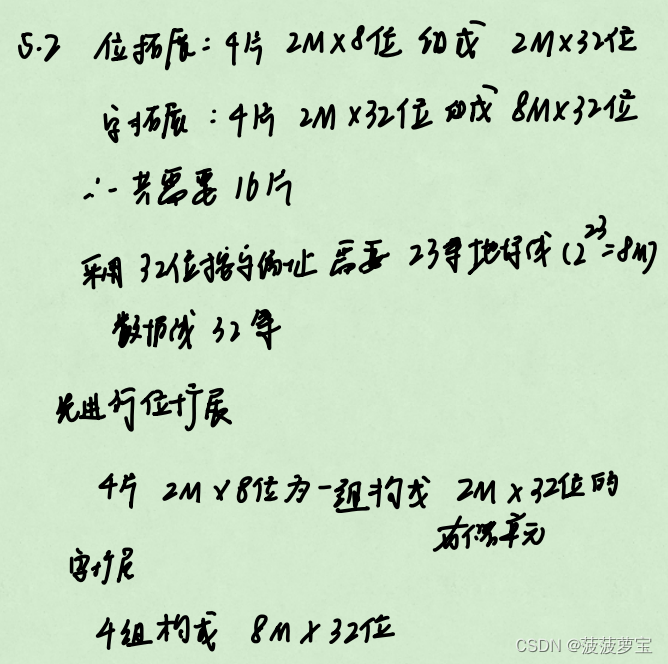

5.2

5.3

5.4

5.5

5.6

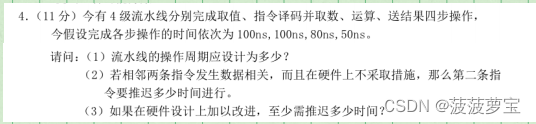

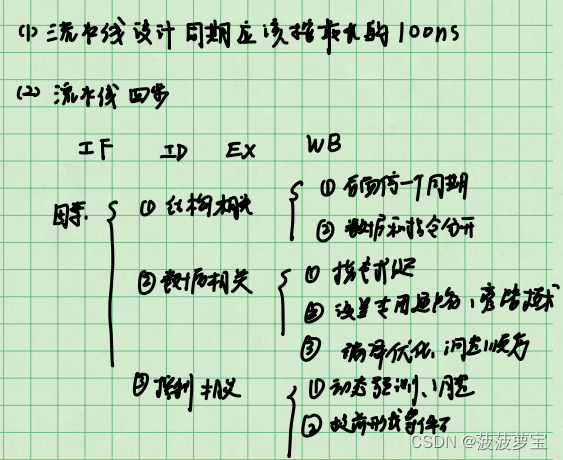

流水线相比于上面几道不是那么重要(我也不敢说不考),但也要做几个维持手感

5.7

总结

相信这一章的干货也是满满,这些题有不会的评论区留言,我也可以解答=v=有遗漏的我再补充