热门标签

热门文章

- 1kube-bench初体验

- 2python头歌-python第六章作业_头歌python第六章作业答案

- 3嵌入式开发-各种干货_dsk嵌入视频

- 4Python 中filter函数用法

- 5etcd 与 Zookeeper、Consul 等其它 kv 组件的对比

- 6Java面向对象:封装、继承、多态_java面向对象 - 封装、继承和多态头歌

- 7androidsdktools安装_Android-sdk 安装

- 8使用javaAPI对HDFS进行文件上传,下载,新建文件及文件夹删除,遍历所有文件_hadoop 遍历hdfs指定文件夹

- 9spark 类别特征_Spark 贝叶斯分类算法

- 10聚焦AI4S,产学研专家齐聚,探讨AI工具在多领域应用的现状与趋势

当前位置: article > 正文

基于Quartus-II软件完成一个1位全加器的设计_quartus实现有符号二进制加法

作者:凡人多烦事01 | 2024-05-18 14:55:17

赞

踩

quartus实现有符号二进制加法

一.什么是全加器

1.概念

全加器是能够计算低位进位的二进制加法电路为一位全加器。而半加器电路指对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。是实现两个一位二进制数的加法运算电路。

一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

2.一位全加器

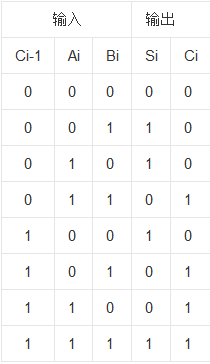

一位全加器的真值表如下图,其中Ai为被加数,Bi为加数,相邻低位来的进位数为Ci-1,输出本位和为Si。向相邻高位进位数为Ci [1]

二.实现

1.新建

启动Quartus-||,新建工程选择芯片EP4CE115F29C7芯片。

2.绘制原理图

如图

推荐阅读

相关标签