- 1ACL+SASL的认证配置后的Kafka命令操作(Windows版)_respondtoserver sasl authentication failed using l

- 2【SpringBoot】SpringBoot中使用AOP实现日志记录功能

- 3嵌入式0基础开始学习 Ⅱ 数据结构(1)数据结构

- 4分布式文件系统HDFS及其简单使用_分布文件系统hdfs的helloword程序演示

- 5vLLM 部署 Qwen_vllm部署qwen

- 6悬赏“黄金夹克”主人,来认证精英会兑现大满贯荣耀

- 7为hexo+landscape主题添加百度统计功能_hexo+landscape主题统计用户访问

- 8解决Android Gradle plugin requires Java 17 to run. You are currently using Java的具体操作步骤

- 9Java数据结构与算法(1)_数据结构与算法是一门

- 10什么是SLA服务可用性

Vivado仿真功能_vivado 仿真

赞

踩

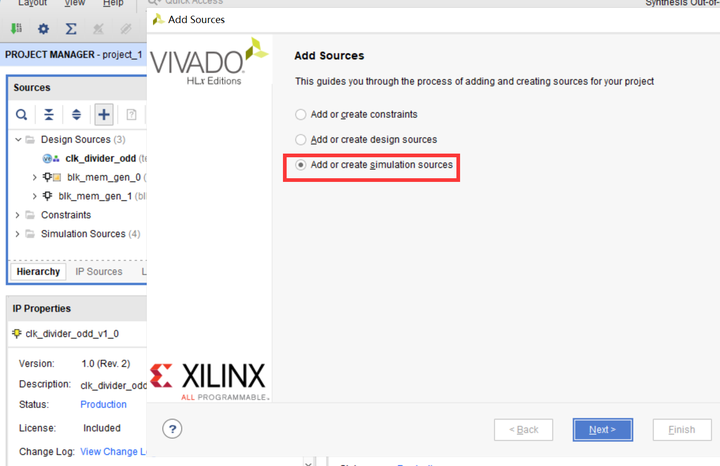

仿真是FPGA开发中常用的功能,通过给定测试激励,对比输出结果,来验证设计的功能性。本文将介绍vivado中仿真功能的使用。

一、 仿真功能概述

Vivado支持:Vivado Simulator、Questa、ModelSim、IES、VCS、Rivera-PRO和Active-HDl等等仿真工具。

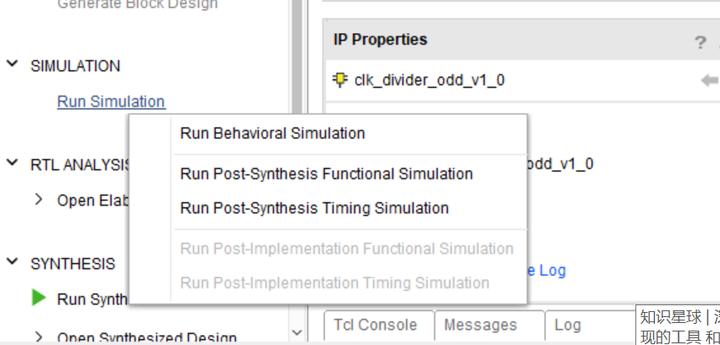

vivado中的仿真可以分为三种:

RTL级行为仿真:一种在综合和实现前用来验证设计的方法,主要用来检测模块的功能是否符合要求。

综合后仿真:综合后使用网表进行仿真,以验证综合后设计是否满足要求,包括时序仿真和功能仿真。

实现后仿真:布线实现后进行功能仿真和时序仿真,接近真实的运行情况。

注意:综合后仿真和实现后仿真,运行耗时较长,一般不用。

二、测试激励

测试激励(Testbench)是一种用于仿真的输入信号,主要用于触发设计中的逻辑流程并生成仿真波形。在Vivado中,我们可以使用Verilog或VHDL编写测试激励代码,在仿真过程中使用该代码来生成输入信号。

Vivado Simulator支持VHDL(IEEE-STD-1076-1993)、Verilog(IEEE-STD-1364-2001)、SystemVerilog中的可综合子集(IEEE-STD-1800-2009)三种硬件描述语言,此外还支持IEEE P1735加密标准。

在实际应用中,测试激励可以根据需求进行定制,例如添加复杂的数学计算,以更好地测试设计的性能。

推荐阅读:TestBench内容编写与方法总结

三、 第三方仿真器设置

Vivado除了自带的仿真器以外,还有一些第三方仿真器可供选择。使用第三方仿真器可以提高仿真效率和灵活性,并允许设计人员使用他们熟悉的工具进行仿真。

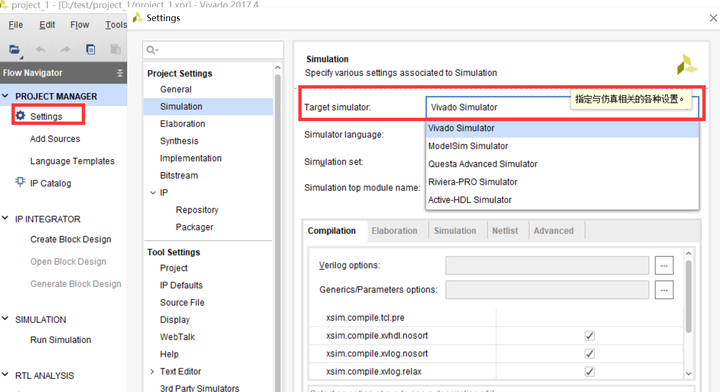

在使用第三方仿真器之前,需要将其设置为Vivado的默认仿真器。这可以通过Vivado中的仿真设置完成。首先,进入Vivado的“Flow Navigator”中选择“Settings”,然后选择“Simulation”,设置默认仿真器为第三方仿真器。

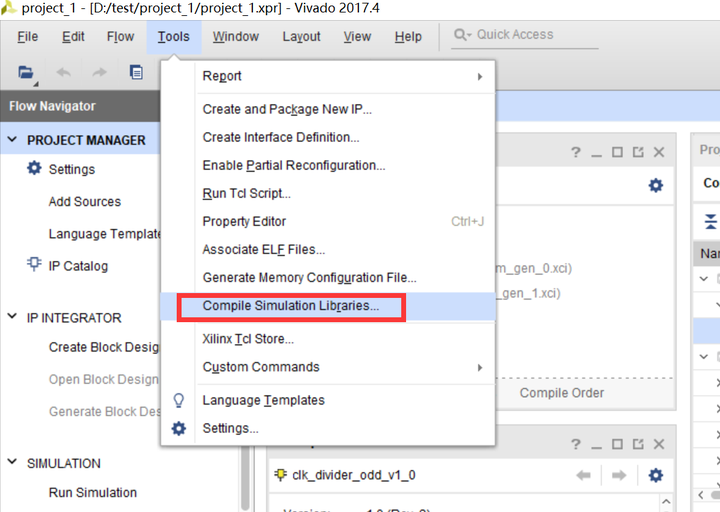

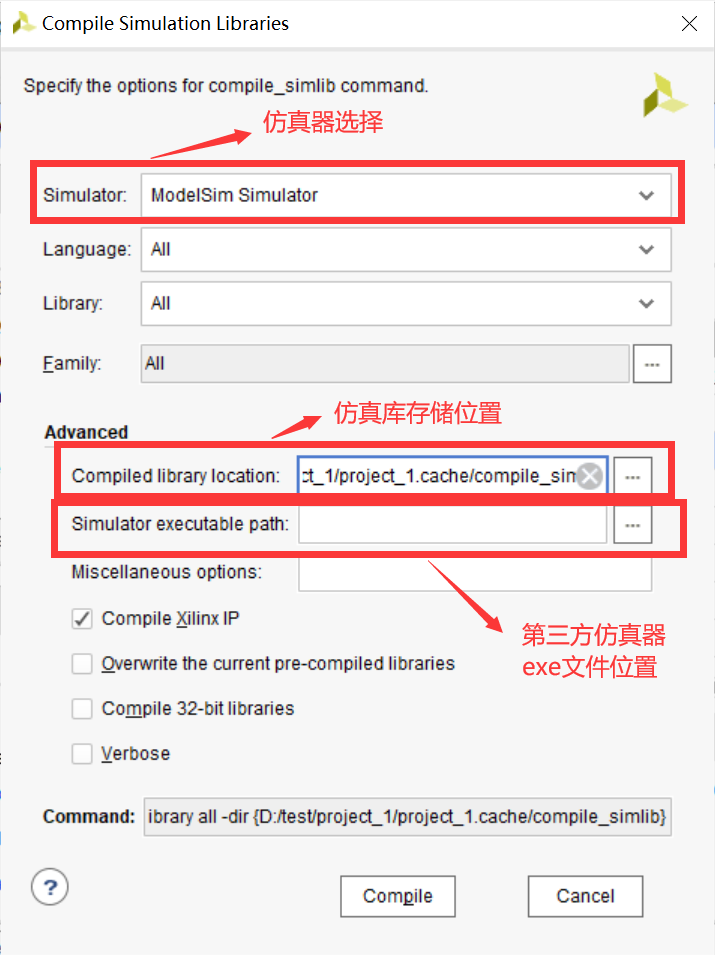

四、仿真库编译

使用Vivado Simulator时,不需要编译仿真库。如果使用第三方仿真工具时,则必须先编译仿真库,才能正确运行。仿真库中包含了仿真模型,比如FPGA和IP的行为模型和时序模型。编译之后的库可以在多个设计工程中使用。

编译仿真库的方法,如下图:

五、 仿真设置

在vivado仿真设置中,设定目标仿真器、仿真集、仿真顶层模块名称等选项,如下图所示

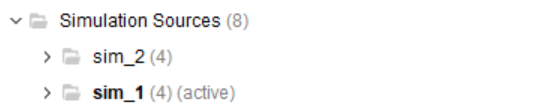

六、仿真集功能

Vivado提供了仿真集(Simulation Sets)功能,可以将不同设计阶段所用到的不同测试激励添加到不同的仿真集中。

当工程中有多个仿真集时,当前正在使用的仿真集会标注为Active状态:

七、 总结

本文介绍了FPGA开发中的仿真功能,包括测试激励、第三方仿真器设置、仿真库编译、仿真设置、仿真集功能等方面的内容。

本文将不断定期更新中,点⭐️赞,收⭐️藏一下,不走丢哦

本文由FPGA入门到精通原创,有任何问题,都可以在评论区和我交流哦

公众号为“FPGA入门到精通”,免费学习资料大礼包下载,github开源代码:“FPGA知识库”

你的支持是我持续创作的最大动力!如果本文对你有帮助,请给一个鼓励,谢谢。