- 1【Ubuntu】Ubuntu 22.04 升级 OpenSSH 9.3p2 修复CVE-2023-38408_ubuntu22.04升级openssh

- 2YOLOv10论文解读——实时的端到端目标检测模型【附结构图】

- 3java加密算法pbkdf2_pbkdf2加密算法工具类

- 4STM32CUBEMX配置教程(三)通用GPIO配置_stm32cubemx怎么设置gpio精准输出

- 5从0到1搭建一台属于个人的服务器,永久可运行!

- 6评价得分计算:确立权重的方法

- 7JAVA程序员面试系列(二)_为啥java需要二面

- 8Jenkins的部署过程,从输入分支名开始,后台都经历了哪些

- 9Ollama配置webui连接大预言模型_ollama ui

- 10用树莓派4B安装gitlab,亲测可用~_树莓派 gitlab

Vivado_ILA IP核

赞

踩

本文介绍Vivado的ILA(Integrated Logic Analyzer)的使用,其ILA版本为6.2。

使用步骤

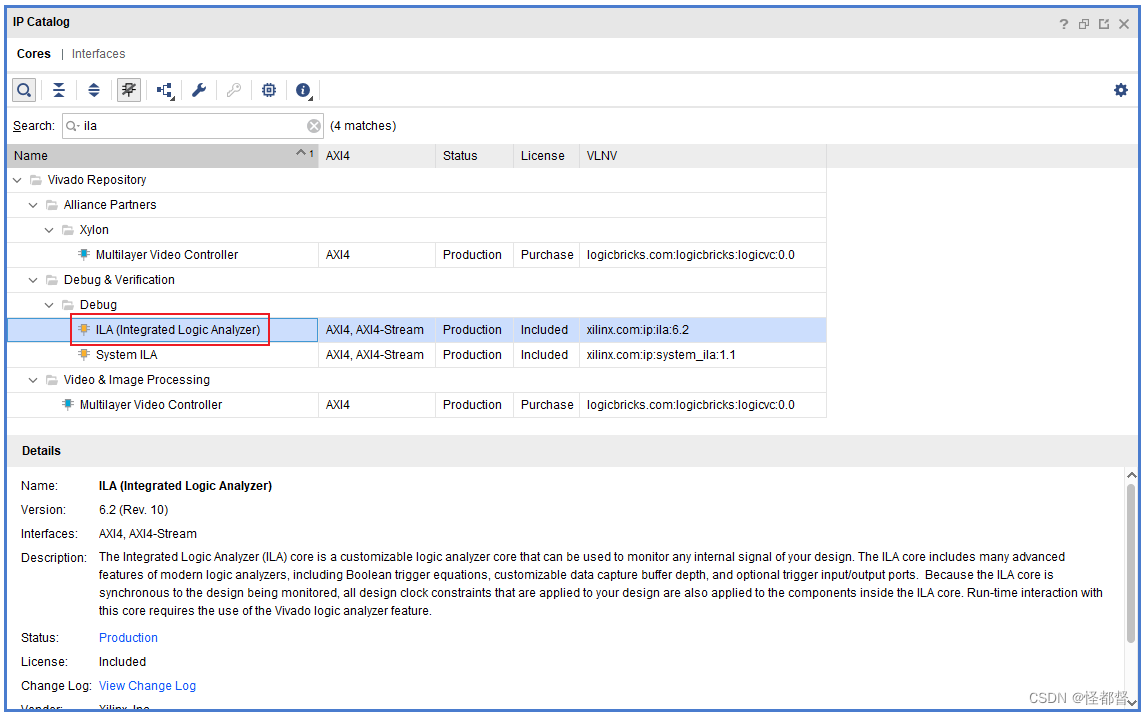

首先在IP Catalog中搜索找到ILA。

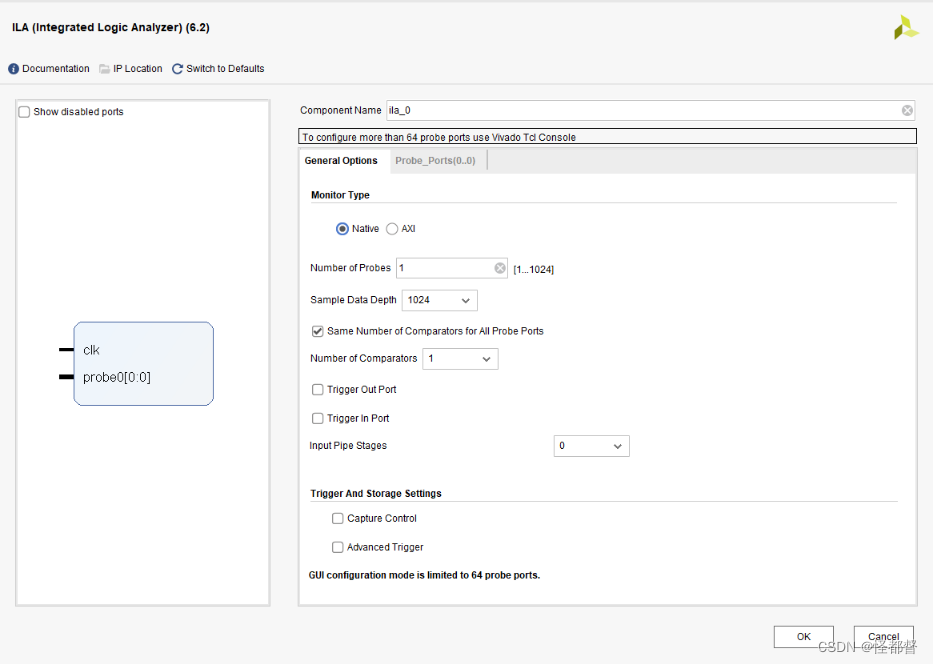

双击并打开后,界面如下。

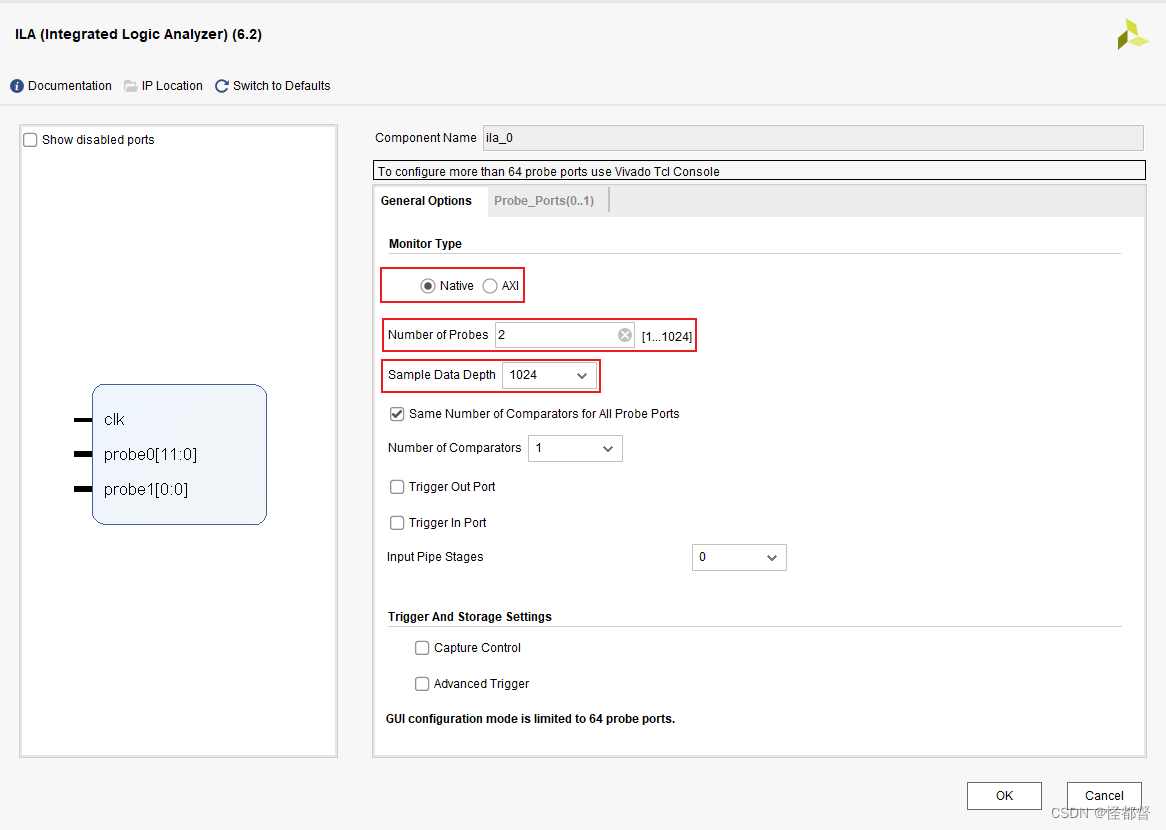

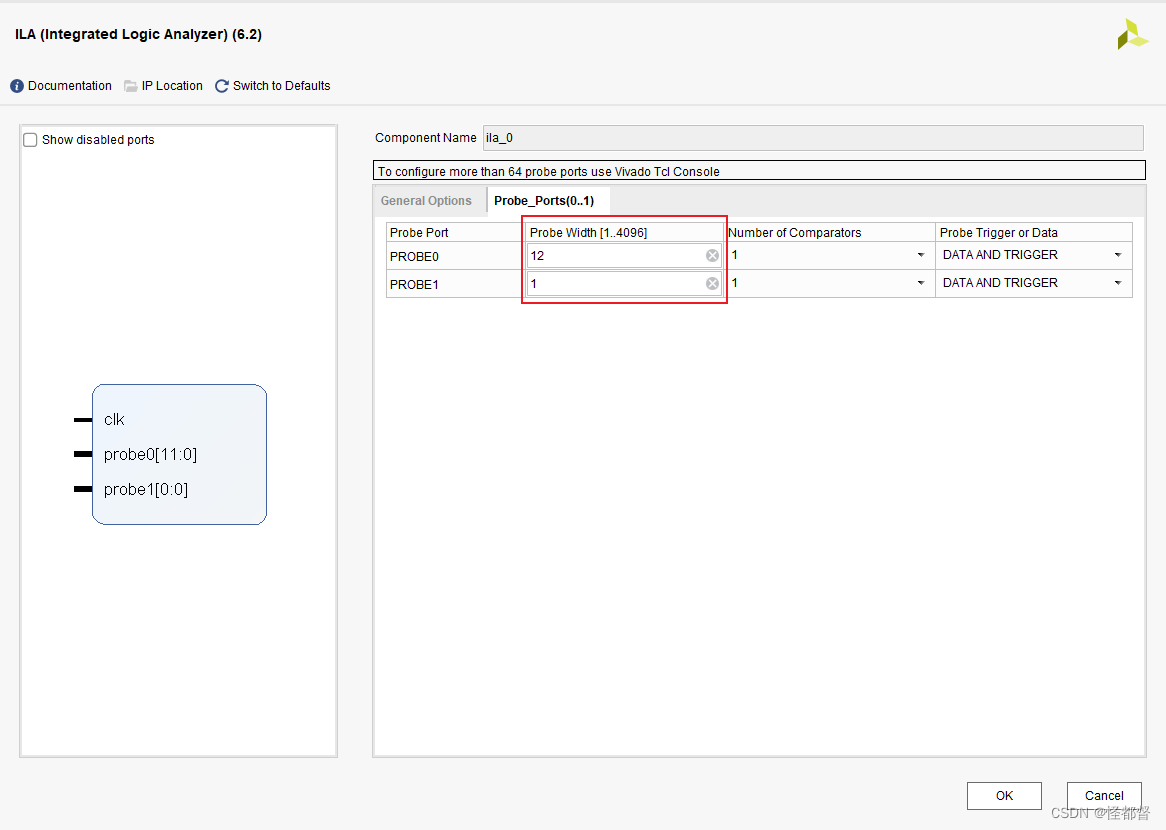

常规使用下,只需设置General Options中的接口类型为Native,Number of Probes 探针数量,Sample Data Depth 样本数据深度,和Probe_Ports中的Probe_Width探针位宽。

如需要查看ADC输出的12位数据,故将probe0的位宽设置为12。

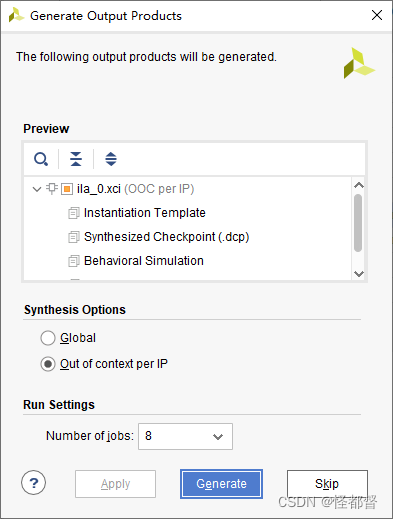

接着,点击OK,并点击下图中Generate生成ILA实例。

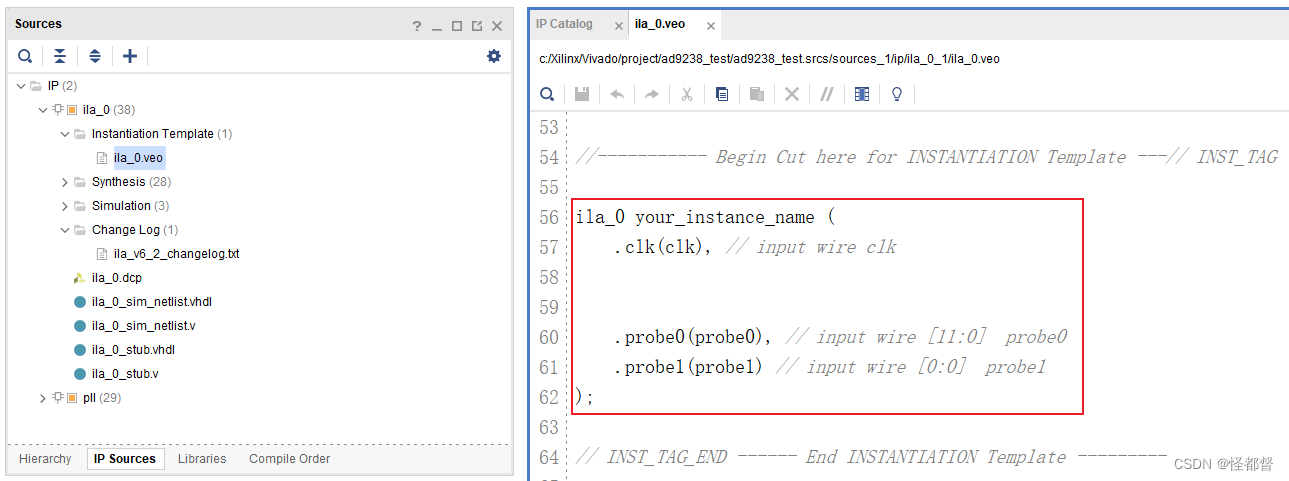

在IP Sources中找到ila_0 -> Instantiation Template -> ila_0.veo 实例化模板代码。

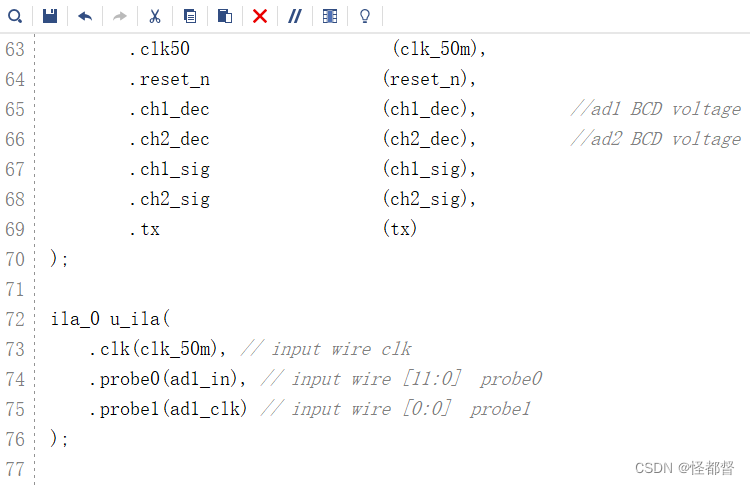

将其复制到顶层模块中,并根据需要写入需要查看的信号。

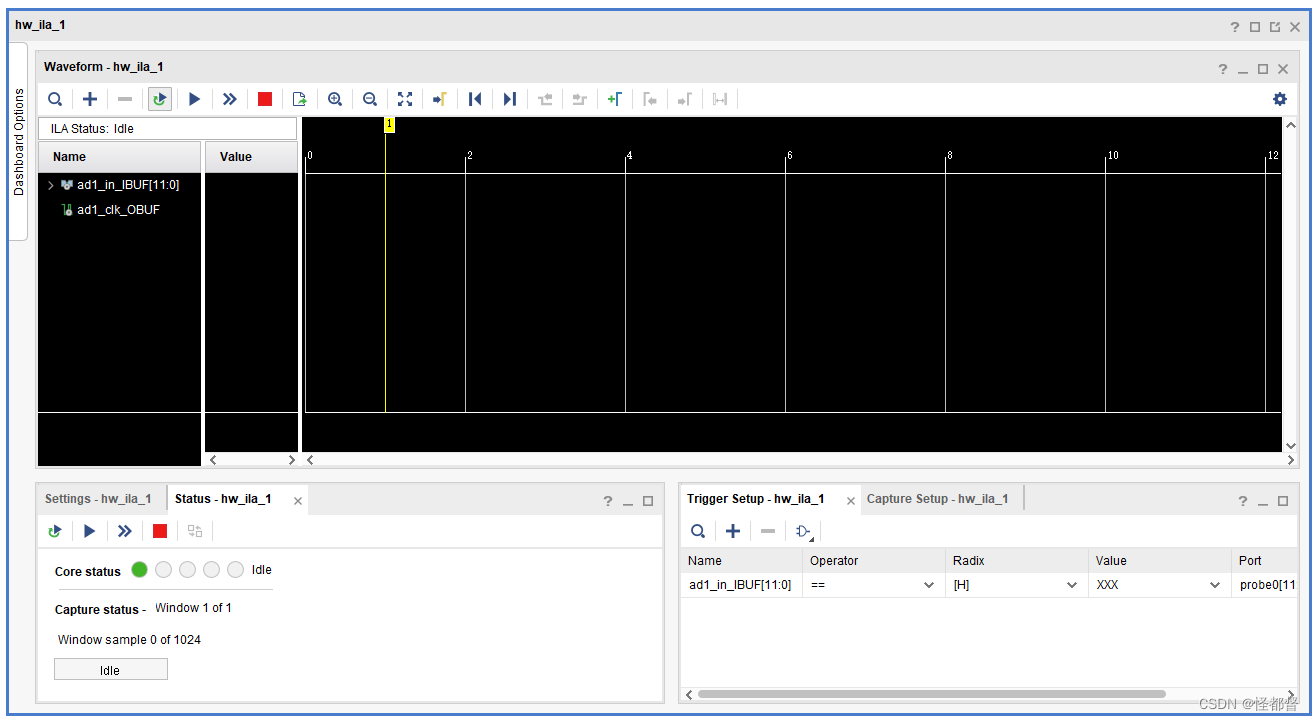

最后,点击Generate Bitstream 生成比特流,运行完成后,选择并进入Open Hardware Manager,下载到FPGA开发板。下载后完成会自动弹出以下窗口。

调试技巧

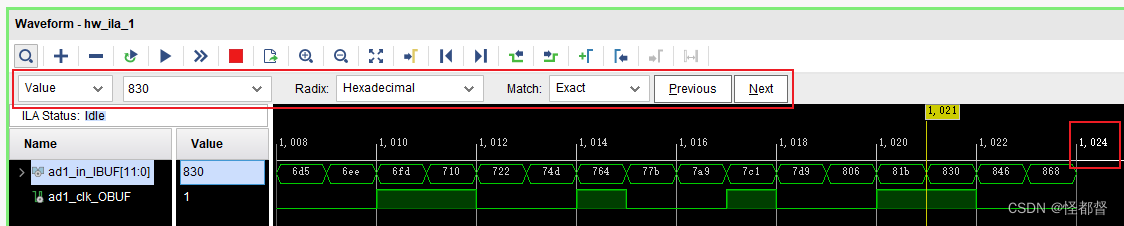

波形窗口支持查找功能,比如选择查找Value,为830,并设置进制为Hex十六进制,点击Previous或Next即可定位到如图中的第1022个数据0x830。从数据的总长度为1024,可以得知之前设置的Sample Data Depth的含义。

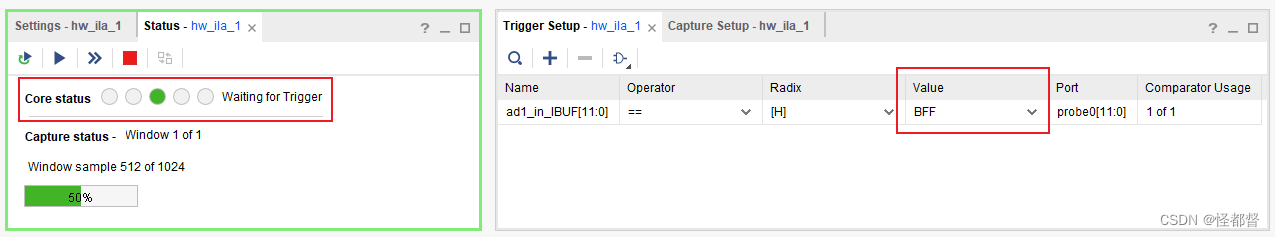

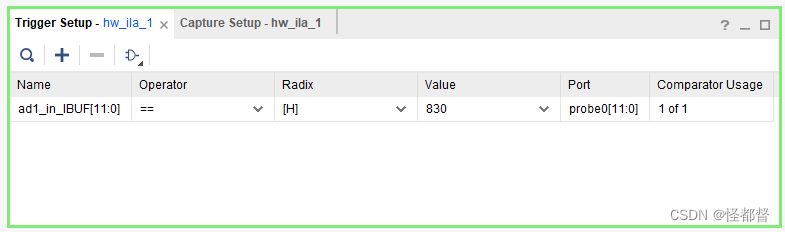

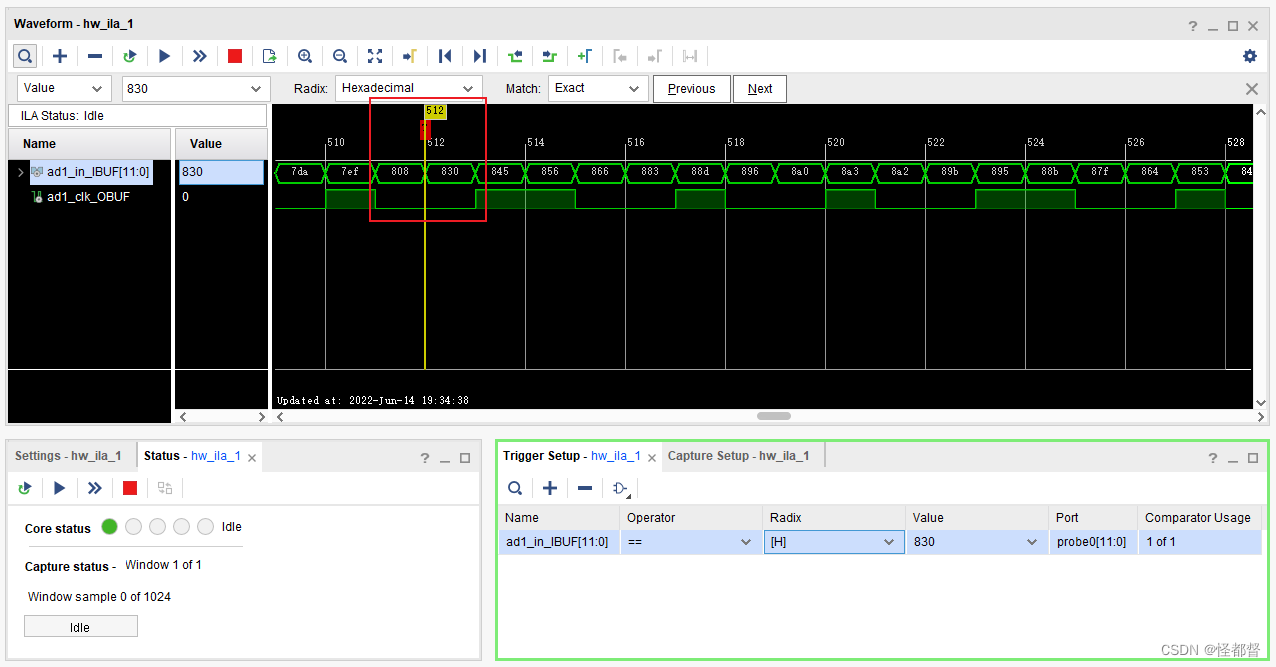

在Trigger Setup 触发设置中也可以实现查找特定数据的功能。首先点击+号,添加一个探针端口,并设置Operator(可选==、!=、<、<=、>、>=),再设置Radix基数和Value值,重新运行即可。

运行结果如下图,可以看到在512位置处有红色触发标志。

下图中左边窗口为Status 状态窗口。比如,设置触发数据值为0xBFF,因为输入信号幅值的限制,同时也因为采样深度的问题,ADC的结果不会出现0xBFF,则左侧窗口Core Status显示为Waiting for Trigger 等待触发。