- 1BUG:docker启动之后直接退出问题

- 2华为OD机试 - 找到它(JavaScript) | 机试题+算法思路+考点+代码解析 【2023】_华为od机考javascript输入

- 3最新最全的前端面试题集锦之 Vue 全家桶篇(从基础到高级,最新最全最详细解答)_vue全家桶面试题

- 4CrossOver (Mac安装Windows应用) v23.7中文激活版2024最新图文安装教程_crossover 23.7.0序列号

- 5Python蓝桥杯练习15——龟兔赛跑预测_话说这个世界上有各种各样的兔子和乌龟,但是研究发现,所有的兔子和乌龟都有一个共

- 6ACM题解——贪心——卫星安装_贪心算法与卫星结合

- 7Linux 磁盘空间占用率100%的排查

- 8Spring Boot 整合 Redis 使用教程

- 9【 C++入门 】引用_c语言中函数里的变量加引用类型,那么调用该函数时还需加引用类型吗

- 10【pycharm环境搭建(python脚本编辑器)】

计算机体系结构之CPU的构建和性能优化(个人学习)

赞

踩

引言

计算机体系结构是计算机科学中一门关键的领域,而其中的中央处理单元(CPU)更是整个计算机系统的心脏。CPU的构建与性能优化直接影响着计算机的运算速度和效能。随着科技的不断进步,CPU设计也在不断演进,从简单的单核结构到复杂的多核和并行计算,再到涉及超标量、超流水线等高级技术。本文将深入研究CPU的基本结构、指令集架构、流水线技术、多核设计、内存层次结构、性能优化等方面,旨在帮助读者更好地理解和应用计算机体系结构中关键的CPU组件,并思考未来的发展方向。让我们一同探索CPU的奥秘,了解如何构建高性能的计算机处理器。

CPU的基本结构

CPU(Central Processing Unit)是计算机系统中的核心组件,负责执行指令、进行运算和控制其他硬件设备的操作。其基本结构复杂而精密,由多个关键组件协同工作,以实现高效的计算和处理任务。以下是对CPU基本结构的详细介绍。

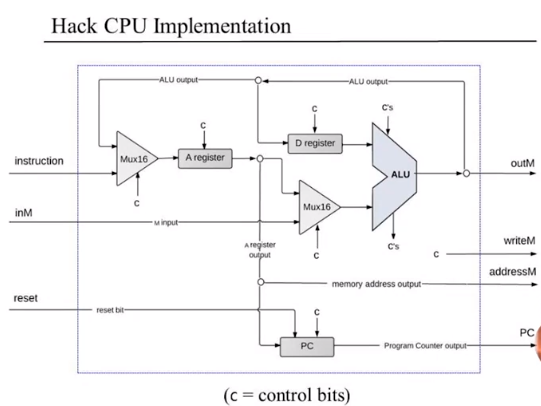

1. 控制单元(Control Unit)

控制单元是CPU的一个关键组件,负责协调和控制整个计算机系统的运行。它通过解释和执行存储在内存中的指令,确保正确的数据流向正确的位置,并且按照正确的顺序执行。控制单元通过时钟信号来同步各个部件的操作,确保计算机系统的协同运作。

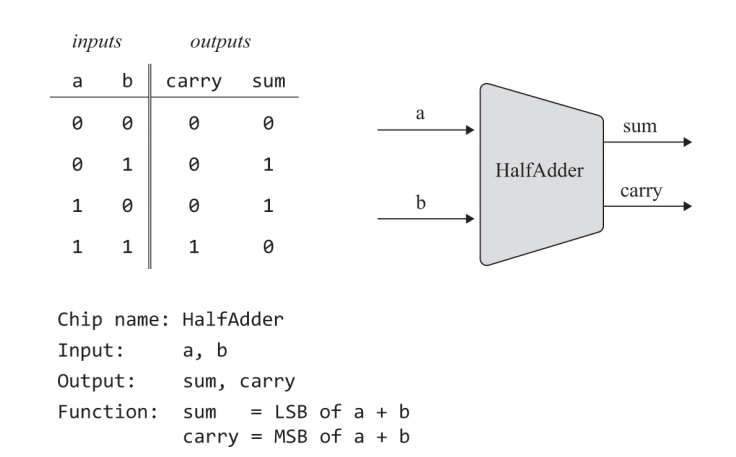

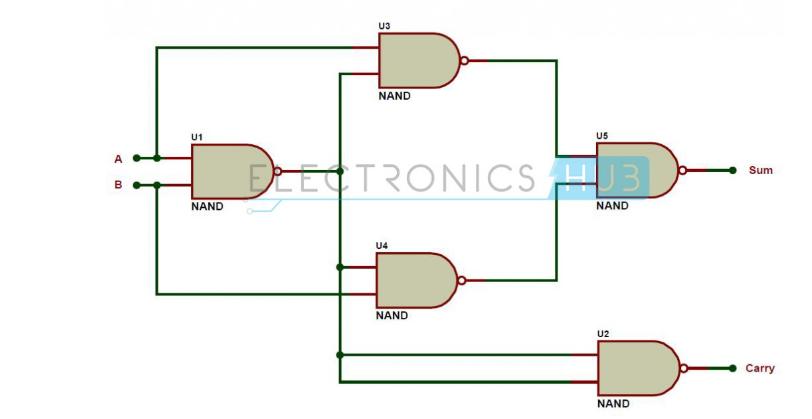

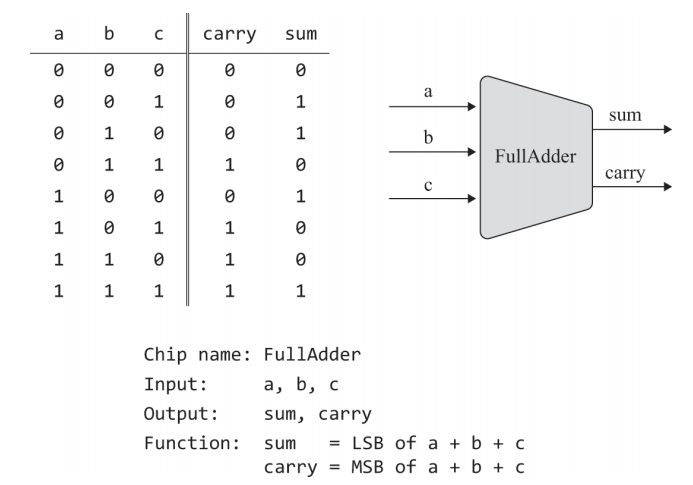

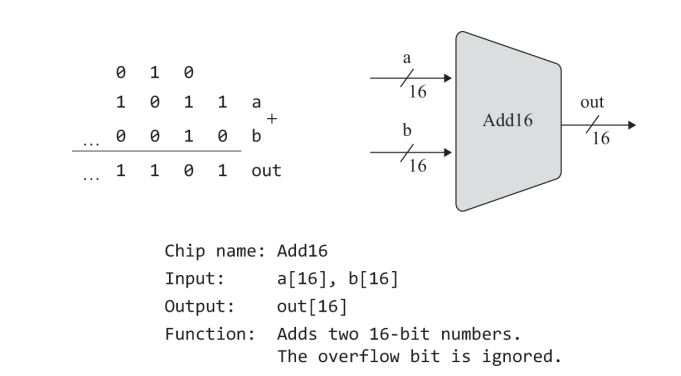

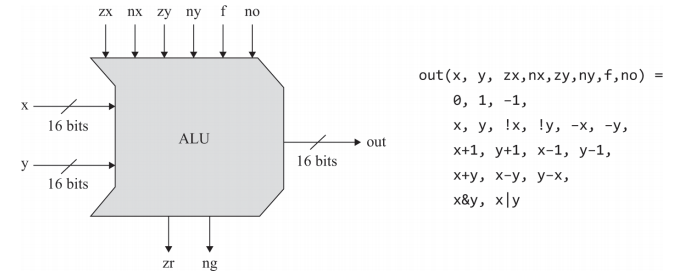

2. 算术逻辑单元(Arithmetic Logic Unit,ALU)

构造”ALU”

ALU是负责执行算术和逻辑运算的部分,是CPU的计算引擎。它可以执行基本的算术运算,如加法、减法、乘法和除法,同时也能进行逻辑运算,如与、或、非等。ALU的设计直接影响CPU的运算能力和效率。

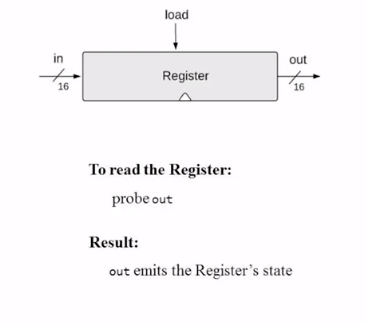

3. 寄存器文件(Register File)

寄存器是CPU内部的一种高速存储器,用于存储临时数据和中间结果。寄存器文件包含多个寄存器,每个寄存器可以存储一个数据单元。寄存器的高速访问速度使得CPU能够更快地存取和操作数据,提高计算速度。

4. 数据总线和地址总线

数据总线用于传输CPU和其他硬件组件之间的数据,而地址总线用于传输内存地址信息。数据总线决定了CPU能够一次传输的数据量,而地址总线决定了CPU能够寻址的内存空间大小。这两者共同构成了CPU与其他硬件设备通信的基础。

5. 控制总线

控制总线用于传输控制信号,包括时钟信号、读/写信号和中断请求等。时钟信号同步了整个计算机系统的操作,读/写信号用于指示数据的传输方向,中断请求则是外部设备请求CPU注意的信号。

6. 缓存存储器(Cache Memory)

缓存存储器是一种高速的临时存储器,用于暂时存放频繁访问的数据和指令。CPU通过缓存存储器加快数据的访问速度,减少对主存的访问次数,提高整体性能。缓存分为多级,包括一级缓存(L1 Cache)、二级缓存(L2 Cache)等。

7. 指令寄存器(Instruction Register)

指令寄存器存储当前正在执行的指令,控制单元从中提取指令的操作码,然后执行相应的操作。指令寄存器的作用是保持 CPU 正在执行的指令,以确保整个指令周期内的正确操作。

8. 时钟与时钟频率

时钟是CPU内部的计时器,用于同步各个部件的工作。时钟频率表示每秒时钟发生的脉冲次数,它直接影响到CPU的运行速度。时钟频率越高,CPU每秒能够执行的指令数就越多,整体性能也就越强大。

9. 运算器(Arithmetic Unit)

运算器是CPU中的一个子部件,主要用于执行各种算术和逻辑运算。它与ALU有一定的关联,但运算器更加综合,包括一些特定的运算和处理单元,用于执行特定的操作,如浮点运算单元(FPU)等。

综上所述,CPU的基本结构包括控制单元、算术逻辑单元、寄存器文件、数据总线、地址总线、控制总线、缓存存储器、指令寄存器、时钟与时钟频率、运算器等多个组件。这些组件协同工作,通过时钟信号的同步,实现高效的指令执行和数据处理,为计算机系统提供强大的计算能力。

缓存局部性(Cache Locality)

在CPU的基本结构中,缓存存储器起着至关重要的作用,而缓存局部性是其性能优化的关键概念之一。缓存局部性指的是在程序执行过程中,对于特定数据的访问往往集中在某个相对较小的区域,这种情况有助于提高缓存的命中率。

缓存局部性的概念与索引的设计密切相关,索引是一种数据结构,用于加速数据的检索。在计算机系统中,特别是在缓存设计中,合理的索引结构有助于提高缓存的效率。

-

索引的作用:

-

快速定位数据:索引允许系统直接跳转到特定位置,而不必逐个查找,从而加速数据的访问。

-

减少访问时间:通过索引,可以更有效地利用缓存,减少对主存的访问时间。

-

-

缓存局部性与索引设计:

-

空间局部性:合理的索引设计可以使相邻的数据项存储在相邻的内存位置上,充分利用空间局部性,提高缓存的命中率。

-

时间局部性:通过索引,经常被查询的数据项可以被快速定位,提高时间局部性,减少缓存未命中。

-

-

多级缓存和索引的关系:

-

索引层次结构:多级缓存中,每个缓存级别的设计需要考虑到索引的层次结构,以优化数据的检索路径。

-

缓存关联性:索引的设计也关乎缓存关联性,即不同索引之间的数据项的关联程度,影响着缓存的协同工作效果。

-

综合而言,缓存局部性的优化需要与索引的设计相协同。巧妙的索引结构可以更好地利用缓存局部性,提高缓存性能,进而加速整体系统的数据处理速度。

缓存局部性例子:

import time

import random

import numpy as np

import timeit

# 创建一个大型的二维数组

size = 3000

twoDarray = np.random.rand(size, size)

# 对行求和

def sum_rows():

return np.sum(twoDarray, axis=1)

# 对列求和

def sum_columns():

return np.sum(twoDarray, axis=0)

#测量执行时间

rows_time = timeit.timeit(sum_rows, number=size)

columns_time = timeit.timeit(sum_columns, number=size)

print(f"列求和时间:{columns_time}")

print(f"行求和时间:{rows_time}")

DFF和MUX(NAND)构成;有记忆功能。 由寄存器构成,多个寄存器构成一个缓存,由多个缓存再构成一个较大的缓存。 内存越大就意味着查询的次数越多;

重点:充分的利用缓存的局部性,写程序的时候要注意利用好缓存。

上述代码实验数据:

| 数组长度 | 列求和时间 | 行求和时间 | 单位s |

| 100 | 0.00045 | 0.00053 | |

| 1000 | 0.3898 | 0.7368 | |

| 2000 | 3.8985 | 7.7411 | |

| 2500 | 8.9922 | 16.0995 | |

| 3000 | 16.1789 | 30.2309 | |

| 3500 | 26.8152 | 49.9134 |

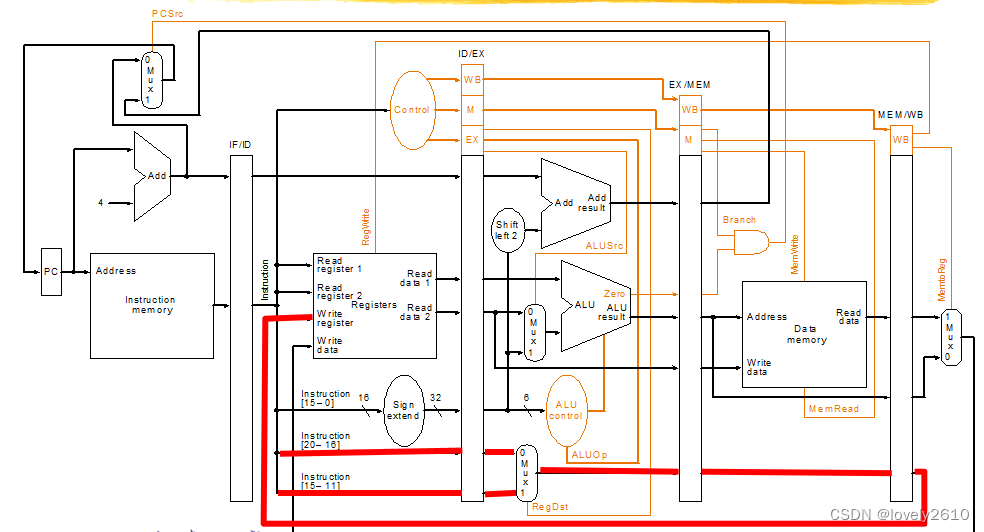

流水线技术(Pipeline Architecture)

流水线技术是一种通过将处理过程分解成多个阶段,并在同一时刻执行多个指令的方式来提高CPU性能的设计思想。这种架构使得处理器能够同时处理多个指令,从而加速整体指令执行的速度。

-

流水线的基本原理:

-

划分阶段(Pipeline Stages):处理过程被划分为若干个阶段,每个阶段执行特定的任务。常见的阶段包括指令获取、解码、执行、访存和写回。

-

并行执行(Parallel Execution):每个阶段都可以同时执行不同指令的相应任务,使得多个指令在不同阶段同时执行,从而提高整体效率。

-

流水线寄存器(Pipeline Registers):相邻阶段之间使用流水线寄存器传递数据,确保各阶段之间的数据传递和同步。

-

-

流水线的优点:

-

提高吞吐量:多个指令在同一时刻在不同阶段执行,从而提高了整体指令执行的吞吐量。

-

降低时钟周期:每个阶段的处理时间相对较短,可以使用较高的时钟频率,降低时钟周期,进一步提高性能。

-

资源重用:在流水线中,各个阶段可以同时执行不同指令,有效地利用了处理器的资源,提高了资源利用率。

-

-

挑战和解决方案:

-

数据冒险(Data Hazards):由于数据相关性可能导致某些指令需要等待之前的指令完成。采用数据前推技术或者乱序执行等方法来解决。

-

控制冒险(Control Hazards):由于分支指令的存在可能导致流水线中的指令需要被清空。采用分支预测技术和延迟槽等方法来解决。

-

-

超标量和超流水线设计:

-

超标量设计:在同一时钟周期内发射多个指令,通过多个独立的流水线来实现。

-

超流水线设计:进一步增加流水线的阶段数,提高流水线的细粒度,以进一步提高指令执行速度。

-

流水线技术的应用成为现代CPU设计中的标配,然而,随着流水线阶段的增加,也带来了一些挑战,如冒险问题的复杂性增加。因此,细致的设计和有效的冒险处理是流水线技术成功应用的关键。

流水线实验-RISC:

精简指令系统(Reduced instruction set computer),代表MIPS(寄存器是32个)和ARM。一般是用于手机。

流水线(piple line)可以降低等待的时间。

依赖:

for ...

sum1 = sum1 + a[i]

sum2 = sum2 + a[i+1]

#对奇数和偶数分别的进行相加,进行两次求和。

代码测试:

def my_dot(a, b):

"""

Compute the dot product of two vectors

Args:

a (ndarray (n,)): input vector

b (ndarray (n,)): input vector with same dimension as a

Returns:

x (scalar):

"""

x = 0

for i in range(a.shape[0]):

x = x + a[i] * b[i]

return x

np.random.seed(1)

a = np.random.rand(10000000) # very large arrays

b = np.random.rand(10000000)

tic = time.time() # capture start time

c = np.dot(a, b)

toc = time.time() # capture end time

#

print(f"np.dot(a, b) = {c:.4f}")

print(f"Vectorized version duration: {1000*(toc-tic):.4f} ms ")

#

tic = time.time() # capture start time

c = my_dot(a,b)

toc = time.time() # capture end time

#

print(f"my_dot(a, b) = {c:.4f}")

print(f"loop version duration: {1000*(toc-tic):.4f} ms ")

#print(twoDarry)

上述代码实验数据:

| 数组长度 | dot | numpy dot | 单位ms |

| 10000000 | 1978.3556 | 5.4953 | |

| 15000000 | 2965.5726 | 6.5694 | |

| 20000000 | 4029.1204 | 7.2656 | |

| 25000000 | 5082.9103 | 9.1541 | |

| 30000000 | 5987.6609 | 9.5503 | |

| 35000000 | 8314.2519 | 13.1459 |

结语

在未来发展方向上,随着量子计算和神经网络处理等新技术的涌现,CPU设计将面临更为复杂的挑战。这些新技术的引入将为计算机体系结构带来颠覆性的变革,推动CPU设计朝着更高性能、更低能耗的方向发展。量子计算的引入可能重新定义计算机的计算模型,而神经网络处理则将在处理复杂模式识别等任务上展现出巨大的优势。

总的来说,对计算机体系结构和CPU构建的深入理解不仅有助于优化当前系统的性能,还为未来技术的发展奠定了基础。通过持续不断地研究和创新,我们将能够迎接未来计算需求的挑战,推动计算机技术迈向新的高度。