热门标签

热门文章

- 1Win10自带输入法 切换到中文 无法输入中文_电脑切换中文输入法后打不出汉字

- 23、Redis底层原理(持久化+分布式锁)_redis 分布式锁 持久化依赖

- 3Java线程的两种实现方式(Rundable接口和lambda)_lamda 创建线程 java 传入参数

- 4java初识 | eclipse和jdk的下载与安装、环境变量的配置(win10)_win10 eclipse 环境变量

- 52021年上海值得去的66家规模互联网大厂公司全名&简称_上海任意门是大厂还是小厂

- 6大模型在金融行业中的应用

- 7python:随机验证码的生成_python generatecode

- 8计算机毕业设计springboot基于协同过滤算法的电影推荐系统2k9y69【附源码+数据库+部署+LW】_基于协同过滤算法spring boot毕业设计

- 9HarmonyOS开发实战探索:基于hvigor插件定制构建规范_hvigor-ohos-plugin

- 10SpringCloudAlibaba入门_spring cloud alibaba入门

当前位置: article > 正文

FPGA实现LVDS接口--OSERDESE2原语的使用_fpga中的源语lvds 的serdes的使用

作者:喵喵爱编程 | 2024-08-16 09:35:50

赞

踩

fpga中的源语lvds 的serdes的使用

目录

总目录点这里:《FPGA接口与协议》专栏的说明与导航

1、概述

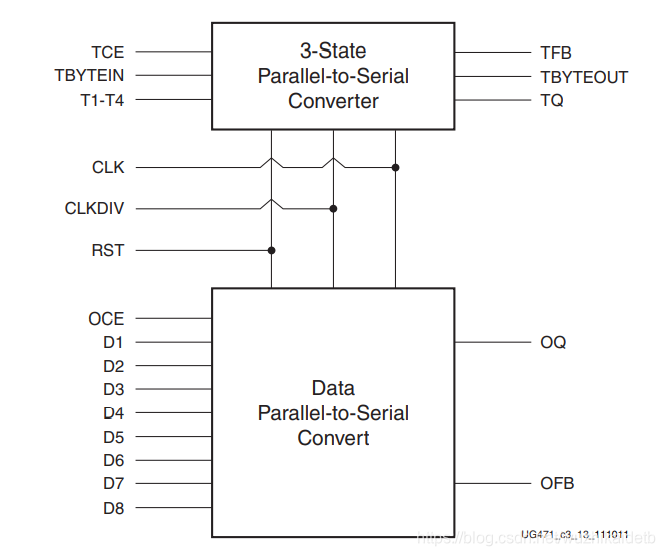

Xlinx的原语OSERDESE2是一种专用的并--串转换器,每个OSERDESE2原语都包括一个专用的串行化模块用于数据和3态控制,OSERDESE2可以工作在SDR和DDR模式。

OSERDESE2的位宽可以达到8:1(如果使用两个原语级联,则可以到10:1和14:1)。3态序列化最高可达14:1,有专用的DDR3模式可用于支持高速内存应用程序。

OSERDESE2的结构框图如下:

OSERDESE2 使用两个时钟 CLK 和 CLKDIV 进行数据速率转换。 CLK是高速串行时钟,CLKDIV是分频并行时钟。 CLK 和 CLKDIV 必须相位对齐。使用前,必须对 OSERDESE2 进行复位。 因为OSERDESE2 包含一个控制数据流的内部计数器,如果使用前不进行复位则有可能产生意外的输出。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/喵喵爱编程/article/detail/987607

推荐阅读

相关标签