- 1Qt开发笔记:Qt3D三维开发笔记(一):Qt3D三维开发基础概念介绍_使用qt做3维图形显示需要什么技术

- 2git push origin master失败报错“fatal: unable to access...“解决方法_git.exe push --set-upstream --progress "origin" ma

- 3LVGL移植到ARM开发板(GEC6818)_lvgl移植arm

- 4mysql查询包含某两个标签_如何查询同时包含多个指定标签的文章

- 5如何在WooCommerce中设置运费(免费功能)_woocommerce产品价格后添加运费

- 6java split()方法_java split方法

- 7贝锐蒲公英异地组网方案:实现制药设备远程监控、远程运维

- 8Linux系统的网络设置_linux 上网

- 9SCI期刊介绍—IEEE Open Journal of the Communications Society

- 10智慧农业新纪元:解锁新质生产力,加速产业数字化转型

超详细 quartus 新建工程 及 quartus 和 modelsim 联合仿真 以及 modelsim 的简易教程_quartus和modelsim

赞

踩

(开始用docx写的,复制进md文件,然后一张张图复制进去,结果导到csdn图片还是没有,,,只能一张张复制到csdn)

一、新建工程

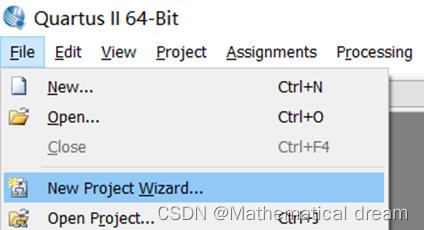

1. 新建工程

选择工程路径,填写工程名

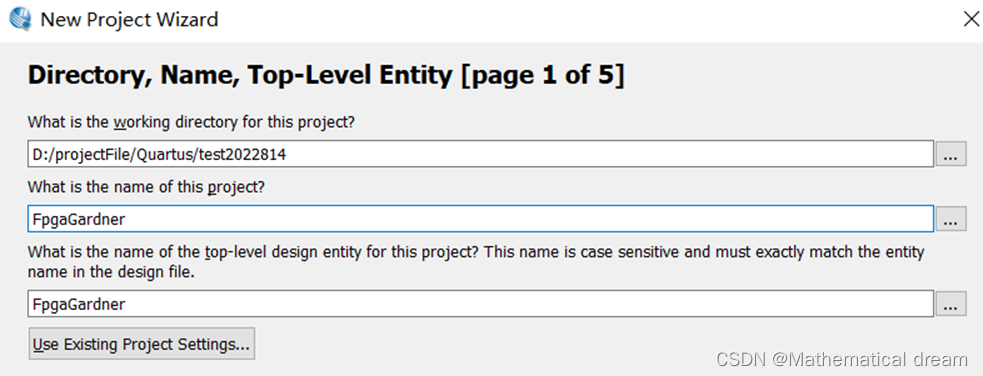

添加文件可以之后手动添加

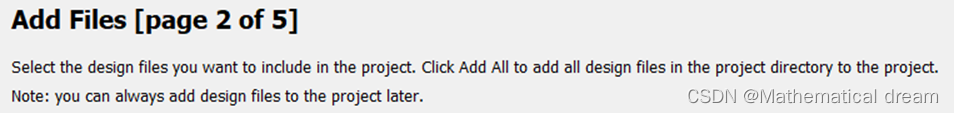

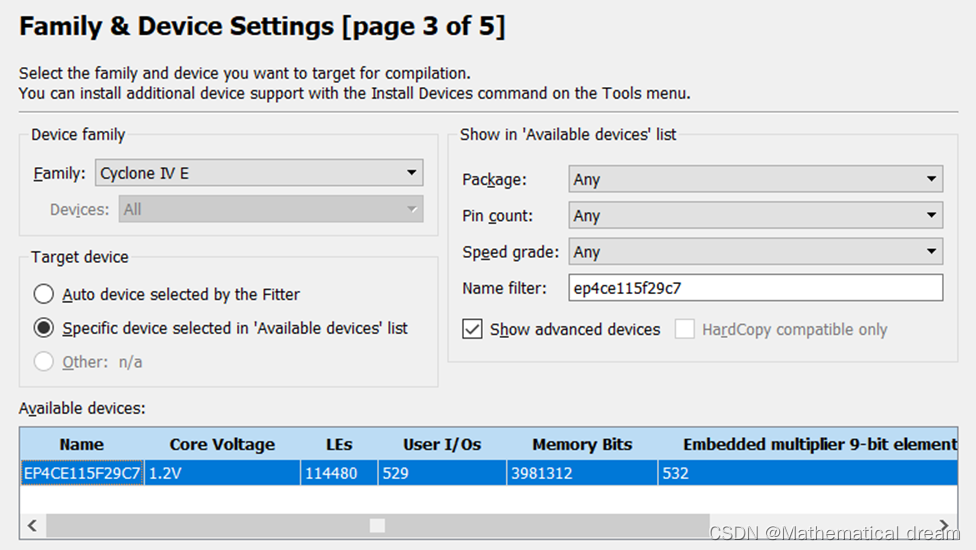

选板型

仿真工具选择

2. 添加源文件以及ip核并编译

添加代码文件

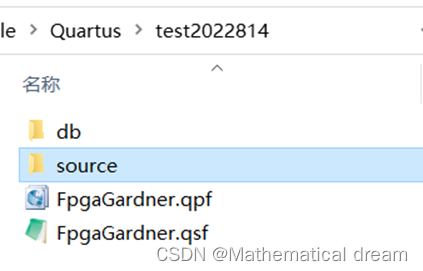

新建文件夹用来放源代码

其中主程序与工程名一致

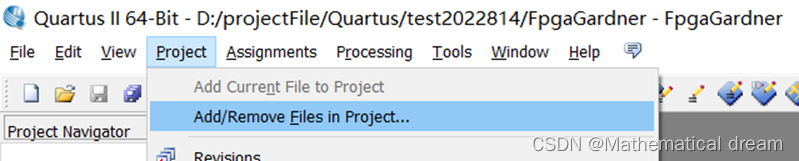

添加代码文件

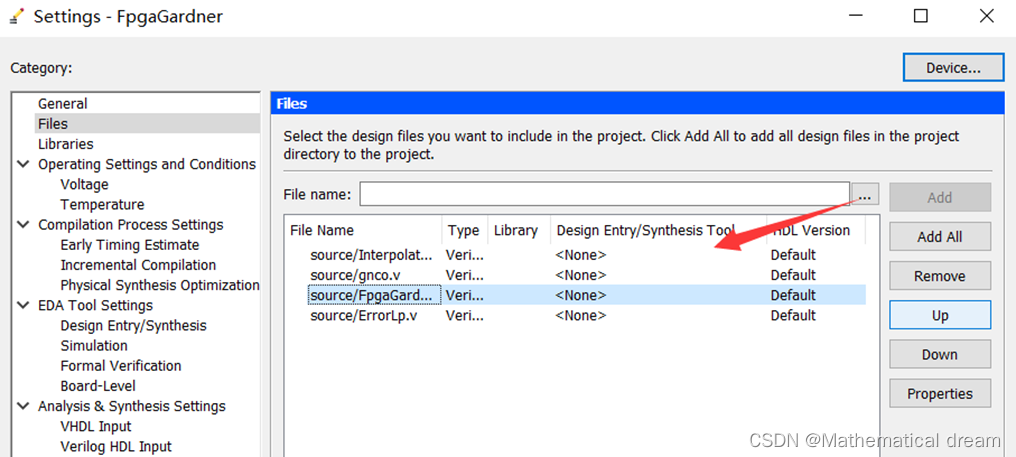

导入文件后可以调整文件顺序

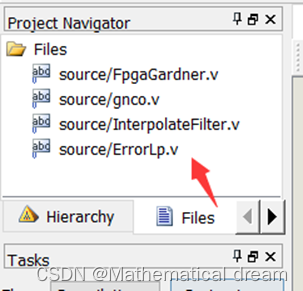

这样便是添加成功

添加IP核

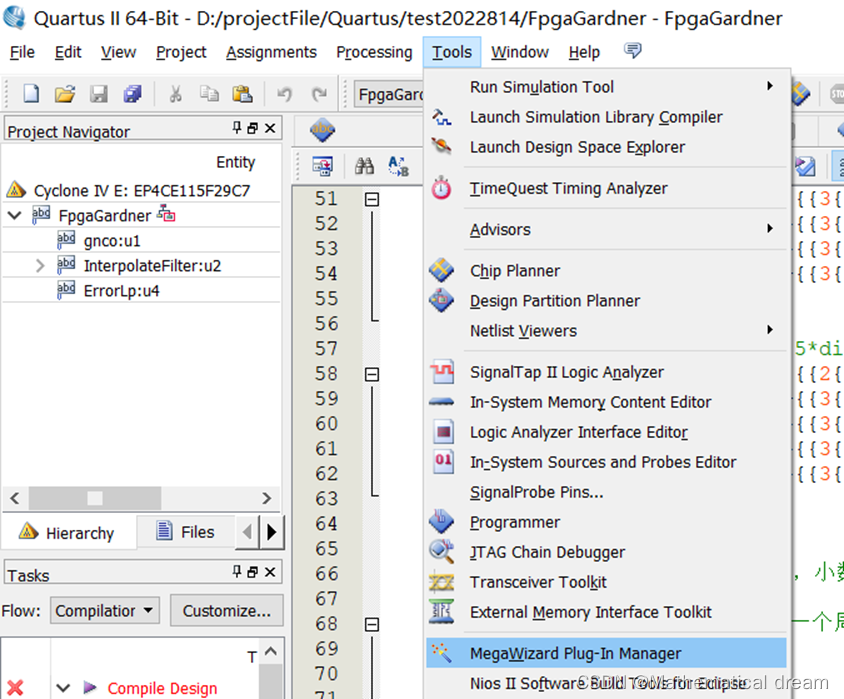

魔法棒添加IP核

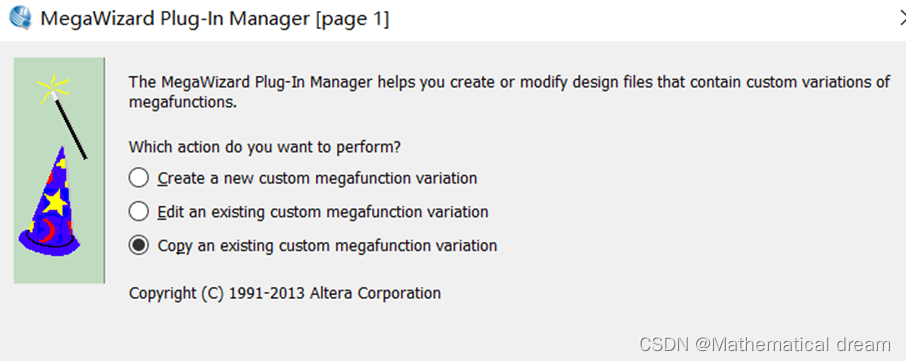

可以新建,这里选择复制

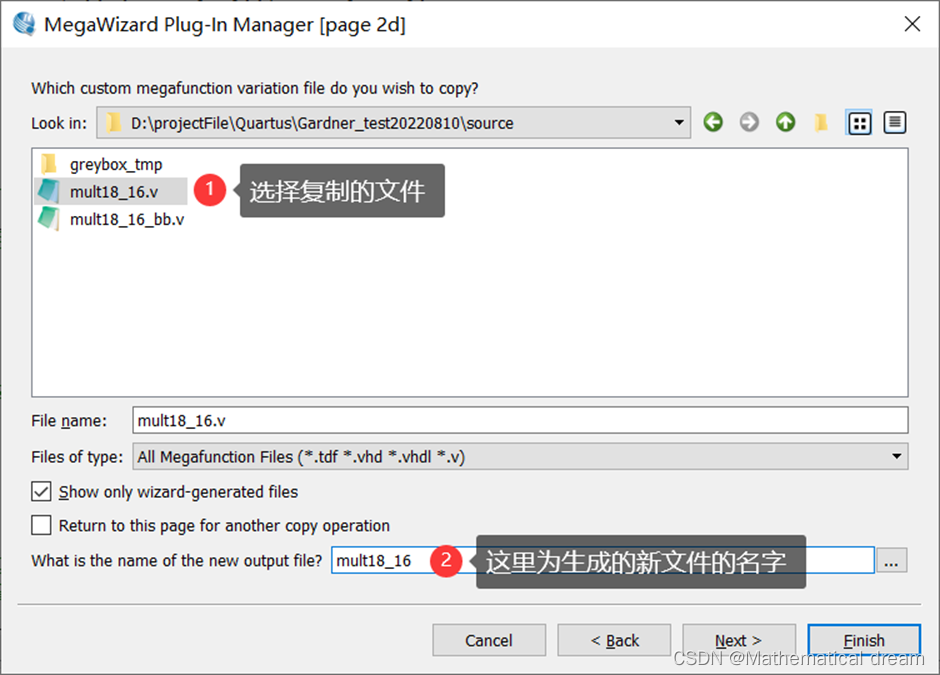

打开看了一下,输出文件此时的路径是” …\Quartus\test2022814\source\”,也可以把路径选全,新生成的文件这里和原来的文件名取了一样的

之后一直next即可

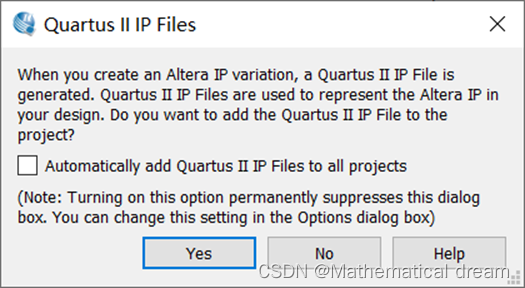

这里应该是yes

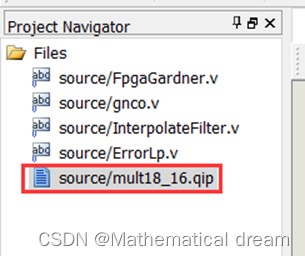

多了一个文件

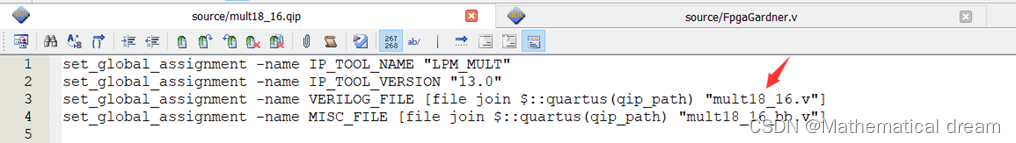

打开是这样

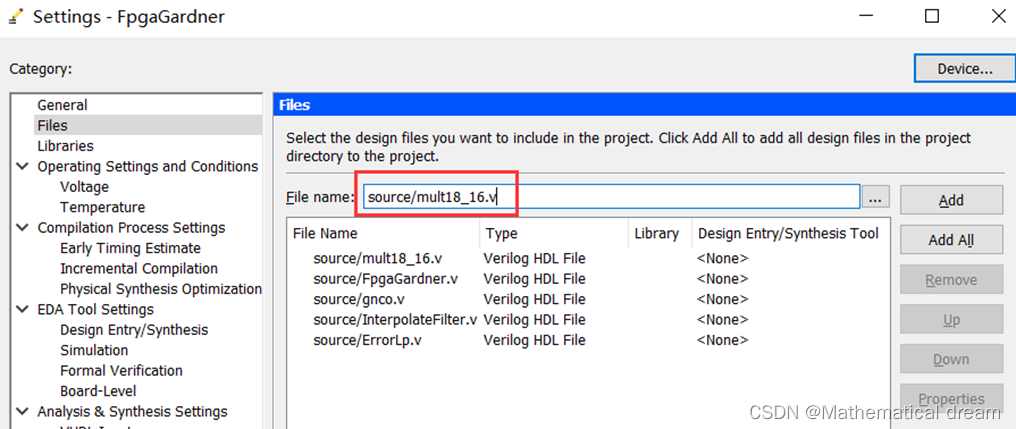

也可以把新生成的文件添加进来

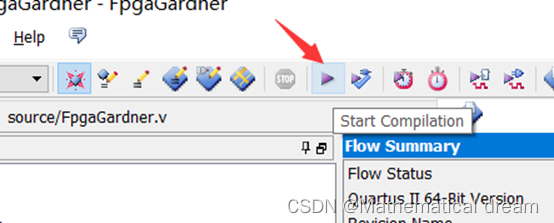

编译

编译之后的warning也要看一下,有时候有变量忘记赋值,或者将a bit的变量错误地赋给b bit的变量等等不会报错但可能不符合编程者预期的问题,都可能在这发现

3. 自动生成testbench文件并添加路径到工程中

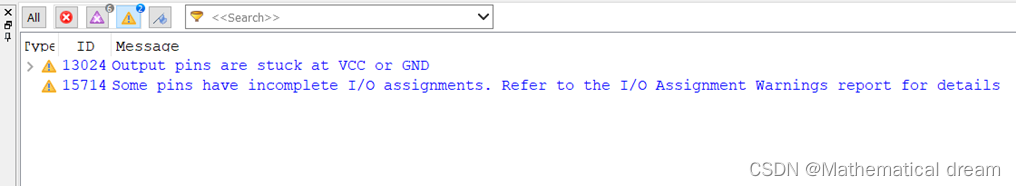

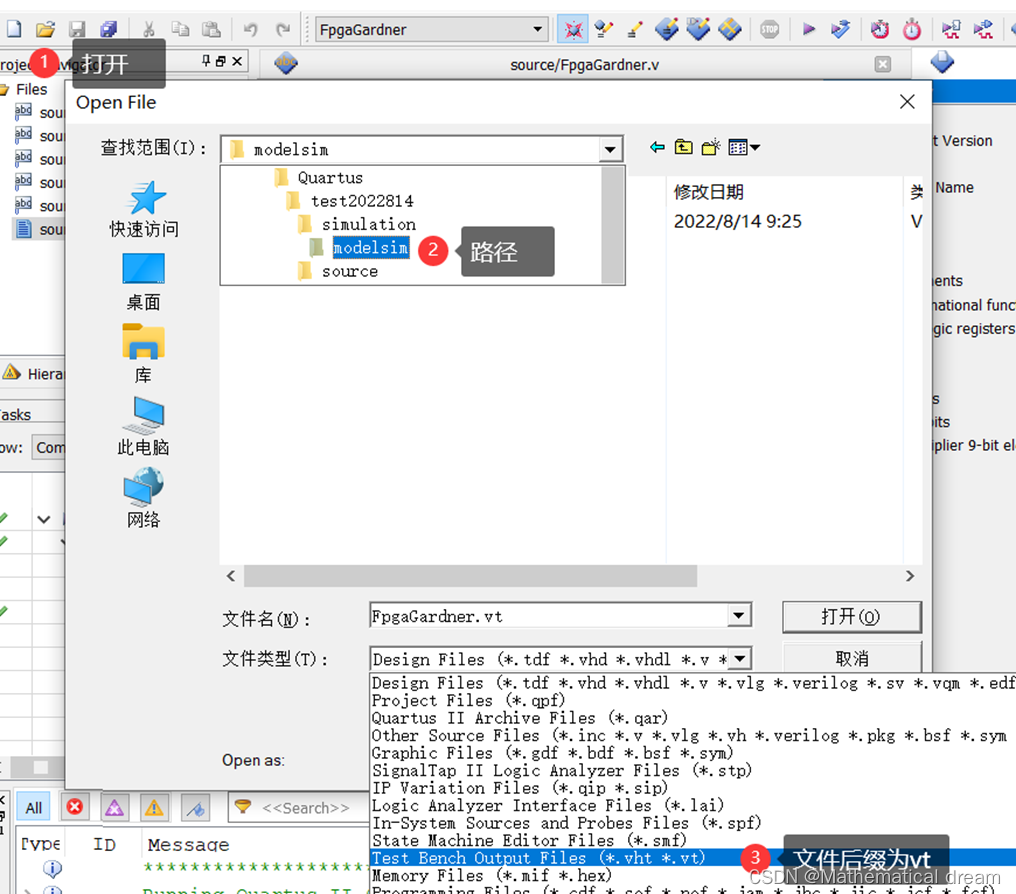

生成testbench文件

编译过后才可以生成testbench文件

可打开文件,方便后续修改

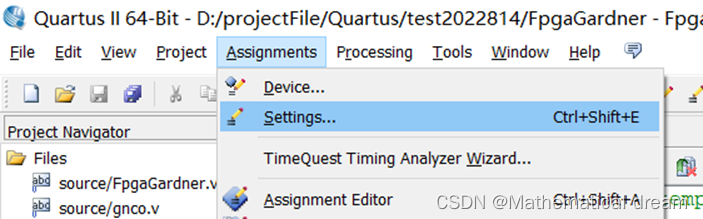

打开设置

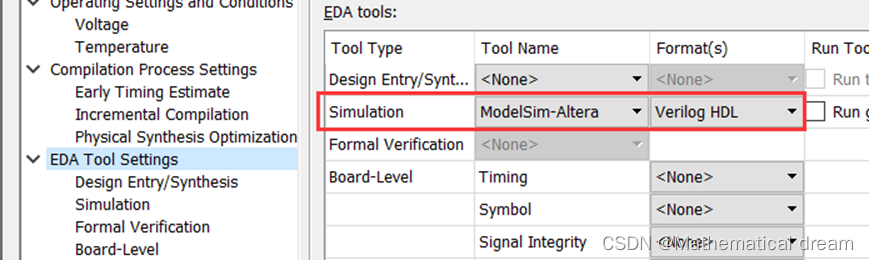

如果建工程时没注意的话,这里可以修改仿真工具

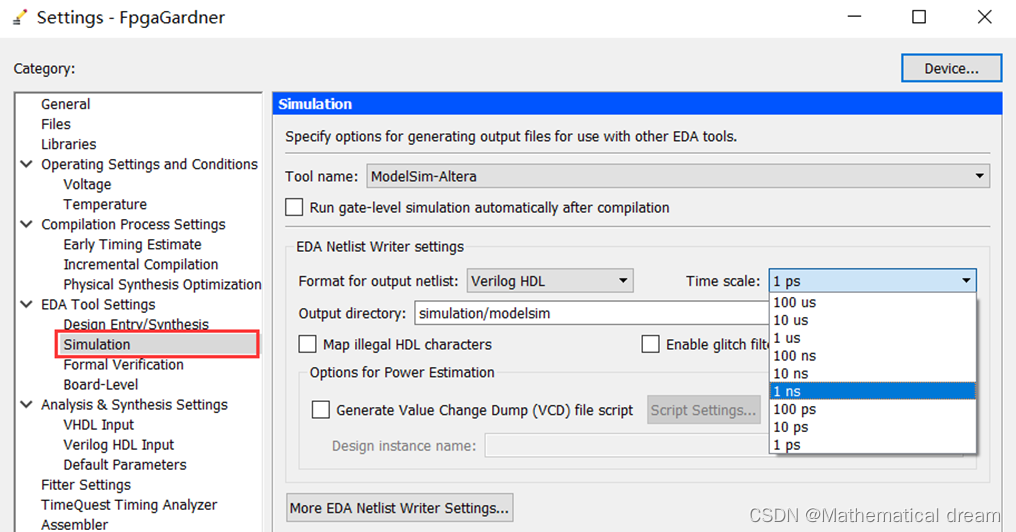

这里可以修改仿真时间单位

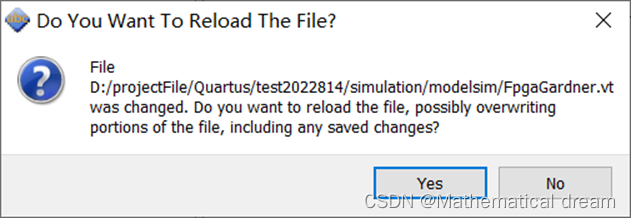

此时如果重新生成testbench文件的话,就会覆盖原来的文件,选择yes

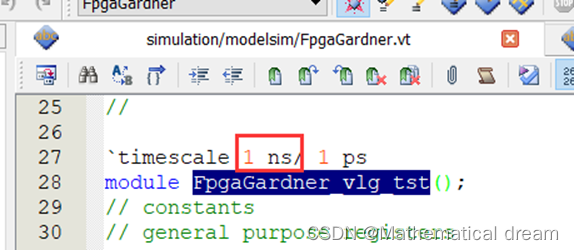

重新加载显示后看到1ps变成了1ns,先把testbench模块名复制一下

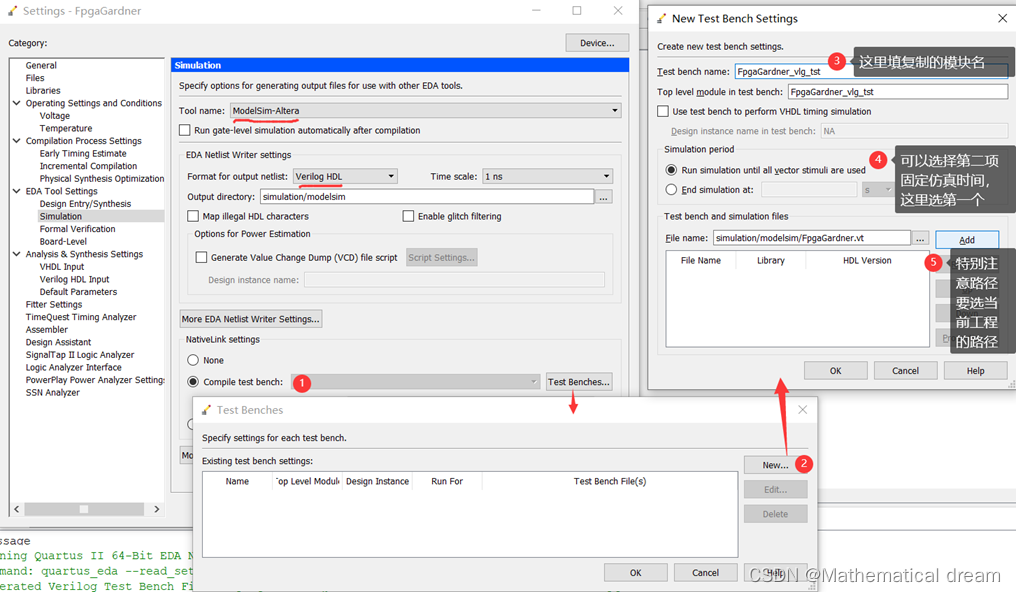

添加testbench路径

添加testbench文件

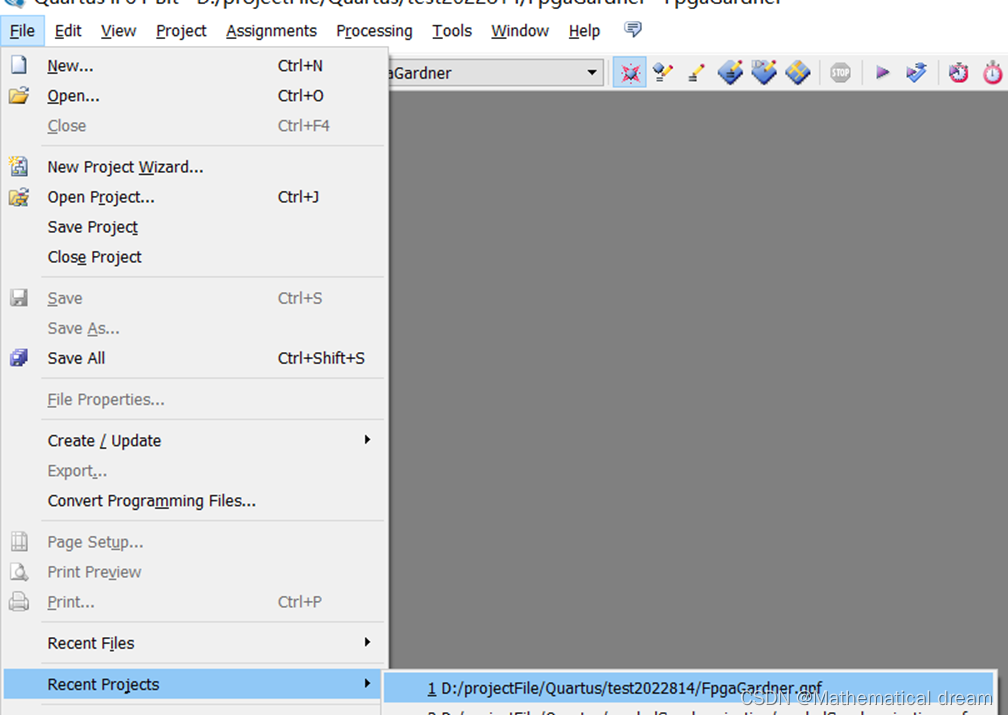

4. 再次打开工程

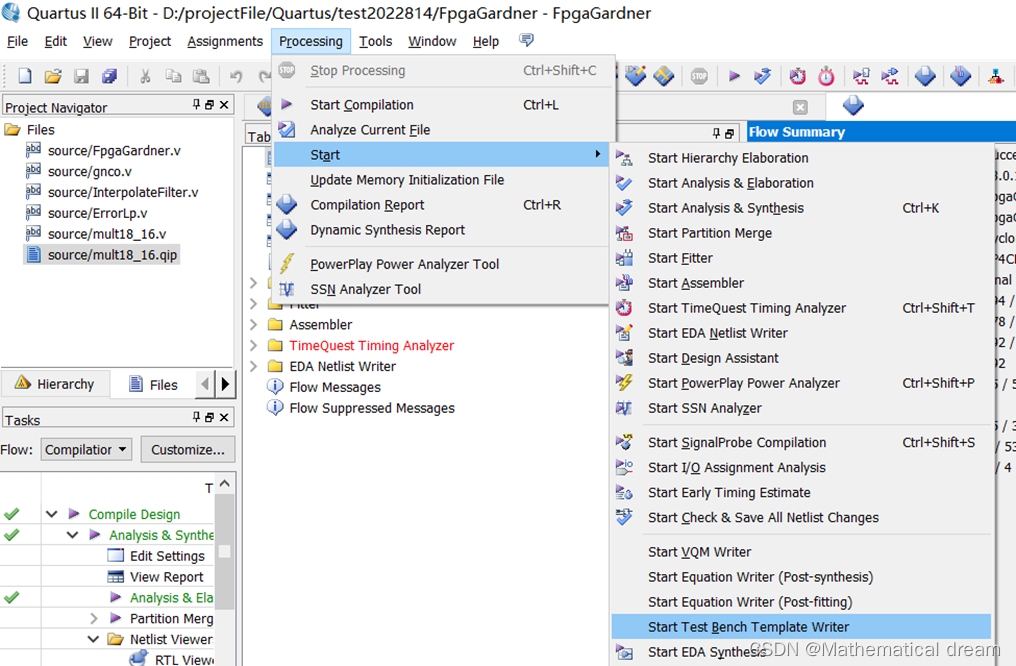

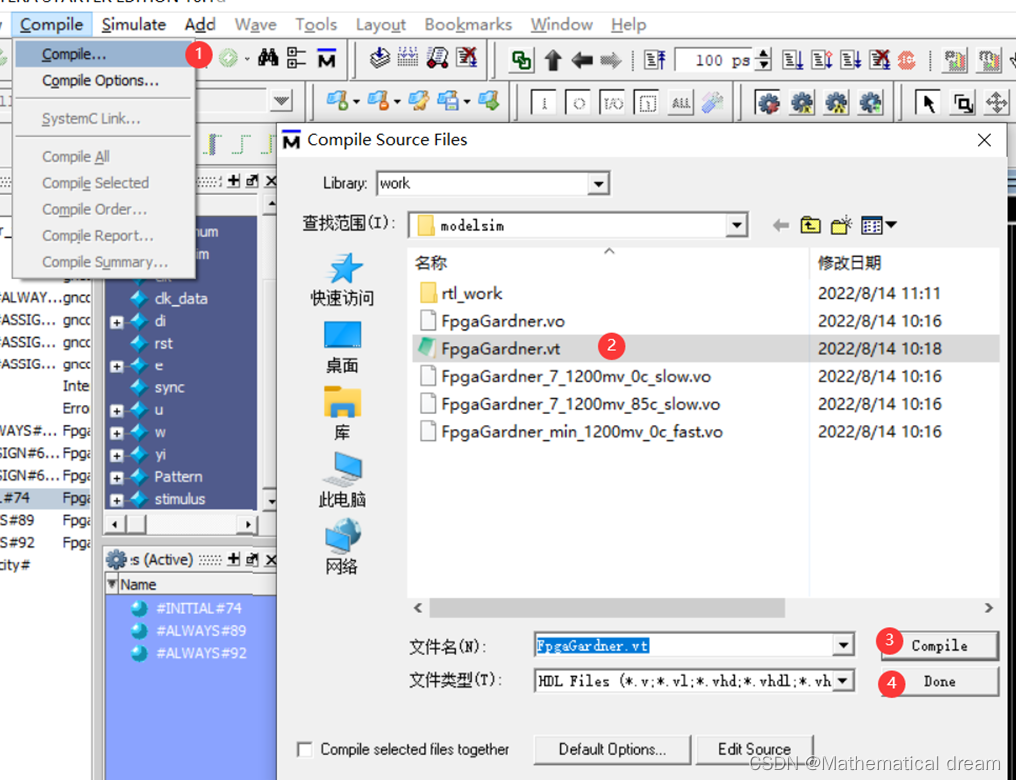

之后可以打开”\ simulation\modelsim\”路径下的testbench文件,注意文件类型要选vt

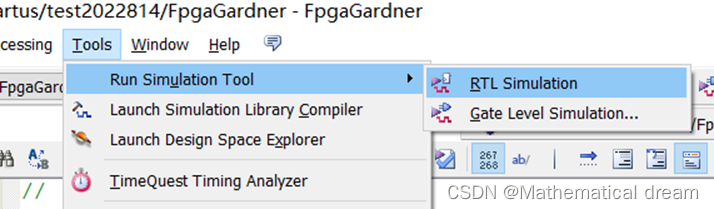

二、quartus和modelsim联合仿真

1. 联合流程

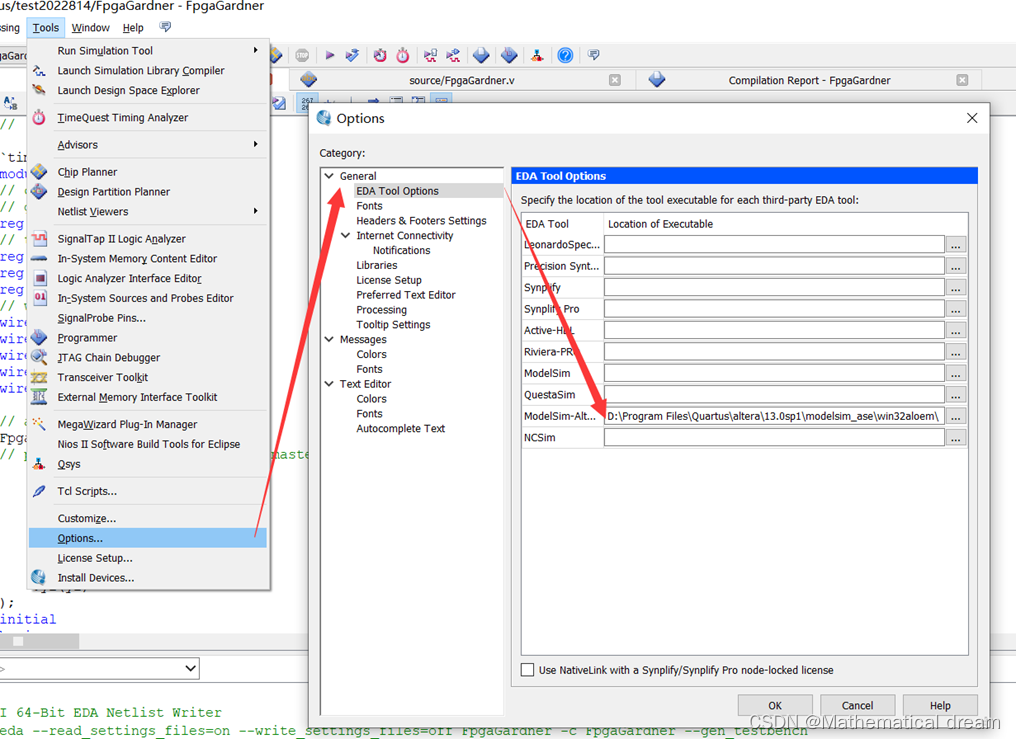

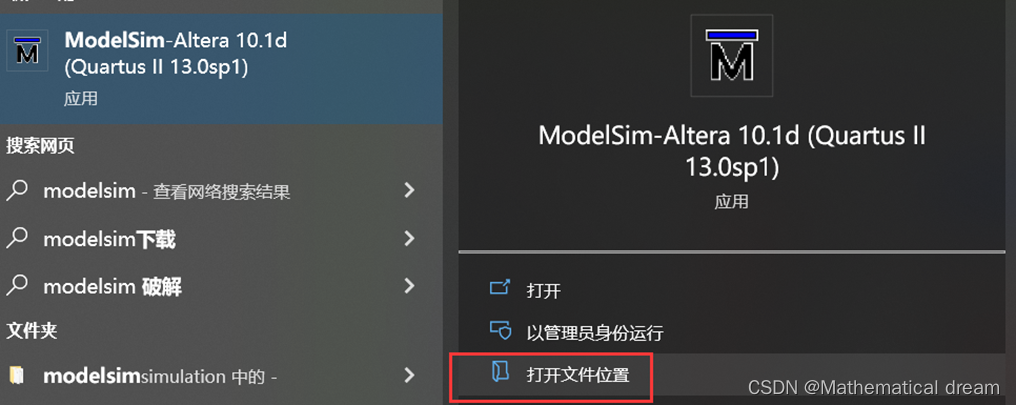

首先添加modelsim的路径

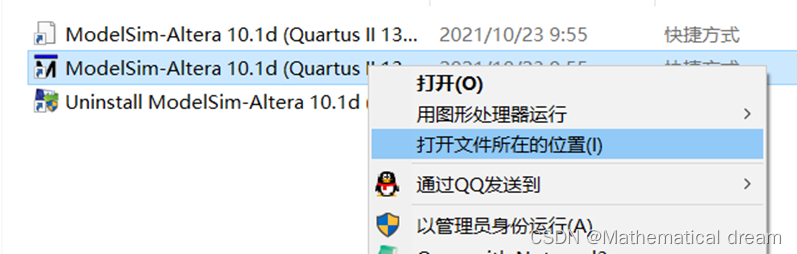

路径可以这样获得

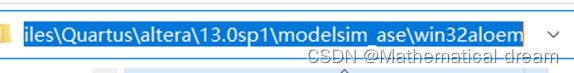

网上说后面要加”\”,就是” …\Quartus\altera\13.0sp1\modelsim_ase\win32aloem\”

路径添加好后,之后就不用管了

不用联合仿真,直接用modelsim仿的话,好像生成的那个mult18_16.v调用就会报错,因为无法链接到它所用到的其他库

应该也可以把它直接或间接用到的库都复制过来,运行也没有报错,这种方法的直接modelsim仿真就没试过了

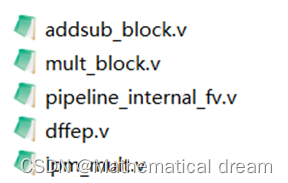

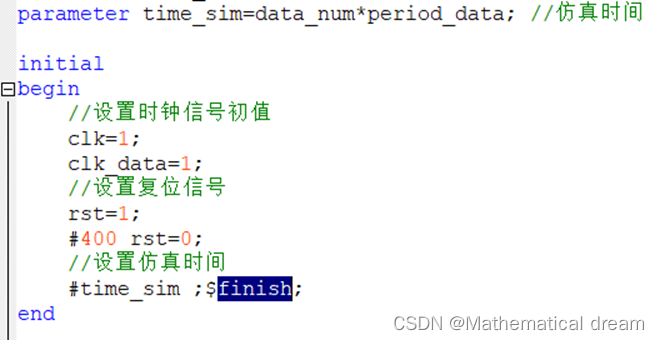

生成的testbench里这几句不知道干嘛的,应该可以删去

写好testbench之后就能联合仿真了。

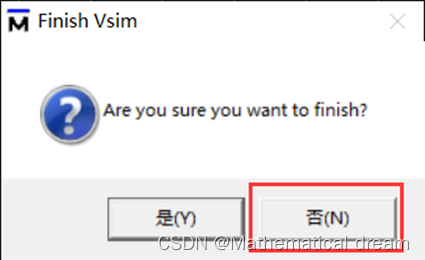

因为testbench中”$finish”语句,仿真时会出现对话框,选”否”,否则会直接退出

这么做的好处是波形会只仿真到”$finish”语句

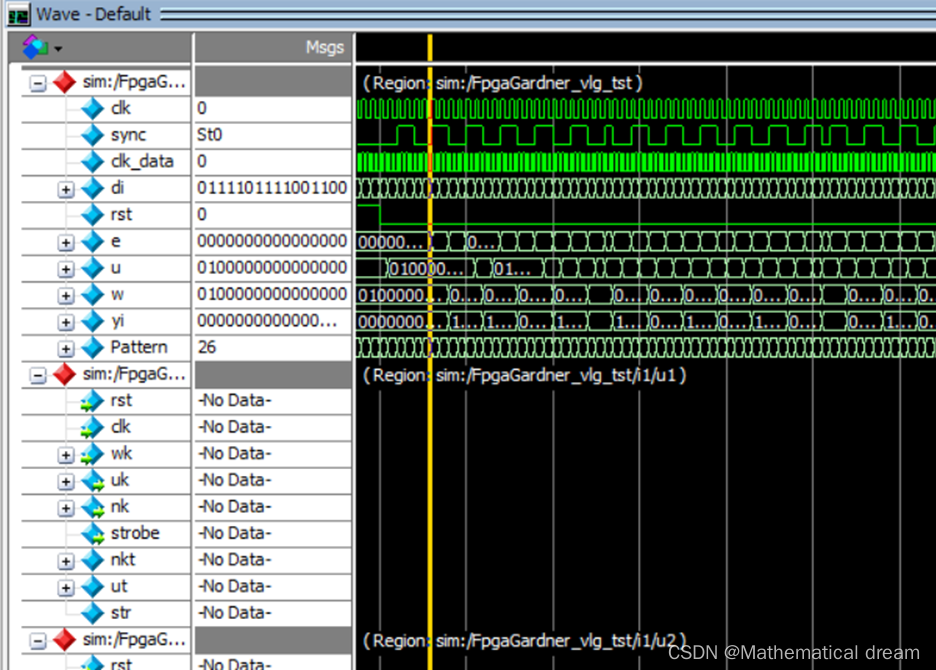

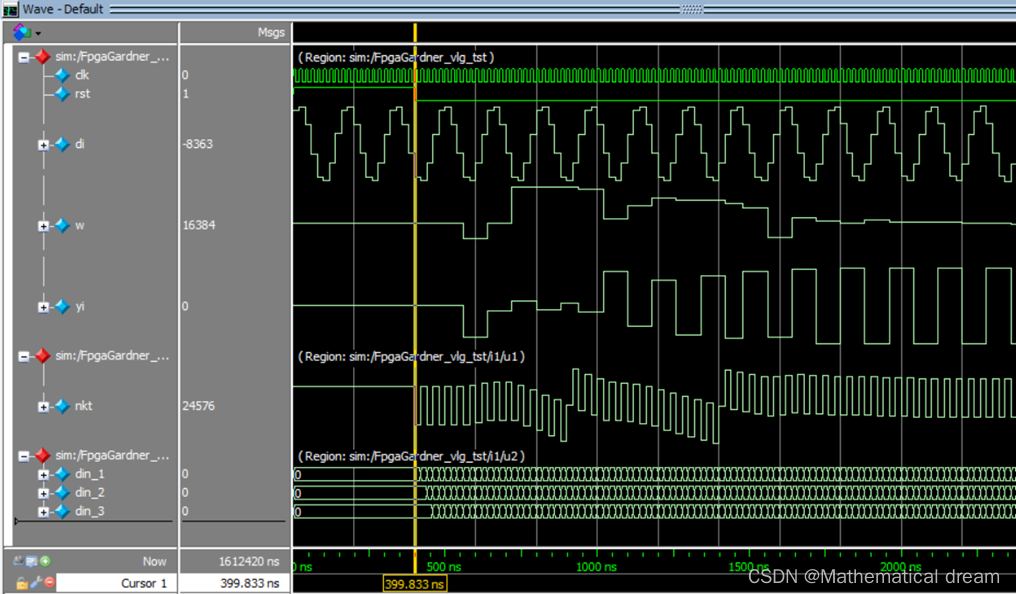

之后就能看到波形了

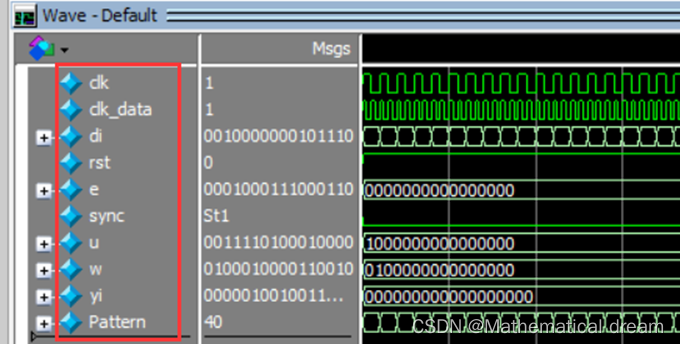

2. 波形查看

基本上modelsim界面每个操作都会在下面命令行用命令实现,可以按”↑”键查看

添加新的变量

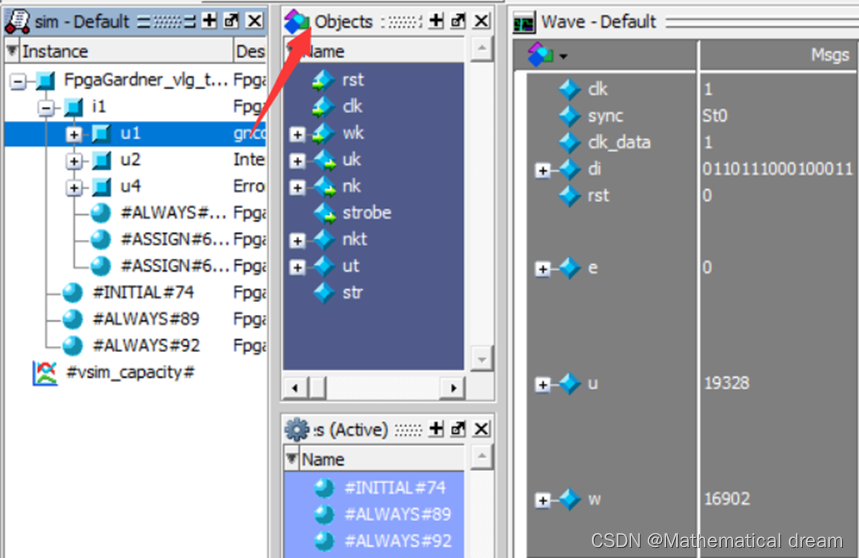

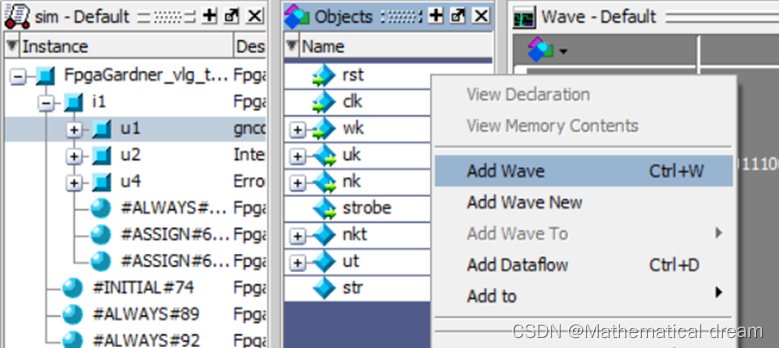

默认是显示testbench模块里定义的变量,选择Instance里的对应实例,可以在Objects看到对应实例内的变量

可以右键添加波形,直接Ctrl+W,或者直接把变量拖到窗口,此时添加进来的变量还没有波形

波形全部添加完毕后,按Ctrl+G可以自动按照来源分类

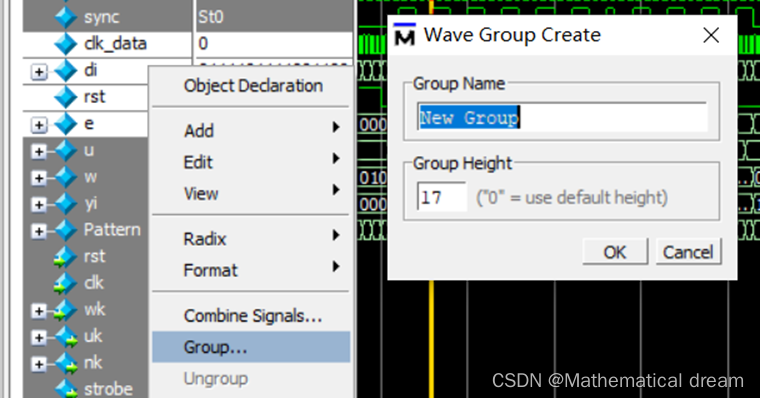

也可以手动分组,但是好像不可以嵌套分组

修改波形后,一分组好像会回到默认波形格式,因此可以先分组后再调整波形的格式

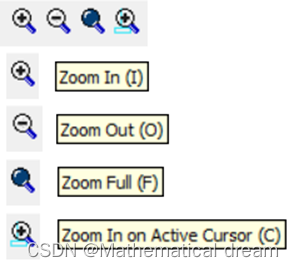

波形查看与格式调整

波形刚出来的时候可以按F看波形全貌,按C可以以光标为中心进行放大

如图为所显示的波形,可以随意拖动波形改变位置,

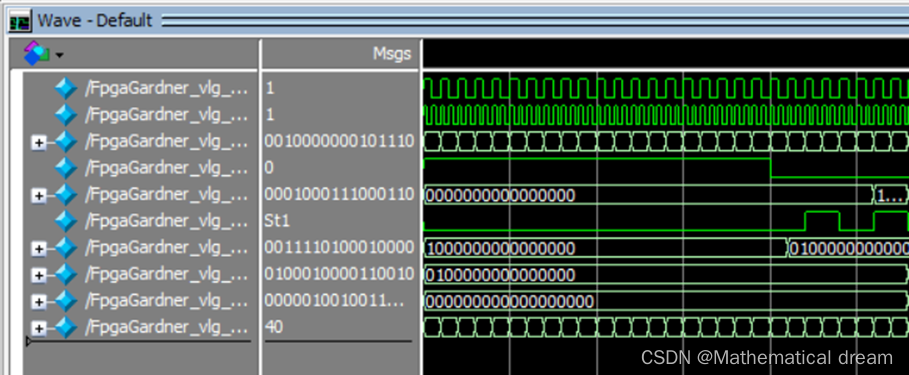

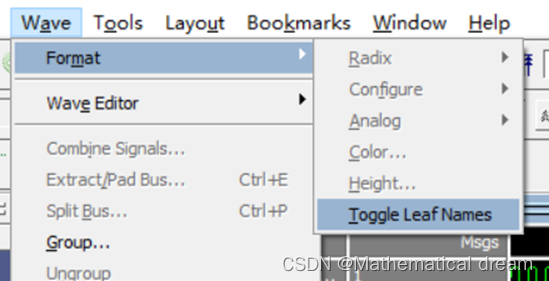

可以让波形名字显示地更简单

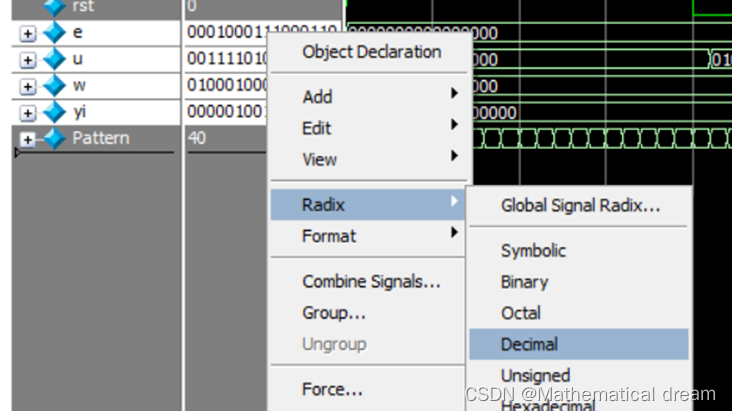

可以显示其他数值显示方式,好像Decimal是有符号10进制,Unsigned是无符号10进制

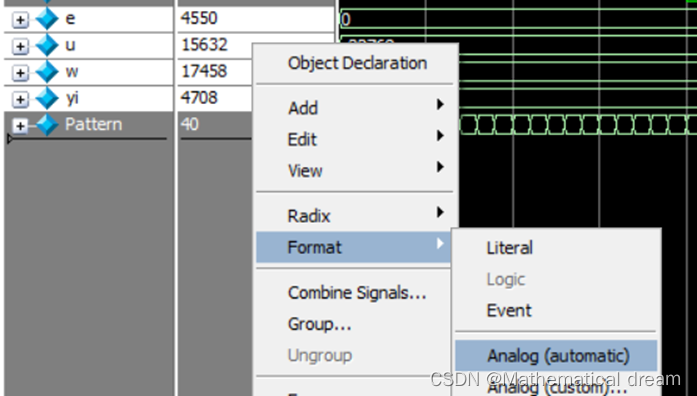

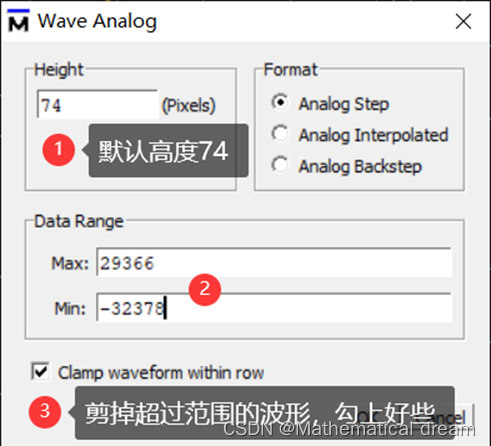

这里可以以模拟的方式显示波形,其中automatic模式是自动根据幅度进行显示,但好像是要有波形(刚添加的波形没波形)才能用,因为需要获取波形极值

也可以选择custom方式

波形设置好后重新仿真显示波形

此时添加的变量还未显示波形

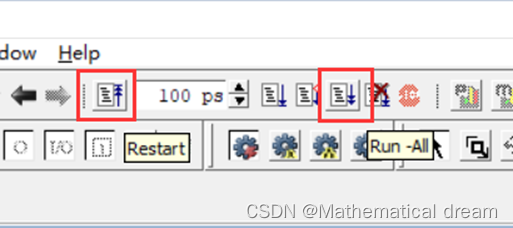

依次按这两个按钮,就可以查看波形

对应命令行命令“restart”和”run -all”

此时所有的变量就都有了波形

3. 保存波形和加载波形

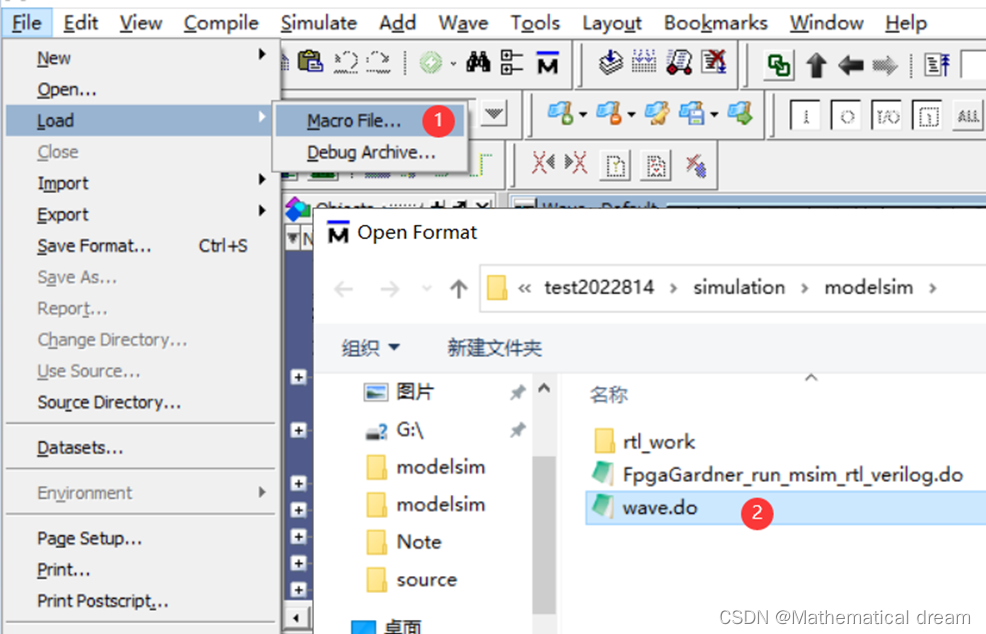

按Ctrl+S可以保存波形,方便下次载入,默认为wave.do,可以根据波形用途取不同的名字方便查看

每次加载波形都是在现有波形后面追加,可以先把现有的波形全选并删除

如果修改了testbench,可以先重新编译一下

加载相应波形

之后“restart”和”run -all”就可以显示波形

4. 修改代码后重新观察波形

如果模块部分代码修改,只编译testbench貌似不够,可以关掉modelsim重新仿真

也可以在命令行按”↑”,找到类似” do FpgaGardner_run_msim_rtl_verilog.do”的语句,或者输”do 工程名_run…”应该可以自动匹配,运行,应该和关掉modelsim重新仿真等价

重仿后波形显示的是默认testbench里的变量,之后load加载波形文件,“restart”和”run -all”就可以查看修改代码后的波形