- 1ERROR 1524 (HY000): Plugin ‘mysql_native_passsword‘ is not loaded_error 1524(hy000) :plugin 'mysgl navtive password'

- 2el-upload文件上传后端实现_el-upload上传文件给后端

- 3SD好复杂,是不是很糊,一文搞懂Stable Diffusion的各种模型及用户操作界面_sd模型网站

- 4mongoDB教程(十):导入、导出_mongodb导出、导入数据

- 5Kafka 消息发送和消费流程_kafka能直接消费另一个kafka么

- 6获得桌面图标所在窗口--兼容Win7_delphi workerw

- 7centos7下mysql8.0.29的安装以及开启ssl访问_mysql8.0.29启动centos

- 8自然语言处理系列九》中文分词》规则分词》逆向最大匹配法_逆向最大匹配算法

- 9AI提示词:打造爆款标题生成器

- 10Web前端最全PHP异世界云商系统开源源码(2),2024年最新Web前端面试题集2024版_2024 php开源商城源码

AXI协议解析(三)_axi incr

赞

踩

了解完通道握手的依赖关系,我们再看看传输事务的结构。首先看传输的地址结构。AXI协议是基于突发(burst)传输的。所谓突发传输,就是在一次事务中,连续地传输多个地址相邻的数据。一次突发传输中可以包含一至多次数据(Transfer)。每个 transfer 因为使用一个周期,又被称为一拍数据(Beat)。每个数据可以是多个Byte构成。

协议规定,每次突发传输的累计地址不能跨4KB边界。至于为啥是4KB而不是别的数值,这是最初操作系统的问题,以4KB为一个页(page),对于某些设备而言,跨了4KB边界可能就是另外一个设备了。

ARLEN用于读地址通道的突发长度,AWLEN用于写地址通道的突发长度。下文中AxLEN指ARLEN或AWLEN, x指代R或者W,对于其它信号也类似,以后不再赘述。在AXI3中,对于所有的突发类型,都支持1-16的突发传输。AXI4中,INCR类型支持1-256突发传输,其它类型依然是1-16。所以对于AXI3来说,AxLEN信号是4bit宽度;而在AXI4中,AxLEN是8bit宽度。一次突发传输的长度是AxLEN+1,因此,最小长度就是1了(毕竟0的话没有任何意义)。

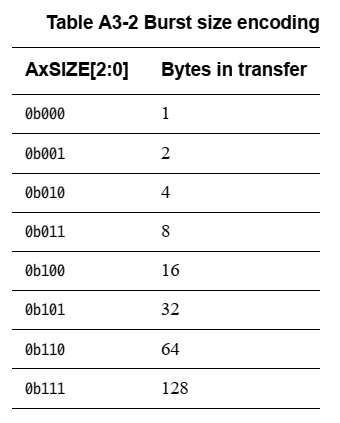

AxSIZE信号指示突发传输中的数据位宽。数据位宽不能超过数据总线本身的位宽,而当数据总线位宽大于突发传输的位宽时,将根据协议的相关规定,将数据在部分数据线上传输。

突发传输有以下几种类型:

FIXED,所有数据都使用起始地址。该模式适合对某个固定地址进行多次数据更新,比如读写一个 fifo 时,读写地址就是固定的。

INCR,后续数据的地址在初始地址的基础上进行递增,递增幅度与传输宽度相同。适合对于RAM 等通过地址映射(mapped memory)的存储介质进行读写操作。

WRAP,首先根据起始地址得到绕回边界地址与最高地址。当前地址小于最高地址时,WRAP 与 INCR 类型完全相同,地址递增。但到递增后的地址到达最高地址后,地址直接回到绕回边界地址,再进行递增,就这样循环往复。最高地址由绕回边界地址计算得到。这种传输类型适用于对缓存行(cache line)的操作。

突发传输类型是通过AxBURST信号来指示的,具体参考下图:

好了,到这里,我们知道了每次突发的起始地址是主机发出的。AxLEN用于指示要传输多少次数据(beat);AxSIZE用于指示每个数据有多少Byte;AxBURST用于指示突发类型,除去首次传输的地址,下次传输的地址可以根据AxBURST和首地址计算得出。

协议中规定,通信双方都不能在传输事务的所有 Transfer 完成前提前结束。哪怕发生错误,也要走完整个传输事务的流程。但是主机有办法减少传输的数据。在写传输事务中,发送方可以通过置低所有写有效位的方式,使得写数据无效。在读传输事务中,主机可以直接丢弃读取到的数据。

分析完传输的地址结构,再来看看读写数据的结构。主要是涉及窄传输(Narrow transfers),非对齐传输(unaligned transfer)和混合大小端(mixed-endian)传输等话题。

WSTRB信号用于指示WDATA中的哪些数据byte是有效的。WSTRB[n] 对应的是WDATA[8n+7:8n],也就是:当 WSTRB[n] 为 1 时,WDATA[8n+7:8n]有效。

当主机发起的传输位宽小于总线宽度时,就是一次窄传输。如果是INCR或者WRAP类型,可以每拍(beat)使用不同的字节位置(byte lane),如果是FIXED类型就不可以了。协议中给出了两个例子,我们看一个就好了,如下图:

突发长度是5

起始地址0

每次传输8bit

数据总线宽度32bit

突发类型是INCR

图中灰色表示该byte无效,我们可以看到,每次传输的有效字节位置是不同的。在窄传输中,主机可以调整有效数据的字节位置,以及给出字节有效信号 WSTRB,能够使从机无需进行数据重组等工作。

AXI中还有一个问题是大小端问题,之前的文章讲过什么是大端和小端。其根本不同就是高字节数据存在低地址位还是高地址位。AXI协议定义了一种字节顺序不变端序(byte-invariant endianness)方案。

1.无论大端或小端模式,每个数据结构存储空间的分配方式是相同的

2.该数据结构按照其大端或小端模式决定字节存储的地址顺序

3.在传输过程中不考虑数据结构的大小端,按照字节原先存储的顺序,原样传输并存放至对端

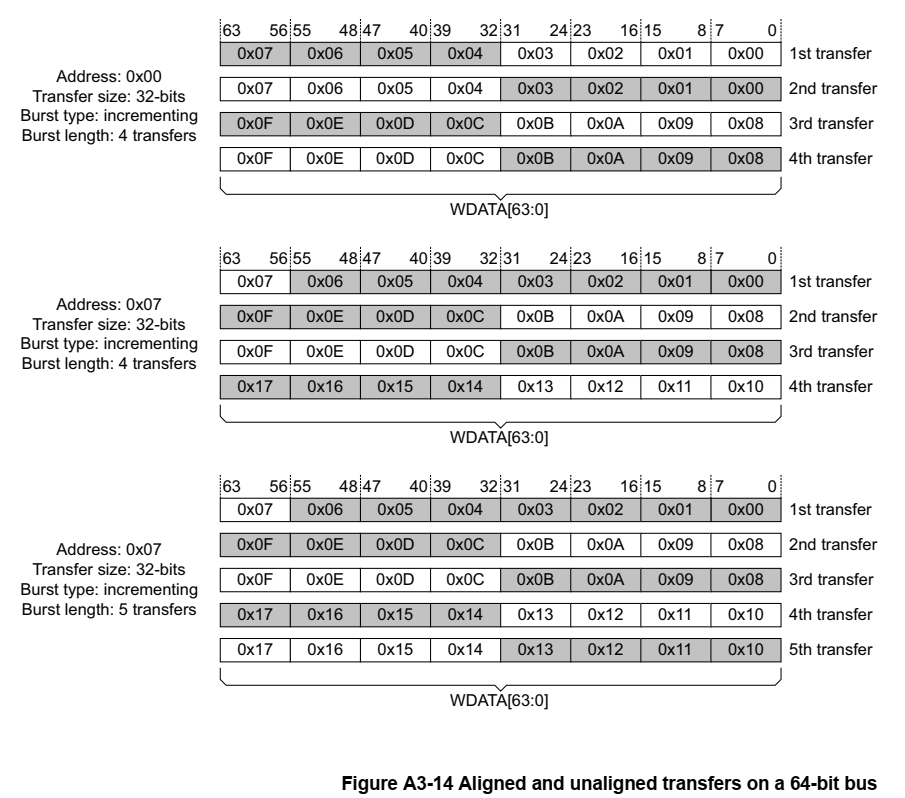

AXI 协议支持地址非对齐的传输,允许突发传输的首字节地址,即起始地址与突发传输位宽不对齐。比如,总线位宽为 32bit,也就是4byte,这时要保证对齐,起始地址的最低两位必须是2‘b00。如果起始地址为 0x1002,则产生了非对齐现象。

主机可以使用低阶地址行表示未对齐的起始地址,然后提供一个对齐的地址,并使用字节通道选通信号通知未对齐的起始地址。下面是协议中给出的例子:

看完了数据结构。就剩下读写响应结构了。读写响应信号分别是RRESP/BRESP,各2bit,总共4种状态:

OKAY ,常规访问成功

EXOKAY,独占(exclusive)访问成功

SLVERR,从机错误,从机接收到了访问请求,但因为种种原因向主机返回了一个错误状态

DECERR,解码错误,一般由互连(interconnect)组件产生,表示主机发送的传输事务地址无效,无法将传输事务发送给某个从机。

原文地址:https://mp.weixin.qq.com/s/I8YrDEB5f-B0URGnYl1BYA