【FPGA】AXI学习_fpga axi

赞

踩

1.什么是AXI?

AXI是ARM AMBA的一部分,AMBA是1996年首次推出的微控制器总线系列。AXI的第一个版本首次包含在2003年发布的AMBA 3.0中。发布与2010的AMBA4.0包含了AXI的第二个主要版本,AXI4。

这儿有3种AXI4接口:

AXI:用于高性能存储映射需求。

AXI4-Lite:用于简单,低吞吐率的内存映射通信。(例如,进出控制器和状态控制器)

AXI4-Stream:用于高速流数据。

2.AXI如何工作?

AXI规范描述了一个在单AXI主机和AXI从机之间的接口,代表IP核之间相互交换信息。多个内存映射的AXI主从可以使用AXI基础IP块连接在一起。Xilinx AXI Interconnect IP和新的AXI SmartConnect IP包含一个可配置的数量的AXI标准的主从接口,可以用于多AXI主从之间的路由。

AXI4和AXI4-Lite接口都由5个不同通道组成:

读地址通道

写地址通道

读数据通道

写数据通道

写响应通道

数据可以同时在主和从之间的两个方向上移动,并且数据传输的大小可以变化。AXI4中的限制是最多256个数据传输的突发事务。AXI4 - lite只允许每个事务传输一次数据。

为读和写提供单独的数据和地址连接,从而允许同时进行双向数据传输。

需要一个地址然后突发256字的数据。

3.信号说明

3.1全局信号

ACLK:全局时钟信号。

ARESETn:全局复位信号,低有效。

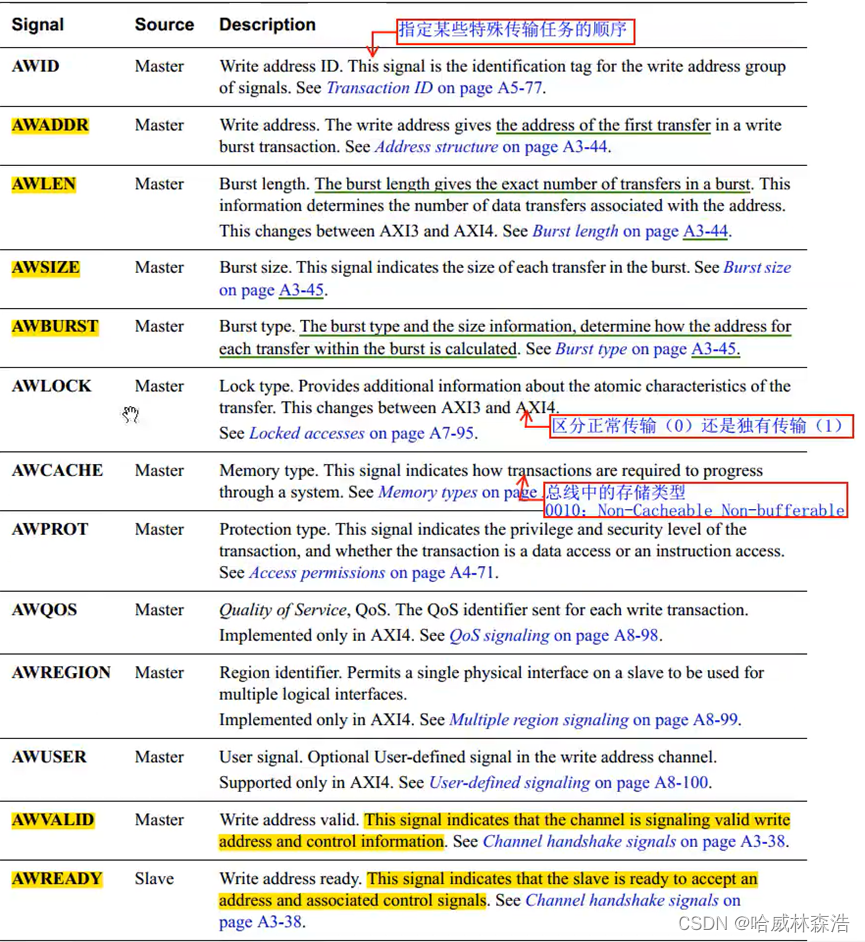

3.2写地址通道(AW开头,表示address write)

AWADDR:指定在突发传输下的第一个地址

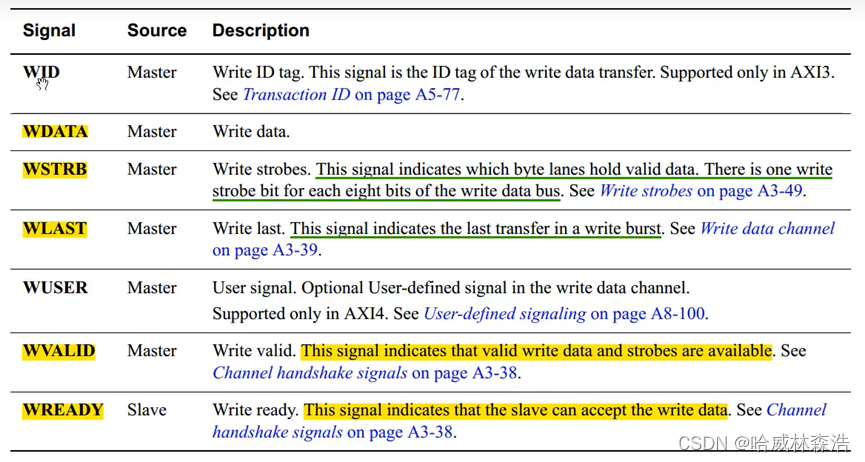

AWLEN:8位信号,突发长度,真实的长度为AWLEN+1

AWSIZE:3位信号,突发大小。指单次的数据量是多少字节具体设置如下。(计算方式:log2(位宽/8))

AWBURST:2位信号,突发类型,一共有三种如下图

FIXED:突发时,传输的地址不变。

INCR:自增型,根据突发大小,计算出下一次的传输地址。

WRAP:回环递增,当递增到高位地址后,会回环到低位去。

AWVALID:写地址有效信号,当前通道的地址信号和控制信号是否有效。

AWREADY:从机是否准备好接收地址和控制信息。

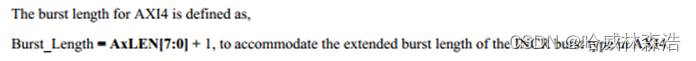

3.3 写数据通道

WDATA:要写入的数据。

WDATA:要写入的数据。

WSTRB:频闪信号,屏蔽不需要被写入的数据。

WLAST:突发传输的最后一个数据,每次突发传输后会拉高。

WVALID:写有效信号。

WREADY:写准备信号。

3.4写响应通道

BRESP:二位信号,写传输状态。

OKAY:表示正常访问成功。

EXOKAY:独占式存取okay。

SLVERR:从机错误,从机已经接收到数据,但出现错误。

DECERR:解码错误,互联模块无法成功译码从机。

3.5读地址通道

类比写地址通道

类比写地址通道

3.6读数据通道

类比写数据通道。

类比写数据通道。

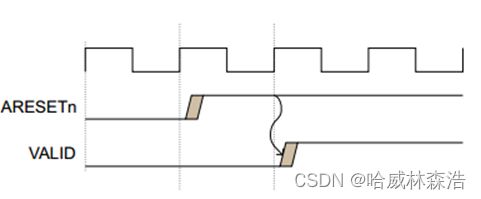

4.时钟和复位

时钟:所有的输入信号都在ACLK的上升沿采样。所有的输出都在ACLK的上升沿之后。

在复位时:

主机接口的ARVALID,AWVALID和WVALID会被拉低。

从机接口的RVALID,和BVALID也被拉低。

其他信号可被驱动到任何值。

5基础读写事务

AXI的基础机制有:

握手过程

通道信号要求

5.1握手过程

所有五个事务通道都使用相同的VALID/READY握手过程来传输地址,数据和控制信息。这种双向控制机制意味着主和从都可以控制速率。源端生成VALID信号来表明什么时候地址,数据,控制信息有效。目的端生成READY信号来表明它可以接收信息。只有当VALID和READY都为高时,才能传输。

通道握手信号

5.2写地址通道

只有在主机生成有效的地址和控制信号时,才能施加AWVALID信号。

默认的AWREADY信号可以为高或为低。规范建议为高。当AWREADY为高,从必须可以接收任何有效的地址。

5.3写数据通道

5.3写数据通道

在一个写突发时,只有当主写有效的数据时,才可以施加WVALID信号。且必须持续到从施加WREADY,直到时钟上升沿。

默认的WREADY可以为高,但是前提时在一个周期内从可以一直接收数据。

主在写突发的末尾必须施加WLAST信号。

5.4写响应通道

5.5读地址通道

5.6读数据通道

5.7读事务的依赖性

简单来说,单箭头表示箭头指向的信号可以不等待箭头源信号。

而双箭头指向的信号需要滞后于箭头源信号。

5.8写事务的依赖性

同上

同上

6AXI4-Lite定义

AXI4-Lite关键的功能如下:

所有的传输突发长度都为1.

所有的数据访问都使用全部带宽。

AXI4-Lite支持的总线带宽为32位或64位。

所有的访问都是不可修改的,不可缓冲的。

不支持独占访问。

7信号清单

相比于AXI4更加简单。

本文内容主要来自于

IHI0022E_amba_axi_and_ace_protocol_spec

UG1037-en-us