实验三 原码一位乘法实验(基于Logisim)_原码一位乘法器logisim

赞

踩

1、实验目的

学生掌握原码一位乘法运算的基本原理,熟练掌握 Logisim 寄存器电路的使用,能在 Logisim 平台中设计实现一个 8*8 位的无符号数乘法器。

2、实验内容

在 alu.circ 文件中原码一位乘法器子电路中增加控制电路和数据通路使得该电路能自动完成 8 位无符号数的一位乘法运算,设置引脚初始值,然后驱动时钟自动仿真,电路可自动完成运算,运算结束结果传输到输出引脚,运算结束时电路应该自动停止。

3、实验步骤

1.理解原码一位乘法的原理。

2.分析需要进行的操作,确定需要用到的部件。

3.针对每个部件,完成逻辑电路。

4.提交设计好的电路进行评测。若出现错误,立刻分析并修改,直至通过评测。

4、方案设计

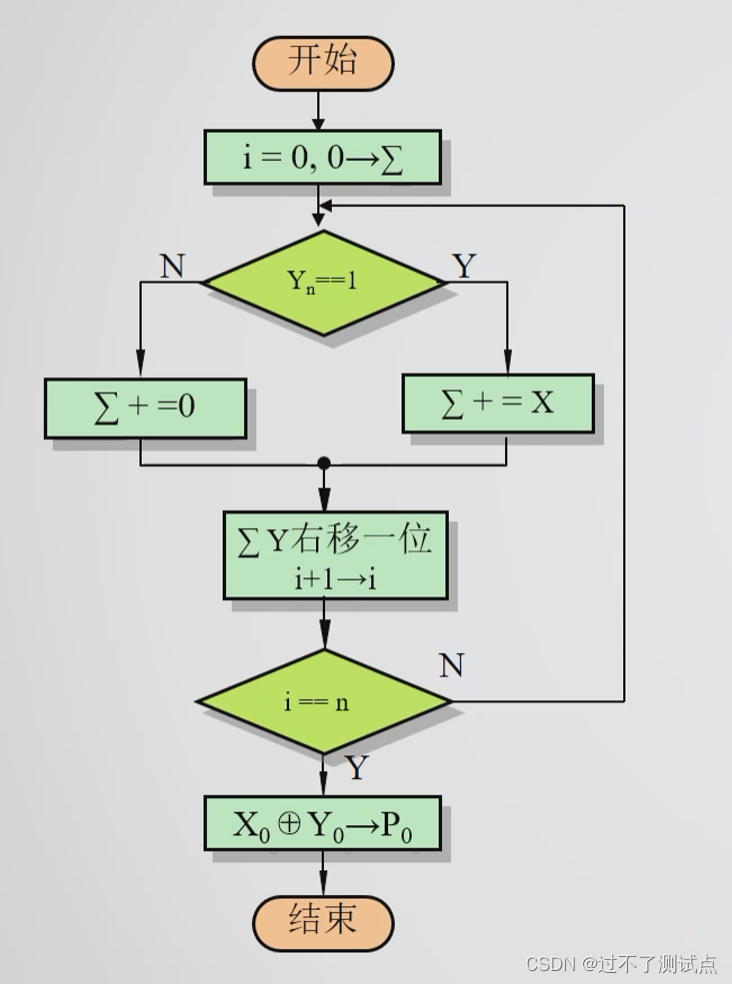

源码一位乘法的流程图如下

本次实验的方案设计主要围绕着以下几个问题展开。

如何实现寄存器Y的初始化将乘数Y送入到寄存器中?

这里采用比较器和计数器。当脉冲数为0的时候进行初始化。二选一多路选择器将乘数Y送入到寄存器Y中。

如何实现部分积加法运算时加0和加X的绝对值的选择?

用二路选择器实现选择加0还是被乘数X的绝对值。选择依据是乘数Y的当前最低位是0 还是1,若是0,则直接加0,若为1,则加被乘数X的绝对值。

如何用器件实现数据的移位操作?

利用两个错位的分线器实现数据的移位操作。在本实验中因为新得到的部分积和乘数都需要进行移位操作。所以要用到两组每组两个位宽为八的分线器。其中新部分积的最高位由串行加法器的进位得到,乘数Y的最高位由部分积右移出来的那一位得到。

如何判断什么时候乘法运算结束?

这里采用比较器和计数器。由于被乘数和乘数都是八位,所以当脉冲次数大于8 的时候触发Stop信号。改变两个寄存器使能端的值,使寄存器不再工作。

如何保存运算结果?

完成运算后,部分积寄存器保存乘积的高位部分,乘数寄存器中保存乘积的低位部分。两者结合即为最后的运算结果。

5、本次实验遇到的困难和错误

遇到的问题:将乘数的最低位接入加法器下面的二路选择器时出现位宽不匹配的问题。

解决方法:用分线器一端连接Y寄存器的输出端,其余八个端口中选择最低位连接二路选择器。

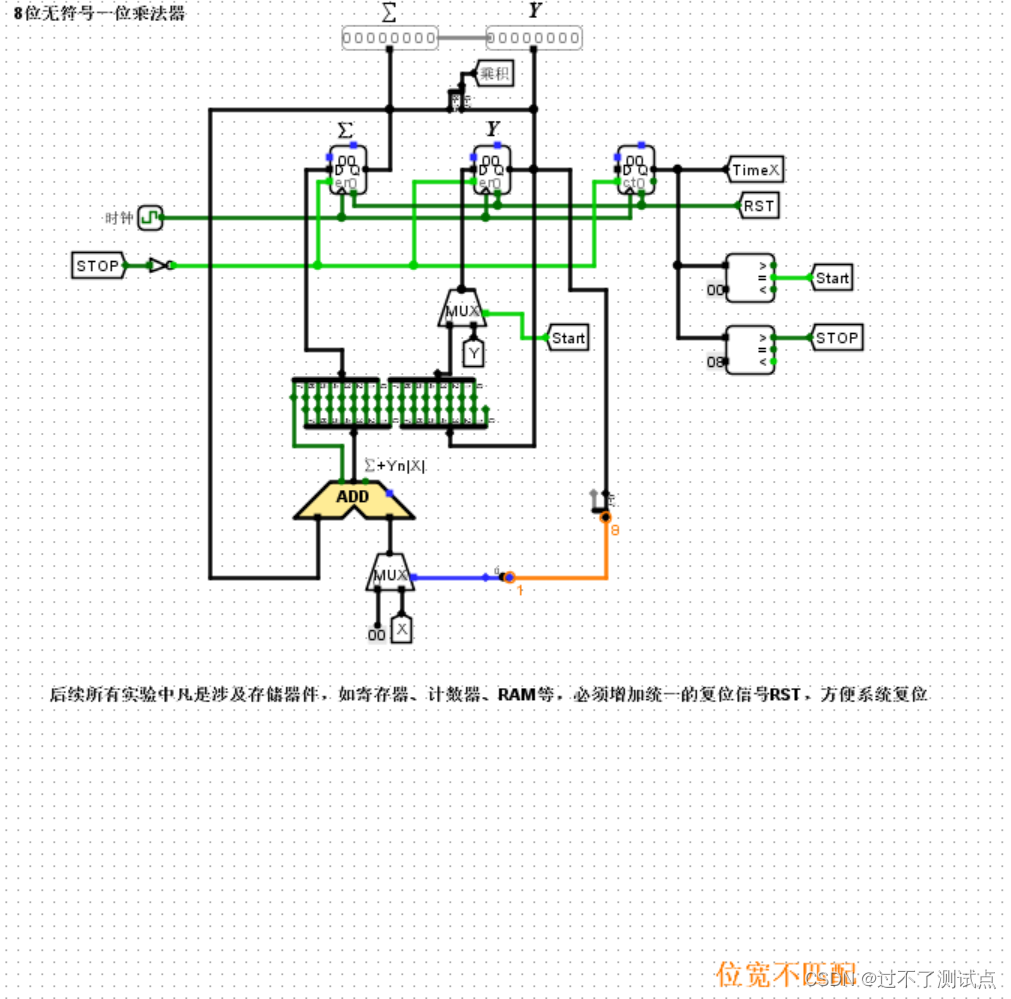

错误截图

6、实验电路图及评测结果

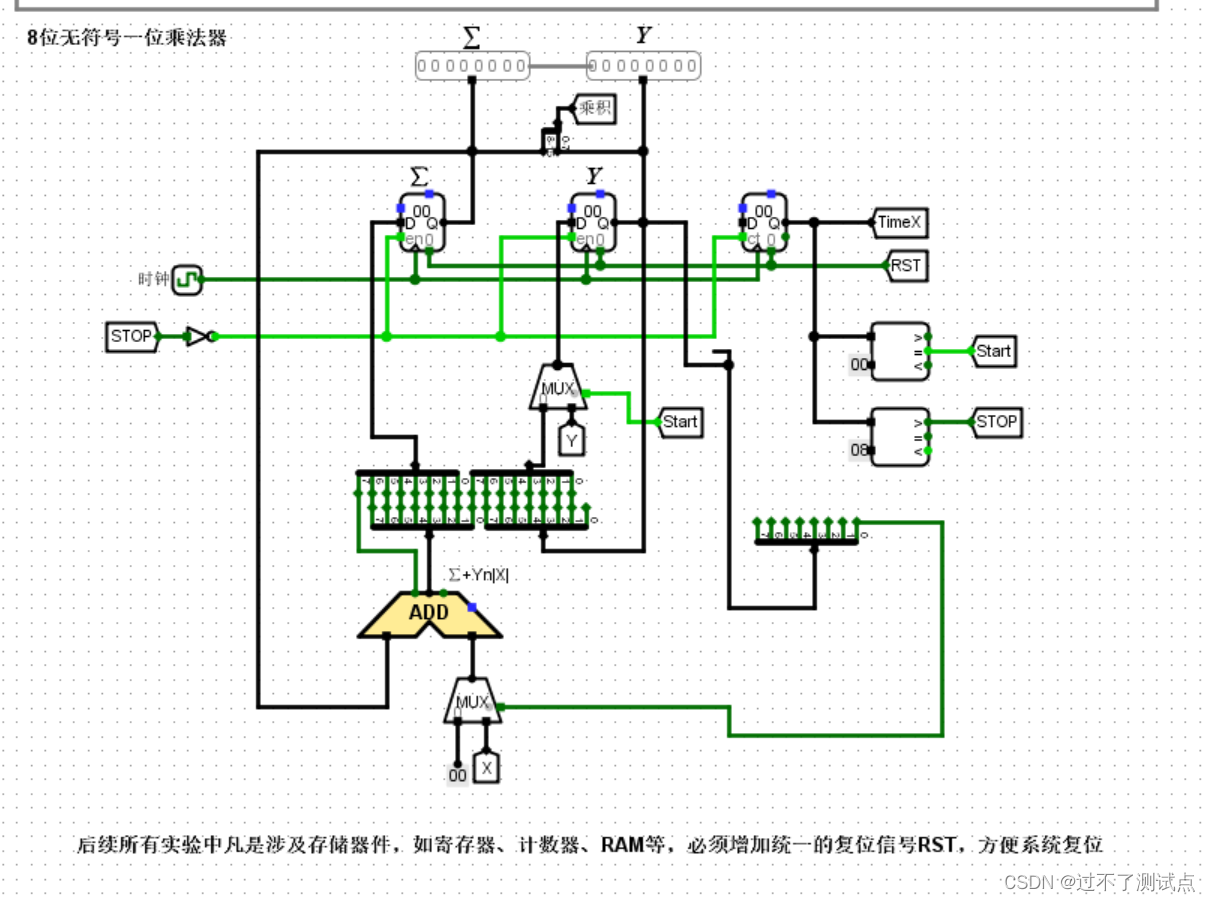

电路图

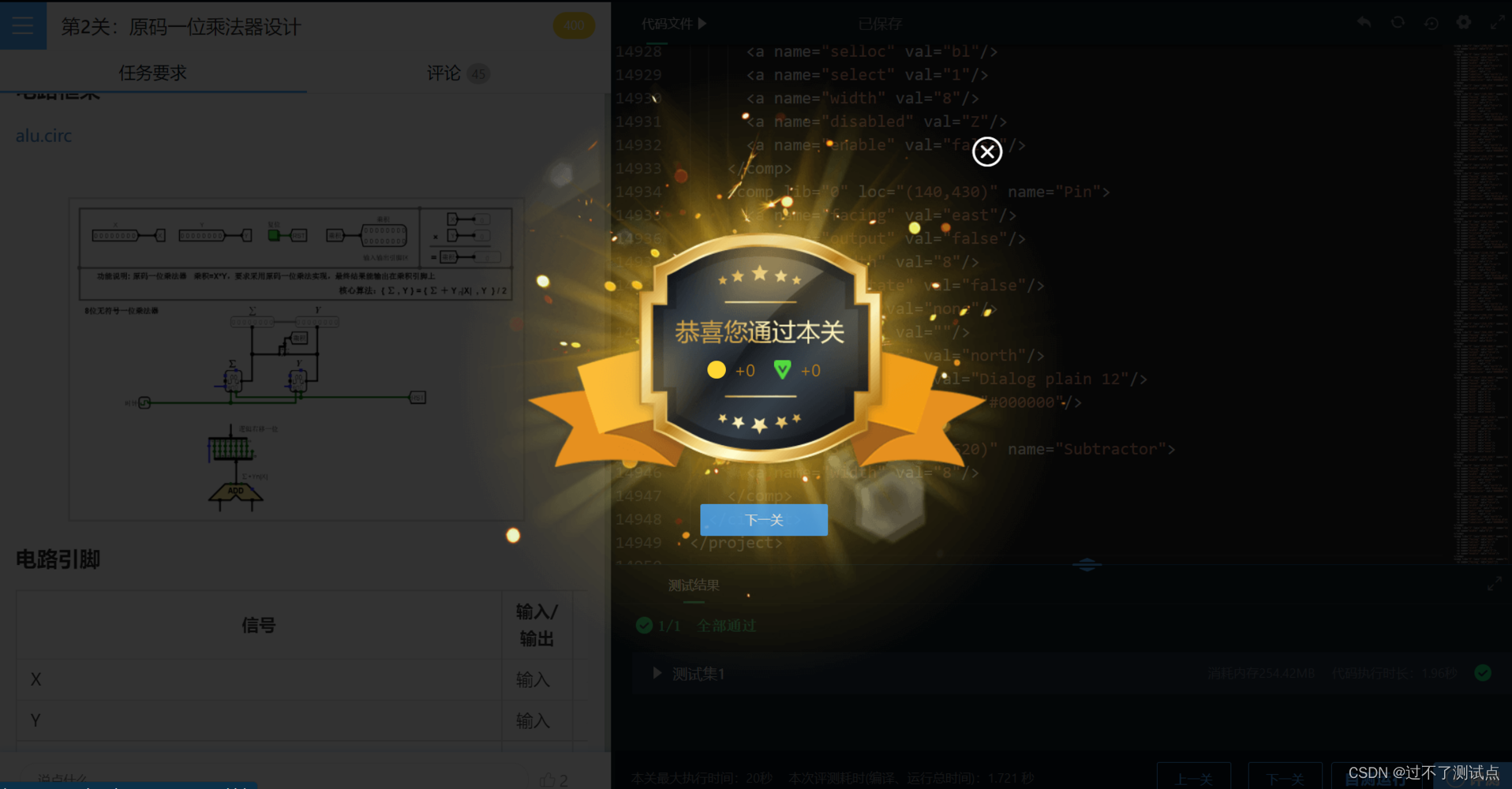

测试结果

7、心得体会

本次实验设计的电路实现了原码一位乘法的功能。由于本次实验难度较大,所以我是在看完谭志虎教授的慕课后,在他给出的提示下完成的。通过本次实验,我加深了原码乘法运算原理的理解,并将理论知识应用到实践当中。与此同时也熟悉了Logisim中部分器件如分线器和比较器的功能。培养了硬件设计的思维,个人实践能力和动手能力得到提高。