- 1ORB_SLAM3安装运行&性能测试对比_orbslam3 ros

- 2Neural Data-to-Text Generation with Dynamic Content Planning_neural pipeline for zero-shot data-to-text generat

- 3Python+Django+Mysql个性化小说推荐系统 小说网站推荐系统 基于用户、项目、内容的协同过滤推荐算法WebNovelCFRSPython python实现协同过滤推荐算法实现源代码下载_小说推荐系统算法 github.

- 4测试面试宝典(十)—— 请问测试开发需要哪些知识?需要具备什么能力?

- 5unity发布webGL压缩方式的gzip,使用nginx作为web服务器时的配置文件_unity gzip

- 6Hadoop-21 Sqoop 数据迁移工具 简介与环境配置 云服务器 ETL工具 MySQL与Hive数据互相迁移 导入导出

- 7NLP 文本分类_nlp文本分类算法

- 8pg无法启动

- 9Proteus仿真STM32的课设实例3——汽车倒车测距提示仪_stm32课设

- 10物体检测框架 RetinaNet 深度神经网络简介

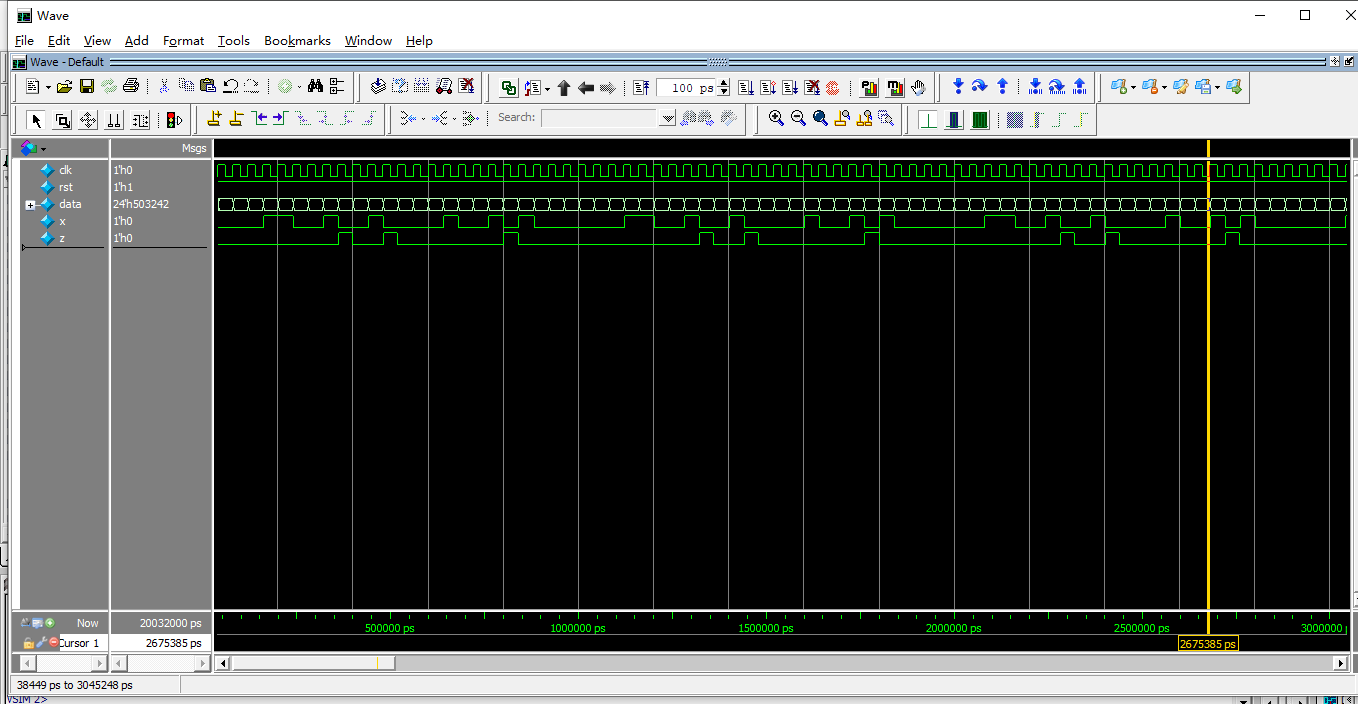

Quartus 18.1和Modelsim 10.4联合仿真详细过程_quartus prime lite edition仿真

赞

踩

Quartus和Modelsim联合仿真详细过程

软件

- Modelsim SE-64 10.4

- Quartus Prime 18.1 Lite Edition

关联软件

启动quartus,菜单栏选择Tools->options,左侧选择EDA Tool Options,在modelsim一栏选择modelsim安装路径下的win64文件夹。

创建工程

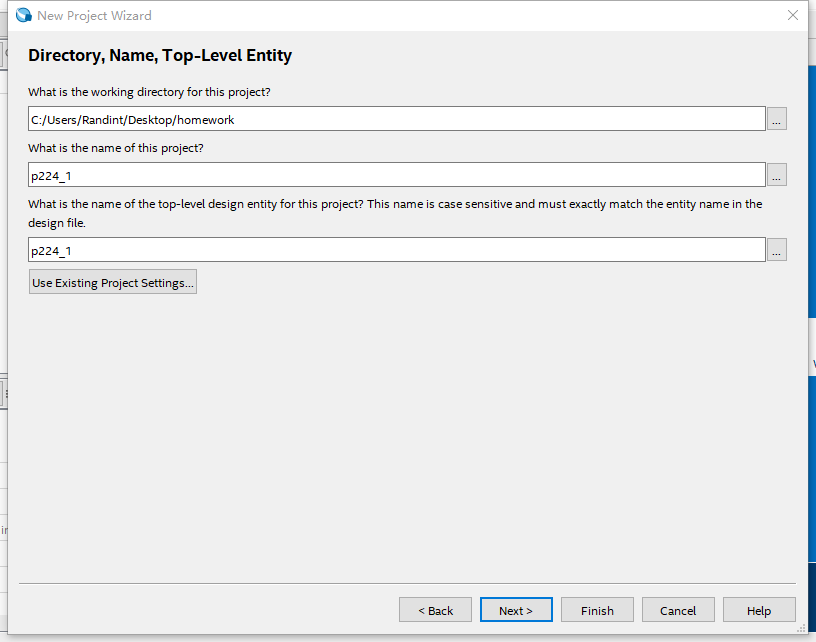

File->New Project Wizard,选择存放项目路径及工程名字,路径不要有汉字,空格及其他乱七八糟的符号,next。

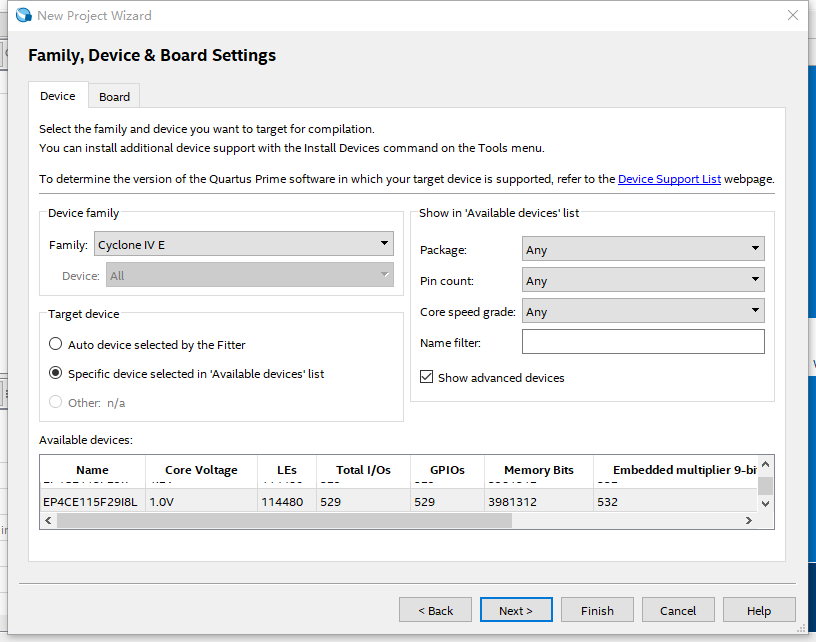

然后选择对应芯片型号,如果仅是写写程序,随便选一个凑合凑合next。

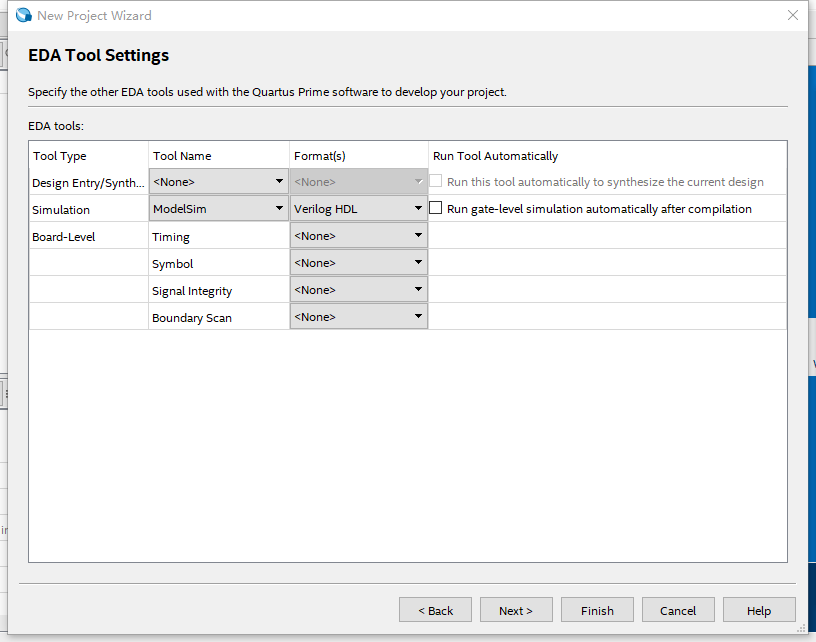

仿真工具选择ModelSim,语言格式Verilog HDL,一路next直到Finlish。

编写及编译

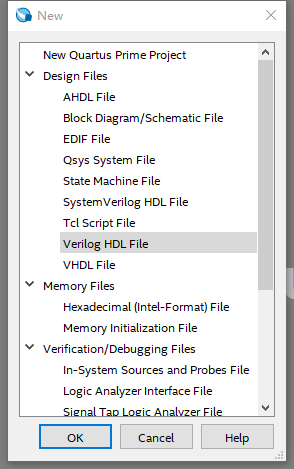

File->New,选择Verilog HDL。

以一个简单的序列检测器为例,程序如下。项目顶层模块名需要和工程名字一致,由于该项目就一个模块,所以模块名为p224_1。

module p224_1(x,clk,rst,z); input x,clk,rst; output z; reg [2:0] state; //状态 wire z; parameter IDLE = 3'd0, A = 3'd1, B = 3'd2, C = 3'd3, D = 3'd4, E = 3'd5, F = 3'd6, G = 3'd7; assign z = (state==D && x==0)?1:0; //状态为D且又检测到x为0,此时输出z为1 always@(posedge clk or negedge rst) if(!rst) begin state <= IDLE; end else casex(state) IDLE: if(x==1) state <= A; else state <= IDLE; A: if(x==0) state <= B; else state <= A; B: if(x==0) state <= C; else state <= F; C: if(x==1) state <= D; else state <= G; D: if(x==0) state <= E; else state <= A; E: if(x==0) state <= C; else state <= A; F: if(x==1) state <= A; else state <= B; G: if(x==1) state <= F; else state <= B; default:state <= IDLE; endcase endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

保存后,点击界面上方蓝色三角形按钮,或菜单栏processing->Start compilation开始编译,在左下角message窗口查看结果。

编写测试文件

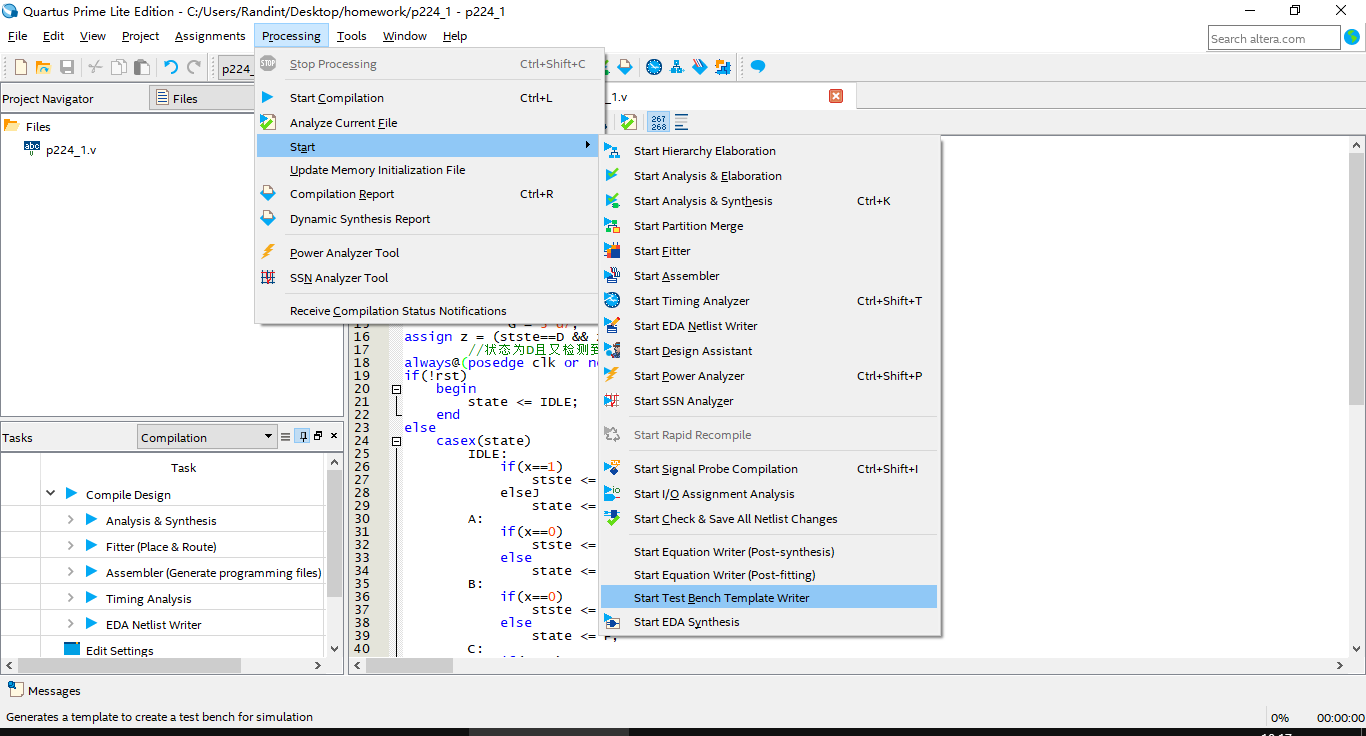

菜单栏选择processing->Start->Start Test Bench Template Writer,此时针对该工程会生成一个test bench的模板。

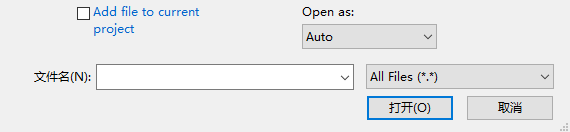

打开该文件,File->open,工程文件夹下simulation->modelsim->工程名.vt,注意右下角文件类型选择All Files

编写测试程序,复制测试程序的模块名备用,即该示例中的p224_1_vlg_tst,保存即可。

`timescale 1 ns/ 1 ns module p224_1_vlg_tst(); reg clk; reg rst; reg [23:0]data; wire z,x; assign x=data[23]; p224_1 i1 ( .clk(clk), .rst(rst), .x(x), .z(z) ); initial begin clk = 1; rst = 1; #2 rst = 0; #30 rst = 1; data = 20'b1100_1001_0000_1001_0100; #20000 $stop; end //时钟 always #20 clk <= ~clk; always @(posedge clk) begin #2 data={data[22:0],data[23]}; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

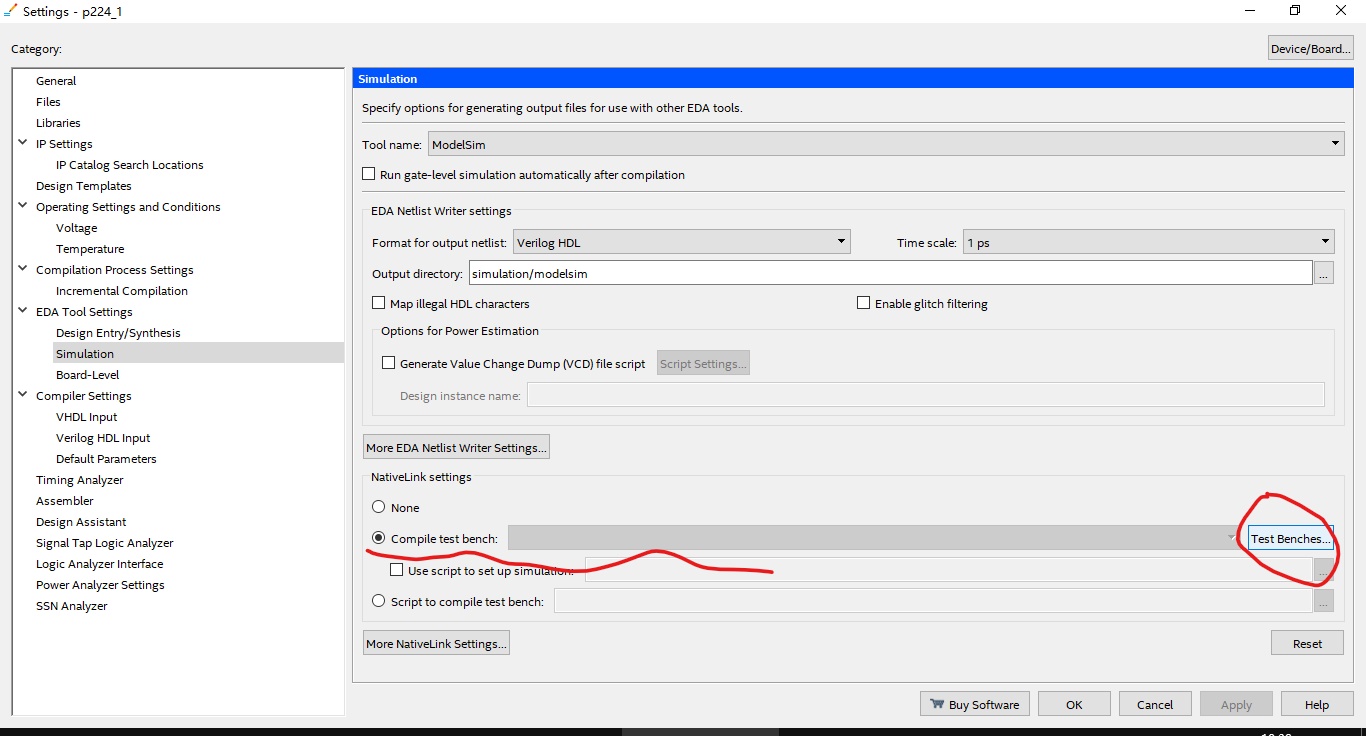

接着菜单栏打开Assignment->Settings,左侧EDA Tool Settings->simulation。选择Test Benches

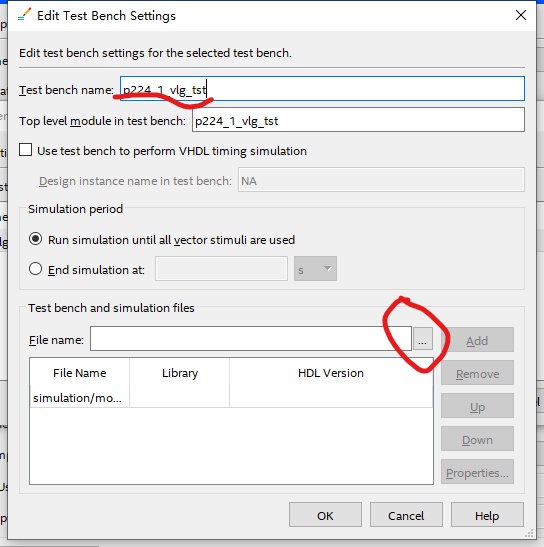

在打开的窗口中填入刚刚复制的测试程序的模块名,接着选择测试文件(工程名.vt),点击add会添加到下方窗口中,最后一路OK即可。

仿真

各类仿真的介绍

https://www.cnblogs.com/lvtu/articles/5553608.html

https://blog.csdn.net/i13919135998/article/details/52458685

菜单栏Tools->Run simulation Tool,RTL simulation为前仿真(综合后仿真,即综合后功能仿真,验证逻辑功能是否正确),gata level simulation为后仿真(时序仿真,综合后考虑线路延时),若测试程序出现错误,会在modelsim的窗口中提示。

记录遇到的一个错误

上述程序为Verilog 数字系统教程第三版(夏宇闻 编著)中的例题,在写程序时不小心打错了个字母

assign z = (state==D && x==0)?1:0; //正确

assign z = (state==D && z==0)?1:0; //错误

- 1

- 2

且编译没有报错,在仿真时提示Iteration limit reached at time 340 ns