热门标签

热门文章

- 1hadoop的三大核心组件之HDFS和YARN_hdfs yern

- 2【实体对齐·HGCN】Jointly Learning Entity and Relation Representations for Entity Alignment

- 3Linux系统简介_linux硬件设备由什么直接管理

- 4Git入门到精通(大全)_git从入门到精通

- 5软件测试只会“点点点”,凭什么让开发看的起你?_软件测试点点点

- 6echarts的简单使用_echarts简单使用

- 7Introduction to 3D Game Programming with DirectX 12 学习笔记之 --- 第七章:在Direct3D中绘制(二)_direct3d画圆

- 8HarmonyOS Next 使用Web获取相机拍照图片案例_onshowfileselector返回值

- 9用70行Python编写一个概率编程语言_pyro教材 概率编程

- 10自动化搞钱:7个最强免费AI工具,10倍速提升赚钱、超过99%的人_7個最強免費ai工具,10倍速提升賺錢、自媒體內容創作、工作效率,超過99%的人

当前位置: article > 正文

基于Quartus Prime18.1的安装与FPGA的基础仿真(联合Modelsim)教程_intel庐 quartus庐 prime lite edition design software

作者:小舞很执着 | 2024-07-16 04:23:48

赞

踩

intel庐 quartus庐 prime lite edition design software version 18.1 for wi

Quartus是一种美国科技公司Intel(英特尔)公司开发的FPGA(现场可编辑门阵列)设计编译软件,用作设计、仿真、综合和布局、支持多种编程语言,包括VHDL、Verilog等,并具有丰富的功能和工具库,可广泛应用于各种数字电路设计和实现。

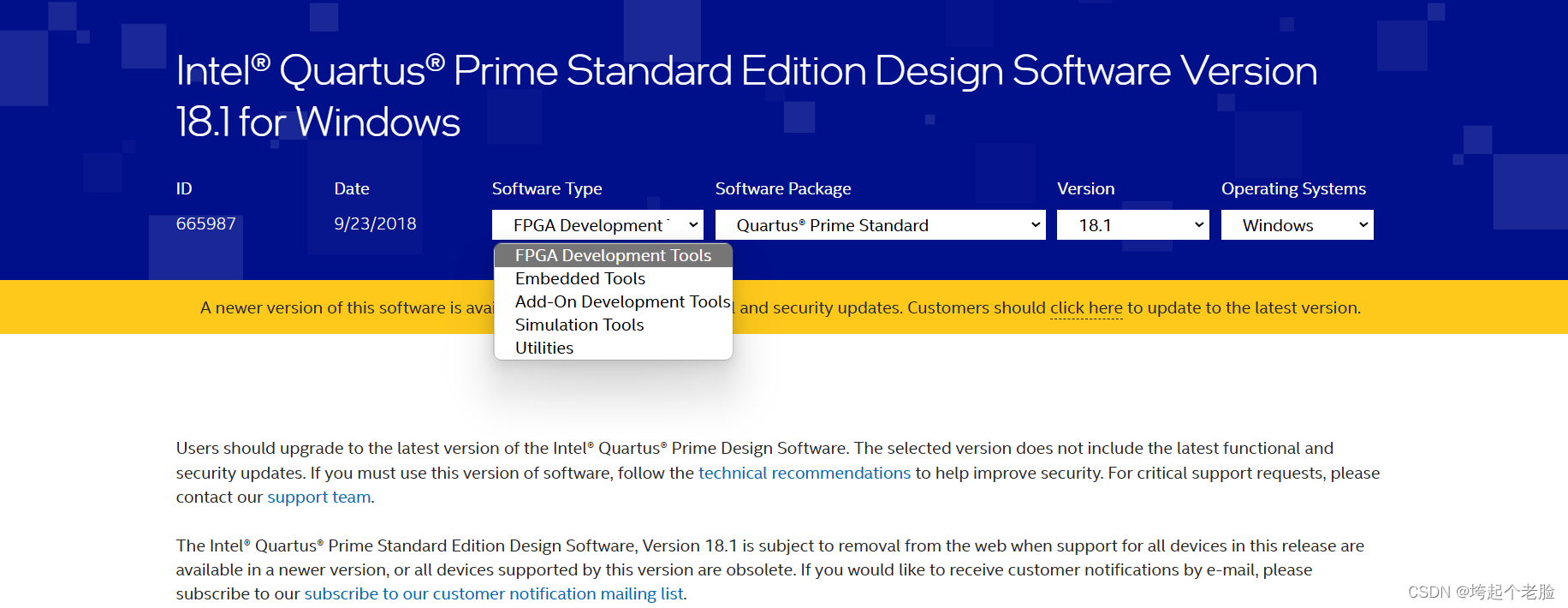

一、 Quartus Prime 18.1 的下载

剑指官网:Intel® Quartus® Prime Lite Edition Design Software Version 18.1 for Windows

选择好相应安装包、版本号、相应操作系统

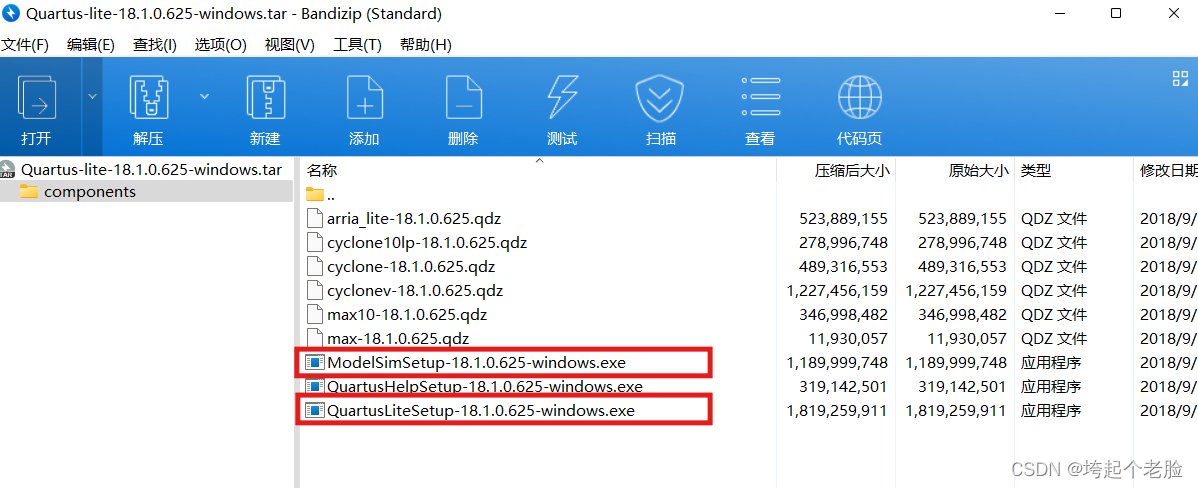

对应下载即可,大约24GB大小下载后打开安装包

二、安装教程

2.1 quartus程序的安装

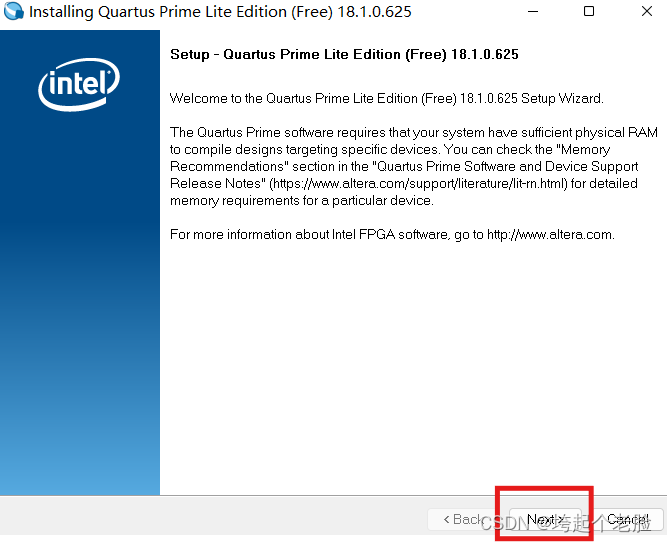

完成上述下载操作后点击如上图所框选的运行文件,打开点next

同意安装使用协议,点Next;

选择安装路径后,继续下一步;

选择需要安装的内容,进行下一步

下一步直到设备驱动程序完成

2.2 ModelSim的安装

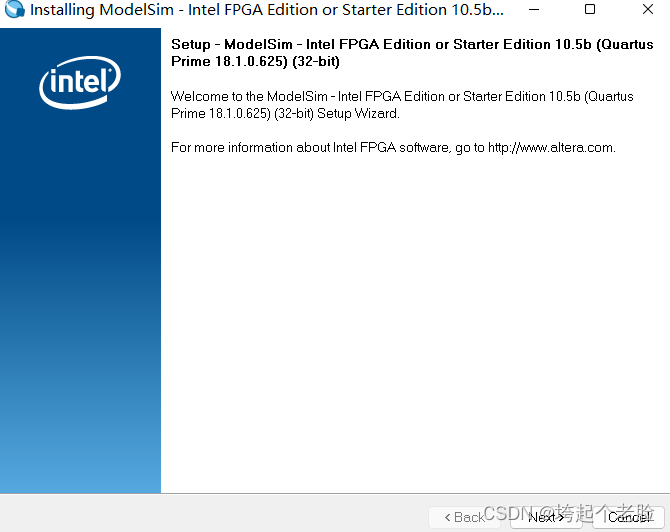

此安装影响后续的仿真模拟,所以仍需要安装调制,打开setup,点Next

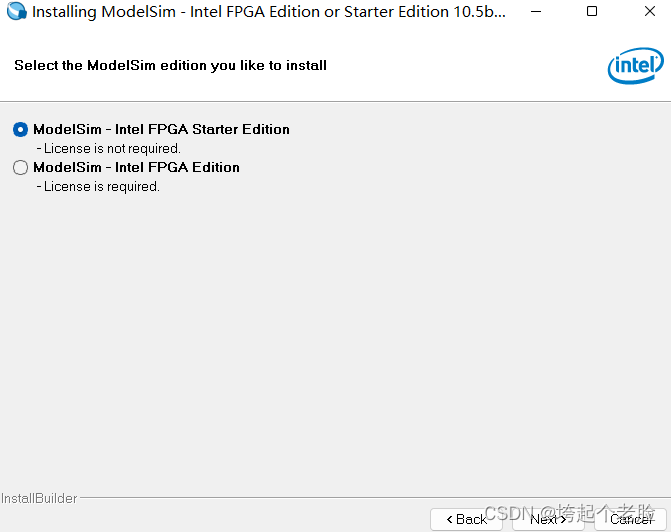

无协议,选择License is not required,选择Next

接受条款选择路径,next

默认安装内容,继续下一步直到设备驱动程序完成

三、基于Quartus 的 CPLD/FPGA 应用开发

3.1. 建立工程

打开 Quartus Prime Lite 18.1 开发环境。菜单 File->New Project

Wizard.

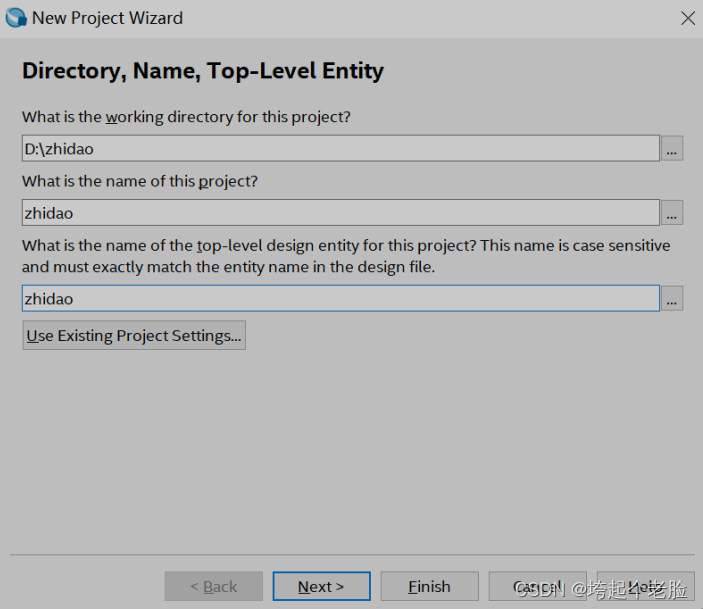

Directory, Name, Top-Level Entity 页选择合适的工程存储路径(路

径不要有中文,最好

不要在桌面

),输入工程名和顶层实体名。

例如:

工程存储路径 D:/zhidao

工程名 zhidao

顶层实体名 zhidao

接下来 Project Type 选 Empty project,即建立一个空的工程

Add Files 页直接 Next

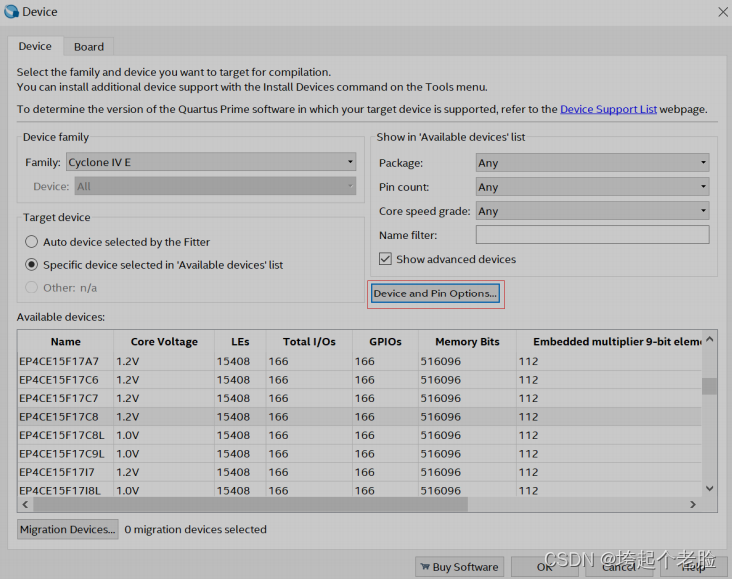

Family, Device & Board Settings 页里器件 Family 选择 Cyclone IV E,在下方选择 EP4CE15F17C8

(不要选成 EP4CE15F17C8L,最后带 L为低电压版)

EDA Tool Settings 页里,Simulation 选择 ModelSim-

Altera

(

不要选

ModelSim

)和 VHDL

Summary 页点 Finish,完成工程的建立

菜单 New -> Design Files -> VHDL File。

贴入 zhidao_vhdl.txt 中的代码

下面给出自己学习当中的课程实验相关代码:三八译码器

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

-

- ENTITY zhidao IS

- PORT(

- x: IN STD_LOGIC_VECTOR(7 DOWNTO 0);

- y: OUT STD_LOGIC_VECTOR(2 DOWNTO 0)

- );

- END zhidao;

-

- ARCHITECTURE tt OF zhidao IS

- BEGIN

- PROCESS(x)

- BEGIN

- CASE x IS

- WHEN "11111110" => y <= "000";

- WHEN "11111101" => y <= "001";

- WHEN "11111011" => y <= "010";

- WHEN "11110111" => y <= "011";

- WHEN "11101111" => y <= "100";

- WHEN "11011111" => y <= "101";

- WHEN "10111111" => y <= "110";

- WHEN "01111111" => y <= "111";

- WHEN OTHERS => y <= "XXX";

- END CASE;

- END PROCESS;

- END tt;

(注意:实体名保持一致)保存文件为 zhidao.vhd 到之前选择的工程目录下(D:/zhidao)

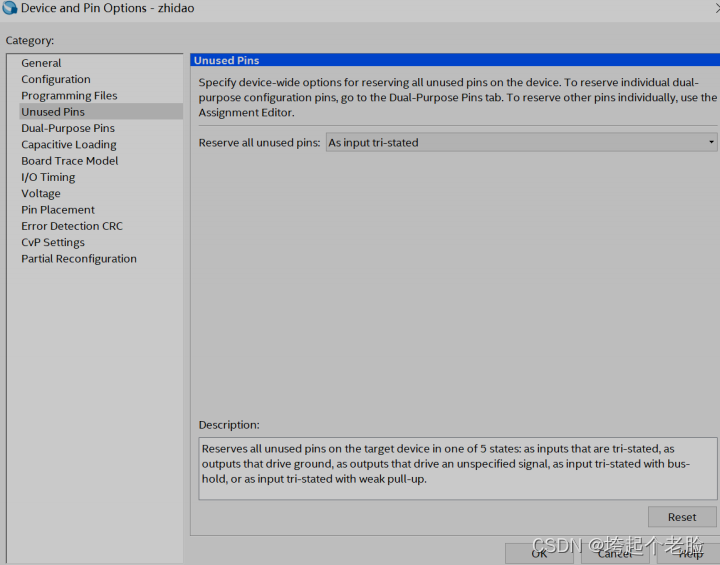

菜单 Assignments->Device,点击 Device and Pin Options

在 Unused Pins 里,选择 As input tri-stated,

将其它未使用的引脚 状态设置为三态输入

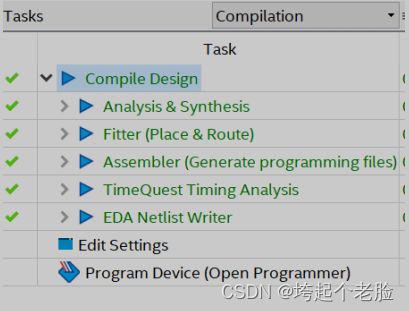

在 Task 栏里双击 Compile Design,全部绿色对勾编译通过

3.3 仿真

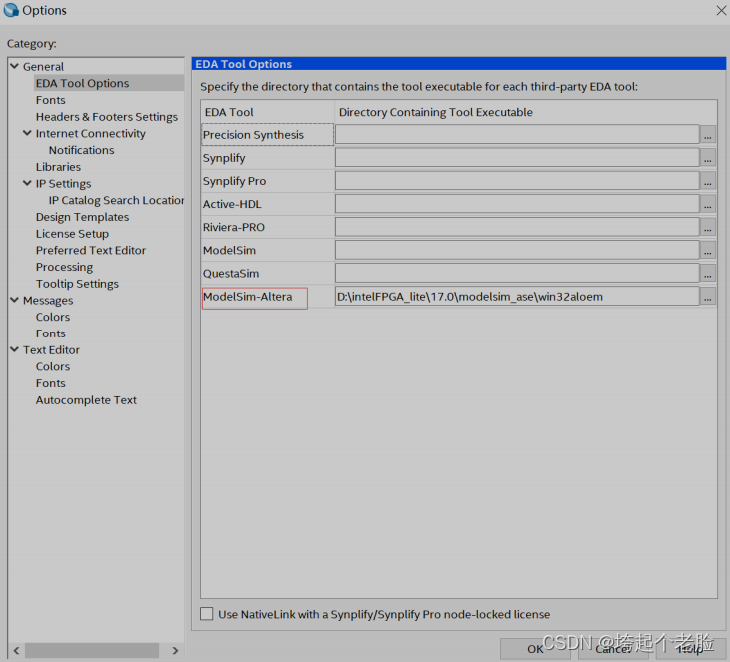

菜单 Tools->Options,General->EDA Tool Options 中设置好 ModelSim Altera 可执行程序的路径(

注意不要设置为倒数第三项 ModelSim)

菜单 Processing->Start->Start Test Bench Template Writer,在工程文件夹 simulation/modelsim下自动生成了Test Bench 模 板 zhidao.vht

直接用 Quartus 打开上一步生成的文件 zhidao.vht。(File->Open 找到 并打开文件,需要选择 All Files 才能看到 .vht 文件)

将 init:PROCESS 和 always:PROCESS 两个进程删除(从 init:PROCESS一直到 END PROCESS always)

将 zhidao_vht.txt 中的 init:PROCESS 和 always:PROCESS 两个进程的代码复制到原处,保存文件。

(进程 init 用来描述一般的输入信号,按顺序书写各个输入信号的变化即可,需要等待一段时间则利用 wait for 语句)

(进程 always 用来描述时钟信号之类的周期信号,在此进程中添加语句后需要删除最后的一句 wait,从而使此进程能够反复循环执行)

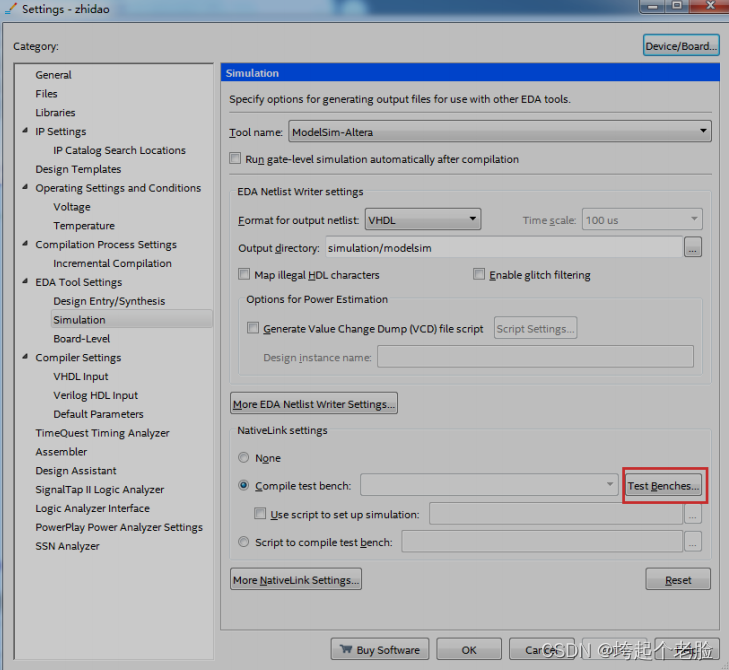

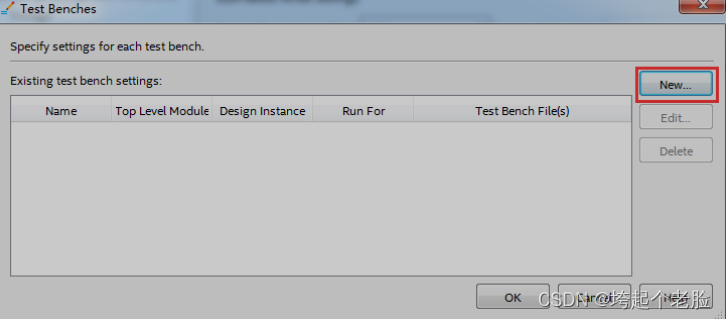

菜单 Assignments->Settings,EDA Tool Settings->Simulation 中,在 NativeLink settings 里选中 Compile test bench,点击后面的 Test Benches 按钮

在弹出的 Test Benches 选项卡里点 New

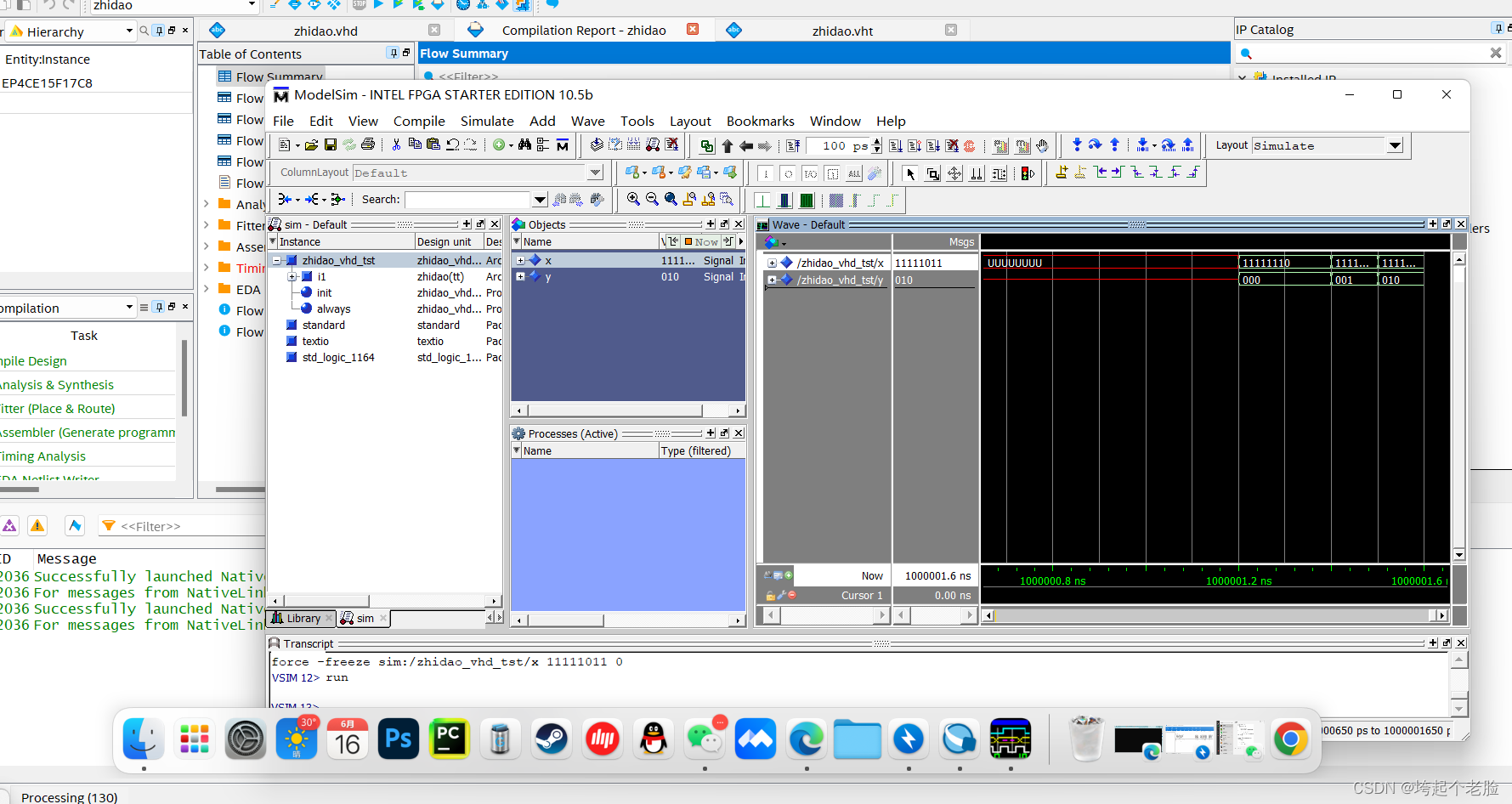

Test bench name 输入 zhidao_vhd_tst、End simulation at 设置为 1ms

最下方 Test bench files 里把 simulation/modelsim 下的 zhidao.vht 添加进去。点击 OK 设置完毕

菜 单 Tools->Run RTL Simulation 会自动打开 ModelSim 并 运 行TestBench 得到仿真结果

注意

是不是有手就行?

注意!!!!

每进行一个项目,必须按照相应的流程重新操作,切不可复制新代码到源文件,否则将会报错

(本文源于学校课程学习研究总结内容)

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小舞很执着/article/detail/832293

推荐阅读

相关标签