- 1Android学习之使用正则表达式Pattern与Matcher来判断字符串格式_android patterns 判断问题

- 2MATLAB——数据归一化处理(normalize函数)_matlab归一化函数normalize

- 3HarmonyOS 基础组件-button_harmonyos button文本属性

- 4机器视觉公司_成都机器视觉有限公司

- 5jieba库中基于 TextRank 算法的关键词抽取——源代码分析(一)_jieba textrank

- 6Windows下新建和更改分区

- 7JVM的知识

- 8独家 | 使用Python的LDA主题建模(附链接)

- 9大学物理·第4章刚体的转动_刚体同时参与两个轴的转动

- 10正斜杠(/)与反斜杠(\)总结

DP Alt Mode(Alternative Mode)

赞

踩

一、Type-C的DP AlT Mode

Type-C 上 配置 Alternative Mode(Alt Mode)。这种配置可以使得其他协议比如DP、HDMI、Thunderbolt™、MHL(mobile high-definition link),以及PCIe等在 Type C线缆上传输。以最流行的DP为例:

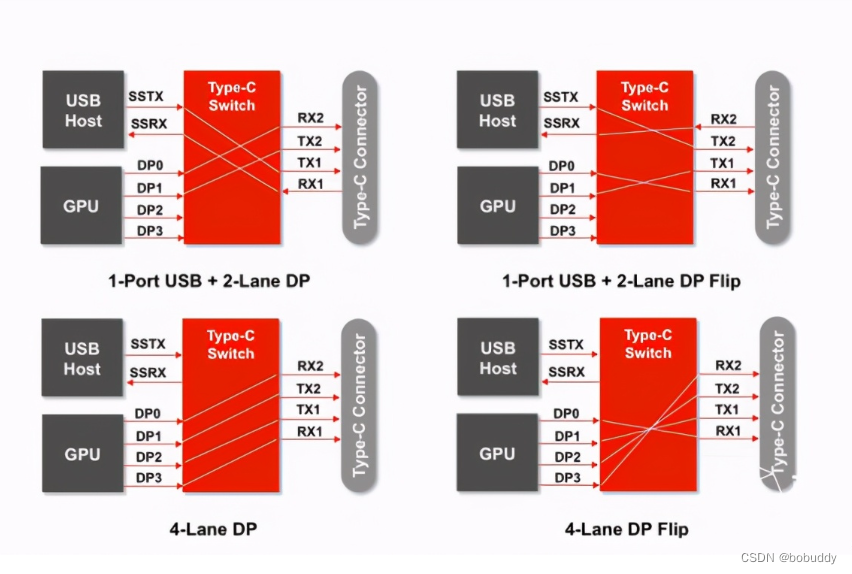

DP Alt Mode 2Lane ,针脚功能如下:

DP Alt Mode 4Lane(此时只能拥有USB2.0) ,针脚功能如下:

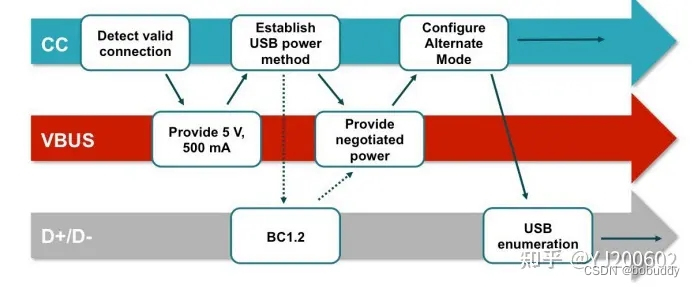

DP Alt Mode触发配置流程

1. USB connection is detected via a CC connection.

2. The default power of 5 V at 500 mA becomes available on the VBUS pin.

3. Either Battery Charging 1.2 (BC 1.2) or USB PD can be used to further negotiate the USB PD to the desired power over VBUS.

4. USB PD is needed to use structured vendor-defined messages (VDM) to negotiate the Alt Mode handshaking.

5. USB enumeration.

6. If DP Alt Mode negotiation is completed, proceed with the DP link training to establish the DP link. 7. USB and DP channels are ready for data and video transfer over Type-C.

TypeC的“备用模式”(Alt Mode)。绝大多数C口能输出视频的设备,都是通过DP Alt Mode进行的。在这种模式下,DP信号可以选择占据8条车道中的一半或者全部。因为显示信号只有一个方向,所以每2根信号线就组成一个DP通道。

DP1.2每通道最多5.4Gbps,DP1.3每通道最多8.1Gbps。而4K60帧的带宽需求是12.54Gbps。所以对于DP1.2的设备来说,4K60就需要占满全部8条车道。(其实6条就够了,但DP没有3通道的配置,USB3也没有半双工模式)USB只能走旧的USB2.0通道。而DP1.3及以上的设备,就可以只占一半,把另一半留给单通道模式的高速USB

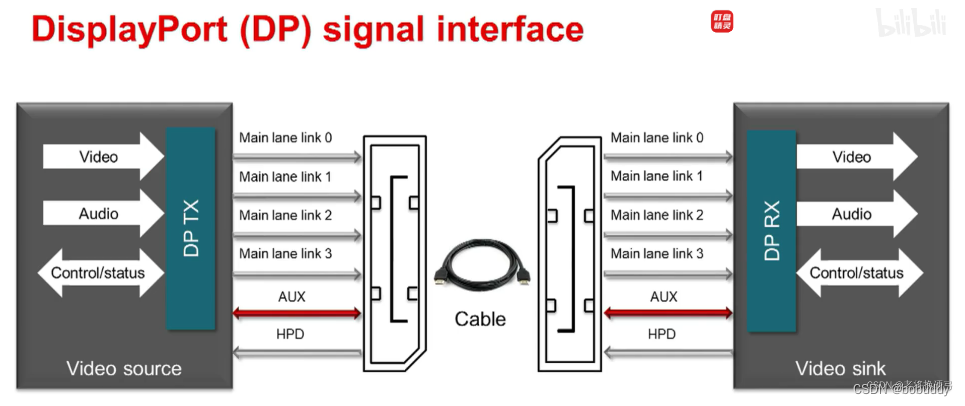

DP接口(DisplayPort)是一种图像显示接口,它不仅可以支持全高清显示分辨率(1920×1080),还能支持4k分辨率(3840×2160),以及最新的8k分辨率(7680×4320)。DP接口不仅传输率高,而且可靠稳定,其接口传输的信号由传输图像的数据通道信号以及传输图像相关的状态、控制信息的辅助通道信号组成,具体包含DisplayPort数据传输主要通道(Main Link)、辅助通道(AUX Channel)与连接(Link Training)

显示接口的概述

1.主链路:主链路是单向的、高带宽、低延迟的信道,用于传输同步串行数据流,如未压缩的视频和音频。

2. 辅助通道(AUX CH):辅助通道是1Mbit/s半双工,双向通道,用于链路管理(状态信息)和设备控制。

3. 热插拔检测(HPD)信号线:HPD信号是sink to source的信号,一是用作sink的检测,接3.3V或拉高说明sink存在,拉低超过2ms说明sink不存在;也可以作为sink设备的中断请求,当拉低0.5ms~1ms时,说明sink设备发出中断,此时source通过AUX读取sink的DPCD寄存器获知中断类型。

此外,DP连接器为盒到盒连接有一个电源引脚为本地设备供电。

AUX Channel-辅助通道

DP设有专用总线,即AUX Channel,用于source和sink之间的握手。因为source是过程的控制装置,它为sink提出请求。sink与source进行通信的唯一途径是在热插拔检测(HPD)信号中发出一个脉冲。

因为AUX Channel是source / sink通信的关键部分,所以理解握手过程的核心在于记录AUX Channel通信。AUX Channel Monitor工具是所有DP协议相关工程师和设计师必须配备的设备。

辅助通道(AUX Channel)作为DP接口中一条独立的双向传输辅助通道,采用交流耦合差分传输方式,是一条双向半双工传输通道,单一方向速率仅1Mbit/s左右,用来传输设定与控制指令。

AUX(Auxiliary)的用途包括读取扩展显示识别数据(EDID),以确保DP信号的正确传输;读取显示器所支持的DP接口的信息,如主要通道的数量和DP信号的传输速率;进行各种显示组态暂存器的设定;读取显示器状态暂存器。

接收(sink)设备可以切换HPD信号来提示源设备启动一个AUX请求事务来读取DPCD链接/接收状态寄存器位,包括IRQ_HPD向量寄存器位。

因此,只有先保证AUX的信号正确才能使DP接口的信号正确传输,而不同DP协议的液晶模组对AUX输出信号的幅值有不同的要求。目前,在液晶模组检测设备对液晶模组进行检测时,针对不同DP协议的液晶模组,需要设计各种AUX输出幅值相匹配的液晶模组测试装置,明显提高了液晶模组的测试成本。

DPCD :DisplayPort Configuration Data

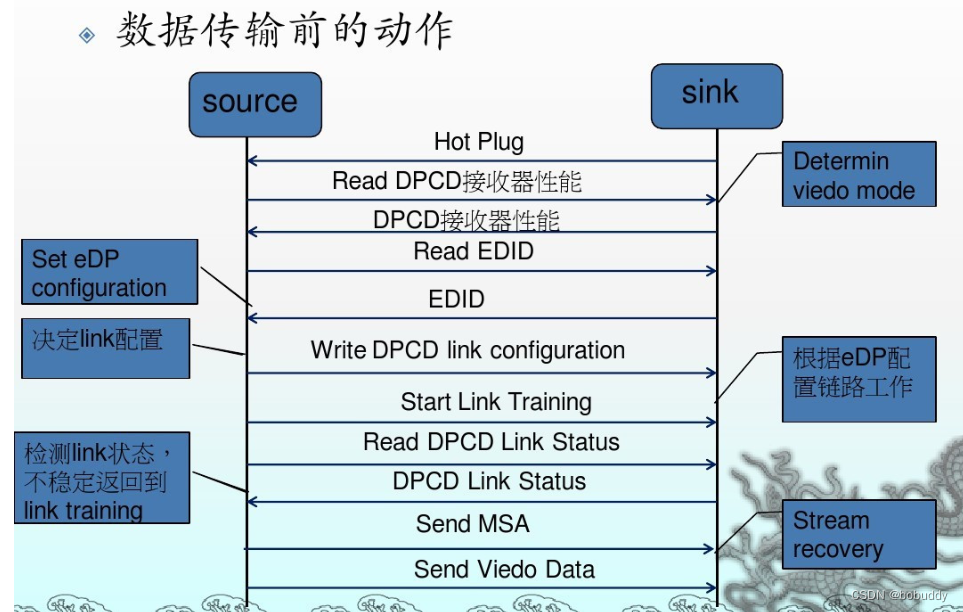

DP source和sink之间的信息传送通过对sink上的DisplayPort配置数据(DPCD)寄存器进行读写来实现。

通过读取DPCD中的特定寄存器,source将知晓sink的性能。在建立数据link,即link训练期间,source对DPCD进行写操作,以指明目标link的配置,另外sink也将各个link训练阶段的结果写到此处。

在数十个DPCD寄存器中调用每个位的详细含义非常具有挑战性。因此,对于DP调试程序的生产率来说重要的是,所用工具能够轻松地根据VESA DP技术规范等标准的常用术语解析AUX读写操作中的DPCD内容。

EDID

扩展显示标识数据(EDID)是一个结构化数据块,定义了DP接收装置的性能。它定义了构造、型号名称、屏幕尺寸和颜色格式。在连接到sink之后,source首先要执行的操作之一就是读取sink的EDID数据。

对DP source和sink之间的通信起到重要作用的是EDID定义了sink以及sink支持的视频模式的原始分辨率。在选择将要发送给sink的内容的格式时,该数据是source的基础。分辨率、所用视频模式、颜色格式、音频格式等。

通过改变测试sink的EDID,工程师可以轻松验证sink的灵活性。易于使用的EDID编辑器可向用户说明各个比特位,是另外一种非常重要且节省时间的工具。

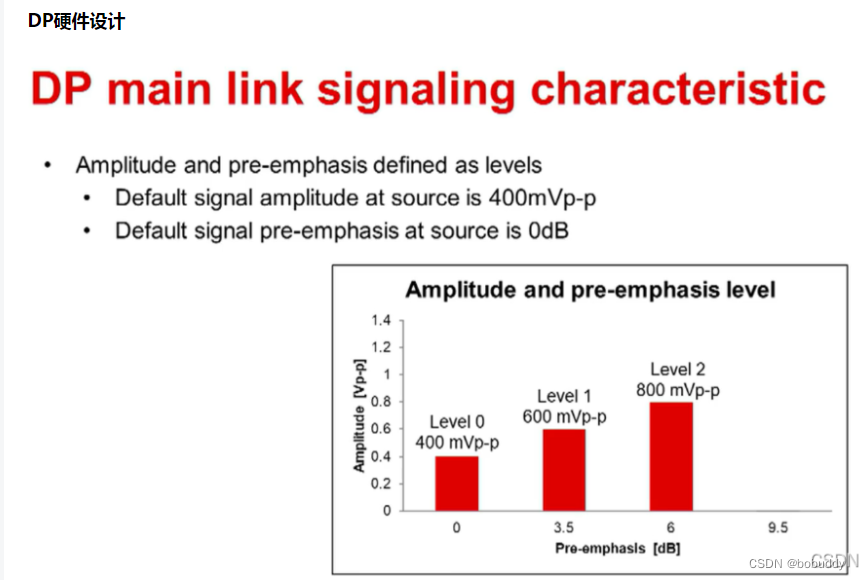

主Link配置

根据source需要发送给sink的内容以及从EDID和DPCD读取来的sink性能,source可确定发送内容的格式以及用于传输的数据link配置。一个良好设计的source将尝试优化link的使用,以达到将功耗降至最低等目的。因此其目标是使用尽可能少的信道和尽可能低的电压摆动。

在link训练期间,source使用其首选配置启动实际训练过程,在link建立之前通过迭代法对其进行改变。一旦link建立,source便可开始发送内容本身。

用户可以在AUX Channel Monitor的帮助下评估通信记录,进而验证link培训过程是如何执行的。此外,工具的易用性将有助于工程师保持注意力集中。因为一对具有多流功能的source和sink之间的link训练过程可包含上百个读写操作,诸如突出显示数据以便于阅读、过滤数据以专注于基础数据等功能至关重要。

通过改变sink或source的性能因素,工程师可以验证其DUT sink或DUTsource是否按预期工作。VESA定义的Link Compliance Test中的各种测试事实上可验证sink或source是否按实现良好互操作性所需的方式进行工作。一个良好的工具允许编辑和保存性能数据,供以后使用。

MSA和SDP

在内容传输期间,source还发送额外数据:主数据流属性(MSA)和可选的次级数据包(SDP)。

MSA是source向sink通知其提供的视频模式详细信息的途径。工程师的一项任务是验证MSA与实际视频模式是否匹配。

SDP可包含多媒体内容的音频部分以及所谓的INFOFRAMES。INFOFRAMES是定义视频和音频结构的数据——sink进行解读的方式。工程师将进行相同任务:验证发送的数据与内容是否匹配。

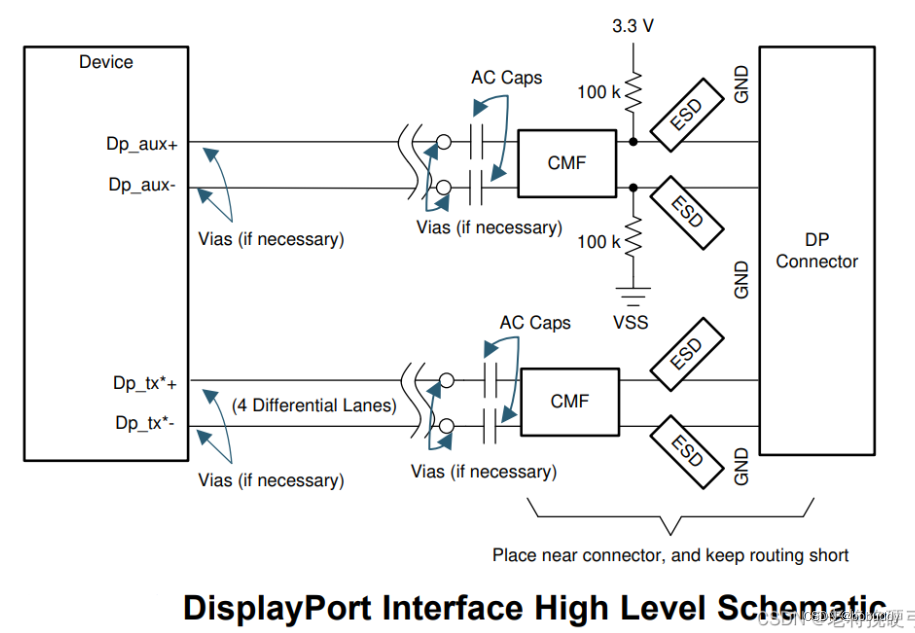

DP信号是一个交流耦合、100欧姆的差分信号接口,下图是一个典型的DP电路设计图示。交流耦合电容必须添加,推荐封装0402;共模电感的选择要注意其是否支持足够高的数据速率;ESD尽量选择寄生电容小的器件

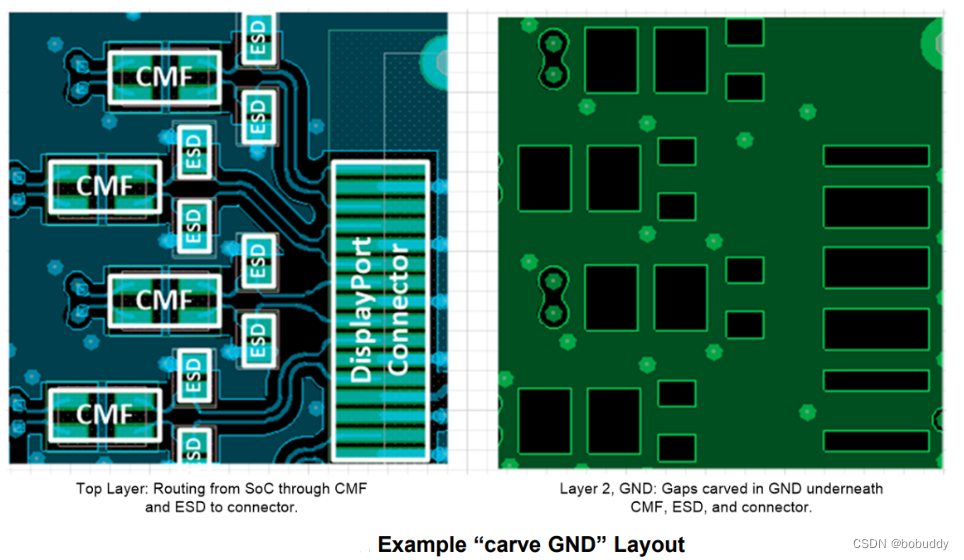

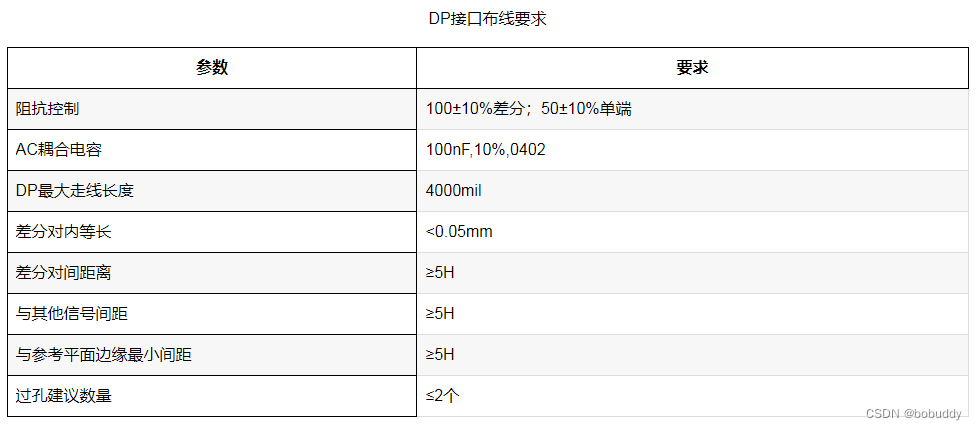

DP接口Layout设计

除以上表中基本要求外,在设计时也要注意如下几个问题,

尽量缩短走线长度,远离开关电源、晶振等噪声源;

建议在信号线换层孔附近添加回流孔,尽量减少换层孔;

信号走线优先参考GND层,并保证参考平面完整。如果设计中无法避免跨平面参考,建议再跨平面分割处用旁路电容将回流信号连接起来;

差分耦合电容、共模电感和ESD等器件尽量靠近DP座并对称放置;

DP座上机壳地与数字地完全分开单点连接;

另,由于元器件的PAD width会导致阻抗不连续,因此建议在元器件pad下方的参考层挖空以减小阻抗的不连续性。下图为Layout的一个例子。