- 1【AI绘画】Stable Diffusion复现——基于 Amazon SageMaker 搭建文本生成图像模型_使用 amazon sagemaker 构建高质量 ai 作画模型 stable diffusion

- 2关于项目管理和项目经理的一些讨论

- 3win10 装SQL Server 2000入门各种坑_sql2000-kb884525-sp4-x86-chs.exe

- 4Hadoop环境搭建(全网最详细,保姆级教程)

- 5Unity AR

- 6Spark学习之RDD编程总结_rdd实验报告心得

- 7vmware下linux虚拟机找不到eth0网卡

- 8数据结构与算法之美学习笔记:不定期福利第一期 | 数据结构与算法学习书单

- 9LangChain 联合创始人下场揭秘:如何用 LangChain 和向量数据库搞定语义搜索?

- 10MySQL安装配置教程(超级详细、保姆级)_mysql超详细安装配置教程(保姆级)_mysql安装及配置超详细教程-csdn博客

【mcuclub】时钟模块DS1302

赞

踩

一、实物图

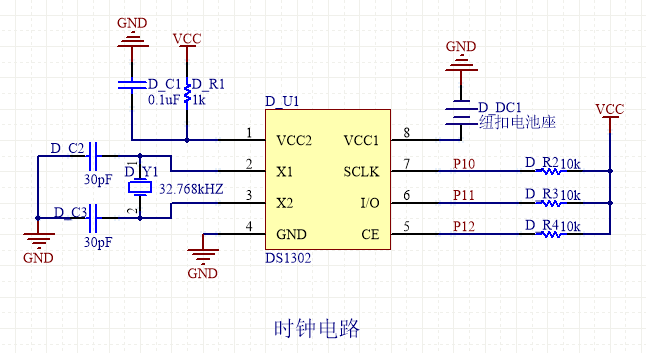

二、原理图

| 编号 | 名称 | 功能 |

| 1 | VCC2 | 双供电配置中的主电源供应引脚。DS1302工作于 VCC1和VCC2中较大者.当VCC2比VCC1高0.2V 时,VCC2 给 DS1302供电。当VCC1比VCC2高时, VCC1给DS1302供电 |

| 2 | X1 | 32.768kHz晶振引脚 |

| 3 | X2 | |

| 4 | GND | 电源地 |

| 5 | CE | 使能引脚。输入信号,在读、写数据期间,必须为高。该引脚有两个功能:第一,CE开始控制字访问移位寄存器的控制逻辑;其次,CE提供结束单字节或多字节数据传输的方法 |

| 6 | I/O | 数据输入/输出引脚。三线接口时的双向数据线 |

| 7 | SCLK | 串行时钟引脚, 用来同步串行接口上的数据动作 |

| 8 | VCC1 | 备用电源引脚。在使用涓流充电的系统中,这个管脚连接到可再充能量源 |

电路图中一些电阻电容作用:

VCC2引脚的电容主要用于滤波,而串联一个电阻可以有效防止电源对芯片的冲击。

晶振两端的电容主要用于起振的,如果不接,会导致时间快几秒,但是时间的精确性主要取决于晶振频率。

VCC1接的是一个纽扣电池,当VCC2的电源断电时,VCC1给芯片供电,这样时钟就会继续运行。

三个上拉电阻作用:

DS1302的数据脚(I/O)是双向的,如果只用单片机弱上拉,双向通讯不成功,可能是因为弱上拉时端口电平翻转慢,造成读数不准。

CE脚和SCLK脚是单向的,可以不用接上拉电阻,单片机弱上拉是可以的。

晶振为什么选取32.768kHz:

时钟系统中,秒是一个重要的时间单位,1秒正是1Hz,如果要提高时间精度,那这个1Hz必须要准确。我们知道,在数字世界里,只有0和1两种可能,下面看一个计算:2^15 = 32768 = 32.768K

2的15次方正好等于32768,反过来讲,如果要把32.768K的时钟频率经过15次分频的话,得到的频率正好是1Hz。所以时钟芯片内部经过15次分频就得到了1Hz,即1s。

三、简介

DS1302 是美国DALLAS公司推出的一种高性能、低功耗、带RAM的实时时钟电路,它可以对年、月、日、周、时、分、秒进行计时,具有闰年补偿功能,工作电压为2.0V~5.5V。采用三线接口与CPU进行同步通信,并可采用突发方式一次传送多个字节的时钟信号或RAM数据。DS1302内部有一个31×8的用于临时性存放数据的RAM寄存器。DS1302是DS1202的升级产品,与DS1202兼容,但增加了主电源/后备电源双电源引脚,同时提供了对后备电源进行涓细电流充电的能力。

四、内部框图

五、通信协议

DS1302的通信是SPI的变异种类,它用了 SPI 的通信时序,但是通信的时候没有完全按照 SPI 的规则来。SPI接口是以主从方式工作的,这种模式通常有一个主器件和一个或多个从器件,其接口包括以下四种信号:

1、MOSI – 主器件数据输出,从器件数据输入

2、MISO – 主器件数据输入,从器件数据输出

3、SCLK – 时钟信号,由主器件产生

4、/CS – 从器件使能信号,由主器件控制

而DS1302是三种信号,其中I/O替代了MOSI和MISO,利用1根数据线进行数据输入和输出。

六、寄存器地址定义

该寄存器显示了时钟的地址信息,操作时往对应的地址写入值就行,也就是说如果想写入秒,往对应的寄存器写入0x80;表示小时的地址的第7位可选为12小时制还是24小时制,WP是写保护位

时钟暂停标志(CH):

秒寄存器的位7被定义为时钟暂停标志,当此位置1时,时钟振荡器暂停,DS1302进入漏电流小于100nA的低功耗备用模式;当此为置0时时钟开始,初始加电状态未定义。

写保护位(WP):

控制寄存器的位7是写保护位,前7位(位0至位6被强制为0且读取时总是读0,在任何对时钟或RAM的写操作以前,位7必须为0;当为高时,写保护位禁止任何寄存器的写操作,初始加电状态未定义;因此,在试图写器件之前应该清除WP位。

命令字:

命令字启动每一次数据传输时需要配置,第7位固定为1,如果是0则禁止对DS1302的写入,第6位写1则是读取或写入RAM区,写0则读取或写入时钟,第1~5位是地址,即要操作的地址,秒的地址是从0开始;第0位置1是read,对地址进行读取,置0是write,对地址进行写入

例如要读取月信息,则往命令字寄存器写0x89,如要写入月信息,则往命令字寄存器写0x88,对应了RTC左边的地址。

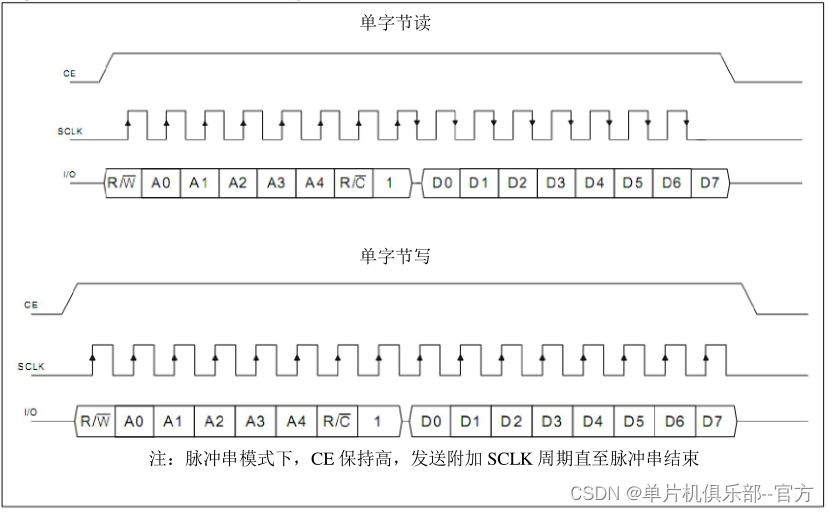

七、时序解析

CE输入驱动高启动所有的数据传输。CE输入有两个功能。首先,CE打开控制逻辑,允许访问的移位寄存器的地址/命令序列。其次,CE提供了一个终止单字节或多字节数据传输方法。

一个时钟周期是由一个下降沿之后的上升沿序列。对于数据传输而言,数据必须在有效的时钟的上升沿输入,在时钟的下降沿输出。如果CE为低,数据传输终止。

对于数据输入︰

开始的8个SCLK周期,输入写命令字节,数据字节在后8个SCLK周期的上升沿输入。数据输入位0开始。

代码如下:

void Ds1302_Write_Byte(uchar addr, uchar dat)

{

uchar i;

DS1302_CE = 1; //启动DS1302总线

//写入目标地址:addr

addr = addr & 0xFE; //最低位置0,寄存器0位为0时写,为1时读

for(i = 0; i < 8; i++)

{

DS1302_IO = addr & (0x01 << i);

DS1302_SCLK = 1;

DS1302_SCLK = 0;

}

//写入数据:dat

for(i = 0; i < 8; i++)

{

DS1302_IO = dat & (0x01 << i);

DS1302_SCLK = 1;

DS1302_SCLK = 0;

}

DS1302_CE = 0; //停止DS1302总线

}

对于数据输出︰

开始的8个SCLK周期,输入一个读命令字节,数据字节在后8个SCLK周期的下降沿输出。注意,第一个数据字节的第一个下降沿发生后,命令字的最后一位被写入。当CE仍为高时。如果还有额外的SCLK周期,DS1302将重新发送数据字节,这使DS1302具有连续突发读取的能力。

代码如下:

uchar Ds1302_Read_Byte(uchar addr)

{

uchar i,dat = 0x00;

DS1302_CE = 1; //启动DS1302总线

//写入目标地址:addr

addr = addr | 0x01; //最低位置1,寄存器0位为0时写,为1时读

for(i = 0; i < 8; i++)

{

DS1302_IO = addr & (0x01 << i);

DS1302_SCLK = 0;

DS1302_SCLK = 1;

}

//输出数据:dat

for(i = 0; i < 8; i++)

{

DS1302_SCLK = 1;

DS1302_SCLK = 0;

if(DS1302_IO)

dat |= (0x01 << i);

}

DS1302_CE = 0; //停止DS1302总线

DS1302_IO = 0; //读取后将IO设置为0,否则读出的数据会出错

return dat;

}

八、BCD码

BCD码(Binary Coded Decimal),用4位二进制数来表示1位十进制数

例:0001 0011表示13,1000 0101表示85,0001 1010不合法

在十六进制中的体现:0x13表示13,0x85表示85,0x1A不合法

BCD码转十进制:DEC=BCD/16 * 10+BCD%16; (2位BCD)

十进制转BCD码:BCD=DEC/10 * 16+DEC%10; (2位BCD)

因为时钟芯片内存放的是BCD码,所以直接读取出来的话会不准确,要转为十进制来显示。

九、流程设计

首先初始化引脚,然后初始化DS1302,设置CE为高,设置是读操作还是写操作,然后写入8位目标地址,接下来如果是写操作,则写入数据,如果是读操作,则读取数据,最后设置CE为低,结束操作。