- 12022-4-27-Linux配置网络和主机_2022网络连接配置

- 2基于微信小程序的失物招领系统的设计与实现_校园失物招领小程序的设计与实现

- 3链表常见面试题( 建议收藏!!)_链表面试题

- 4vmware安装安卓9.0测试_vmware 安装安卓9

- 5python读取.nc数据_python netcdf4读取nc csdn

- 6安装Adobe全家桶时出现The installation cannot continue as the installer file may be damaged.解决方法。

- 7【Unity入门】详解Unity中的射线与射线检测_unity 射线

- 8【机器学习300问】79、Mini-Batch梯度下降法的原理是什么?

- 9基于Java的XxlCrawler网络信息爬取实战-以中国地震台网为例_xxlcrawler 数据抽取方式 含义

- 10计算机毕业设计hadoop+spark知识图谱视频推荐系统 视频分析可视化大屏 视频爬虫 视频大数据分析 大数据毕业设计 机器学习 深度学习 人工智能

STM32——ADC_stm32 adc

赞

踩

一、ADC原理

ADC——Analog to Digital Converter,即模数转换器,是将连续的模拟信号转换为离散的数字信号的器件。由于数字信号本身不具有实际意义,仅仅表示一个相对大小。故任何一个模数转换器都需要一个参考模拟量作为转换的标准,比较常见的参考标准为最大的可转换信号大小。而输出的数字量则表示输入信号相对于参考信号的大小。 它的一般工作过程为:采样——保持——量化——编码。

1、采样与保持

采样:由于模拟信号是连续的,数字信号是离散的,因此我们需要对模拟信号按照一定的采样频率进行采样得到离散的信号。那么采样频率是多少呢?根据采样定理:设采样频率为fs,输入的模拟信号的最高频率分量的频率为fmax,则 fs 与 fmax 必须满足以下的关系

fs ≥ 2 fmax

保持:采样所得的信号并不是立马就能转换为数字信号,往往需要一定的时间,因此为了给后续的量化和编码提供一个稳定值,采样的输出就需要保持一段时间。一般采样和保持是同时完成的。

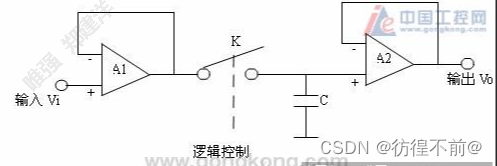

一个简单的采样保持电路和最终得到的输出信号波形如下图所示

t0~t1时段,开关K闭合,电路处于采样阶段,电容器C充电;t1~t2时段为保持阶段,此期间K断开,若A2的输入阻抗足够大,且K为较理想的开关,可认为C几乎没有放电回路,输出电压Vo保持不变。

2、量化与编码

由上图可知,由于采样后的输出需要保持一定的时间,因此经过采样保持后的输出信号,只实现了对输入信号在时间上的离散,在数值上还是连续变化的模拟量。要转换成数字量,还要实现数值上的离散,将取样信号表示为一最小数量单位的整数倍,这一过程称为量化,量化所取得最小数量单位称为量化单位。

量化单位取决于设定的ADC参考电压以及编码的位数。例如一个简单的量化方法为,当ADC的参考电压为0~4V,编码位数为3V,那么量化单位为 4 / (2^3) = 0.5V。那么就有

| 采样电压值 | 量化值 | 编码值 |

| 0~0.5V | 0V | 000 |

| 0.5~1V | 0.5V | 001 |

| 1~1.5V | 1V | 010 |

| 1.5~2V | 1.5V | 011 |

| 2~2.5V | 2V | 100 |

| 2.5~3V | 2.5V | 101 |

| 3~3.5V | 3V | 110 |

| 3.5~4V | 3.5V | 111 |

这里的量化方法采取的是舍尾取整法,可以看到会有一定的误差,此误差称为量化误差,是不可避免的。还有一种更好的方法降低了误差,并且为大多数ADC转换器所采用,叫做四舍五入法,这里就不过多提及了。

3、主要技术指标

(1)分辨率

说明ADC转换器对输入信号的分辨能力。可以用编码的位数来表示,也可以用转换器能区分出输入信号的最小电压来表示。在最大输入电压(参考电压)一定时,输出位数越多,量化单位越小,分辨率越高。例如ADC转换器输出为8位二进制数,参考电压为5V,那么这个转换器能区分出输入信号的最小电压为19.53mV。

(2)转换时间

转换时间是指ADC转换器从转换控制信号到来开始,到输出端得到稳定的数字信号所经过的时间。ADC转换器的转换时间与转换电路的类型有关,不同类型的转换器速度相差甚远。

4、逐次比较型ADC转换器

ADC的一般过程为采样、保持、量化、编码,但是为了减少转换的误差,提高精度,有一些转换器的保持、量化和编码过程并不是上述所说的原理,例如逐次比较型ADC转换器,可参考

(126条消息) 逐次比较型SAR ADC工作原理_稳定性与频率补偿的博客-CSDN博客_逐次比较型ad转换器

总结:逐次比较型ADC转换器的完成一次转换所需的时间(即转换时间)与编码的位数和进入ADC转换器的时钟频率有关,若是8位,则转换时间为8个时钟周期,若是12位,则转换时间为12个时钟周期。位数越少或者时钟频率越高,转换时间越短。

二、STM32ADC模块

STM32各系列ADC的主要特性

| 主要特性 | F1 | F4 | F7 | H7 |

| ADC类型 | 逐次逼近型 | |||

| 分辨率 | 12位 | 6/8/10/12位 | 6/8/10/12位 | 8/10/12/14/16位 |

| ADC时钟频率 | 14MHz(Max) | 36MHz(Max) | ||

| ADC时钟频率是可分频的,这只是规定的最大时钟频率,具体每个芯片的最大时钟频率要查看相应的数据手册 | ||||

| 采样周期 | 采样周期越长,转换结果越准确,但是转换时间会变长 | |||

| 转换时间 | 与时钟频率、分辨率和采样周期有关 | |||

| 输入通道 | 16个GPIO复用外部通道和2个内部通道(温度传感器和V REFINT) | 16个GPIO复用外部通道和3个内部通道(温度传感器、V REFINT和V BAT) | ||

| 中断事件 | 1、转换结束(标志位EOC,可以是规则组转换结束也可以是注入组转换结束); 2、注入组转换结束(标志位JEOC) 3、设置了模拟看门狗状态位(标志位AWD) | 1、转换结束(标志位EOC,可以是规则组转换结束也可以是注入组转换结束); 2、注入组转换结束(标志位JEOC) 3、设置了模拟看门狗状态位(标志位AWD) 4、DMA溢出(标志位OVR) | ||

1、ADC开关控制

可通过将 ADC_CR2 寄存器中的 ADON 位置 1 来为 ADC 供电。首次将 ADON 位置 1 时,

会将 ADC 从掉电模式中唤醒。也可通过将 ADON 位清零来停止转换并使 ADC 进入掉电模式。在此模式下,ADC 几乎不耗电(只有几 μA)。

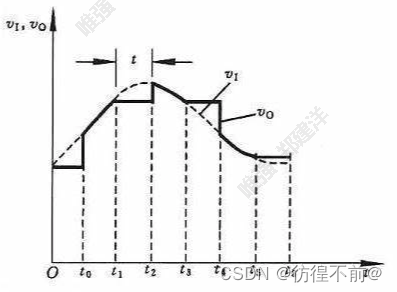

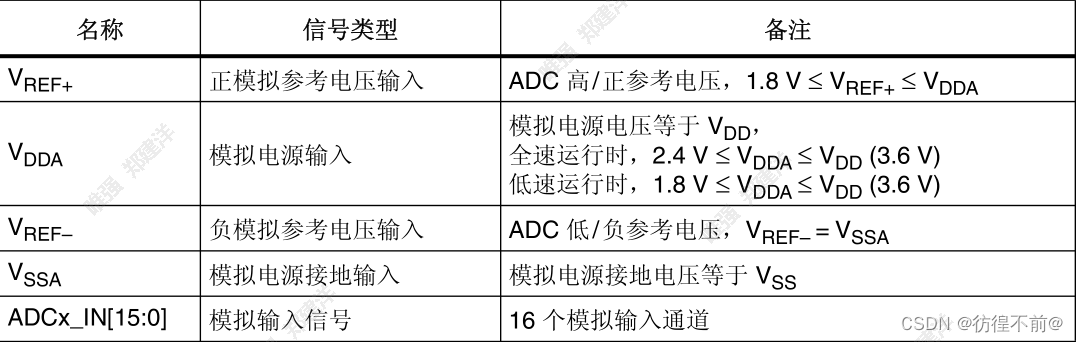

2、ADC引脚

如图是STM32F429中ADC模块的引脚,分为三个部分,红色框住的是参考电压引脚和器件工作所需电压的引脚;

蓝色和紫色框住的是ADC的通道,每个ADC具有多达19个复用通道,可测量来自16个外部源(蓝色框住的,测量从GPIO端口输入的信号)、两个内部源和VBAT通道的信号(紫色框住的,是内部已经接好了的内部输入信号通道)。

ADC需要一个参考电压,然后在转换时根据参考电压和分辨率对数据进行量化编码,参考电压引脚为 VREF+ 和 VRAEF- ;VDDA就是ADC转换器件需要提供的电压,VSSA就是模拟电源接地。

在数据手册和参考手册中我们可以找到关于ADC电源引脚的特性,因此在开发板中我们一般是将VSSA和VRAEF-接地,VDDA接3.3V,然后VREF+与VDDA接在一起,即参考电压为3.3V。

2、ADC时钟

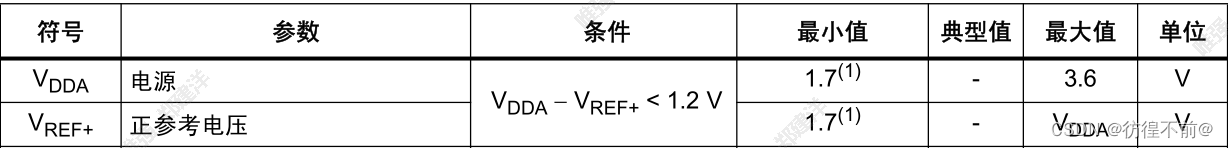

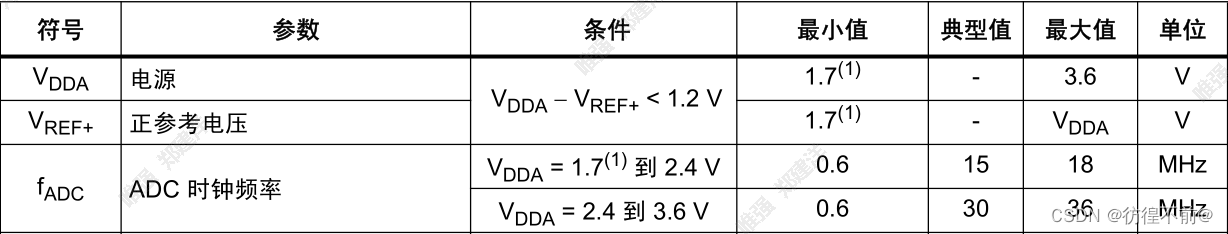

首先我们要看一下STM32F429的数据手册中ADC的特性

由于VDDA接到了3.3V,因此我们可以看到ADC的时钟频率典型值为30MHz,最大值为36MHz。

但是这些都是一个器件的一个理论值,实际上我们要看STM32F429中ADC是接在哪个总线上的,并且在ADC框图中找到ADC的输入时钟。

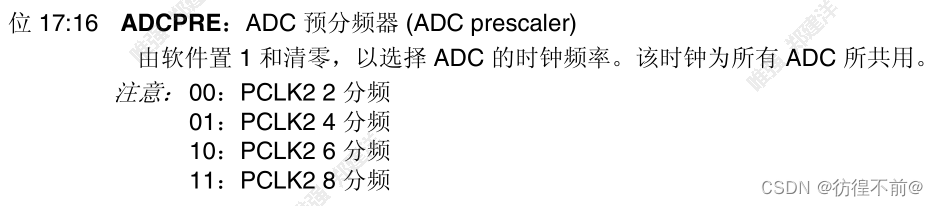

查阅可知ADC是接在APB2 90MHz总线上的,且ADC输入时钟ADCCLK是来源于APB2时钟再分频得到的,分频因子由ADC通用控制寄存器 (ADC_CCR)中位 17:16 ADCPRE 控制。

因此,如果2分频,则ADCCLK的时钟频率为 90 / 2 = 45MHz,但是上面我们说过ADC的时钟频率最大值为36MHz,所以2分频是不行的;同理,4分频,ADCCLK的时钟频率为 90 / 4 = 22.5MHz;6分频,ADCCLK的时钟频率为 90 / 6 = 15MHz;8分频,ADCCLK的时钟频率为 90 / 8 = 11.25MHz。

总结:在STM32F429中ADC的时钟频率最大为22.5MHz,达不到典型值,更达不到最大值。

3、采样时间与转换时间与采样频率

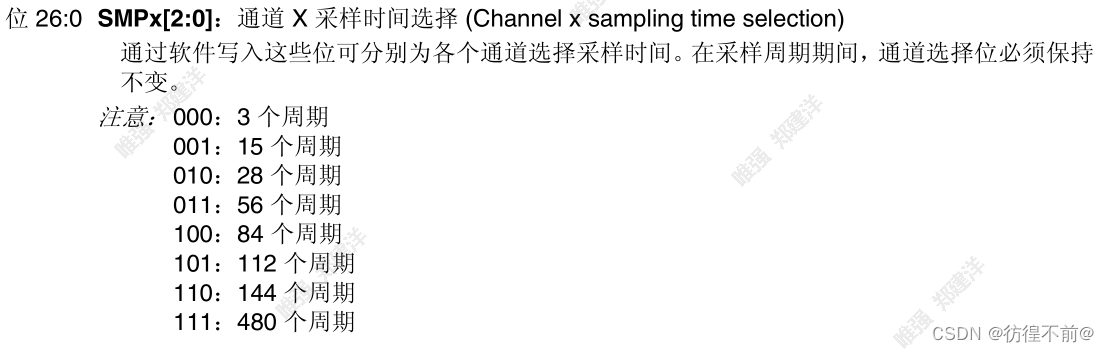

可独立设置各通道采样时间。ADC 会在数个 ADCCLK 周期内对输入电压进行采样,可使用 ADC_SMPR1 和 ADC_SMPR2寄存器中的 SMP[2:0] 位修改周期数。每个通道均可以使用不同的采样时间进行采样。ADC_SMPR2控制的是通道 0~9,ADC_SMPR1控制的是通道 10~18。

采样后,需要电压保持,在保持的同时进行量化编码,由于ADC转换器是逐次比较型转换器,因此完成一次量化编码需要编码位数的个数的周期。例如,分辨率为12位,那么总转换时间的计算公式如下:

T conv = 采样时间 + 12 个周期

示例:

ADCCLK = 22.5 MHz 且采样时间 = 3 个周期时:

最小总转换时间T conv = 3 + 12 = 15 个周期 ≈ 0.67 μs

那么ADC在单重模式下的最大采样频率就为:22.5MHz/15 = 1.5MHz,即采样一次的时间为 2/3 ≈ 0.66666666666us。

4、电压转换

由于ADC 的参考电压范围设定在:0~3.3v,如果设置ADC 为 12位的,那么 12位满量程对应的就是 3.3V,12位满量程对应的数字值是:2^12。数值 0 对应的就是 0V。如果转换后的数值为 X ,X对应的模拟电压为 Y,那么会有这么一个等式成立:

2^12 / 3.3 = X / Y,=> Y = (3.3 * X ) / 2^12

5、规则通道与注入通道

我们上面说了ADC模块有16个外部通道,若是一个通道有输入信号那么我们可以不用管那么多直接进行转换,但是当我们有多个通道有输入信号需要进行转换怎么办?转换的顺序是什么?

在STM32中把这16个外部通道分为规则通道和注入通道,在规则通道里进行规则转换,在注入通道里进行注入转换。

(1)规则转换

规则转换即按照给定的转换顺序进行转换。一个规则转换组最多由 16 个转换构成。如果选定了规则转换,那么我们需要告知ADC转换器的参数就是:需要进行转换的通道数目以及转换的顺序。这些参数我们需要在规则序列寄存器中配置。

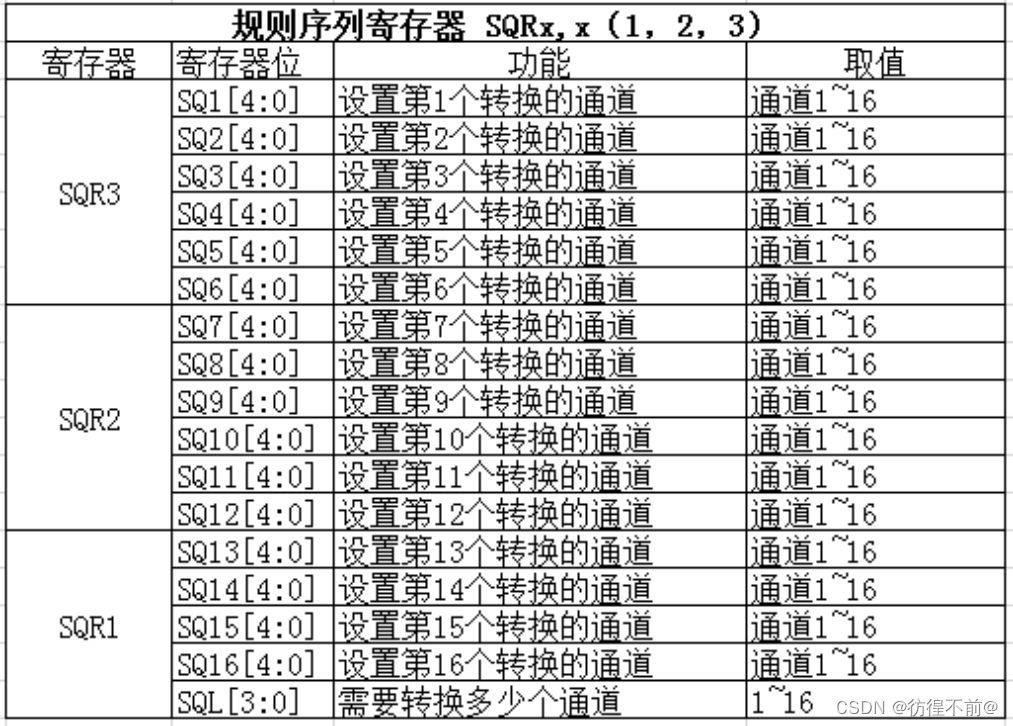

规则序列寄存器有 3 个,分别为 SQR3、SQR2、SQR1。SQR3 控制着规则序列中的第一个到第六个转换,对应的位为:SQ1[4:0]~SQ6[4:0],第一次转换的是位 4:0 SQ1[4:0],如果通道 16 想第一次转换,那么在 SQ1[4:0]写 16即可。SQR2 控制着规则序列中的第 7 到第12 个转换,对应的位为:SQ7[4:0]~SQ12[4:0],如果通道 1 想第 8 个转换,则 SQ8[4:0]写 1即可。SQR1 控制着规则序列中的第 13到第 16个转换,对应位为:SQ13[4:0]~SQ16[4:0],如果通道 6 想第 10 个转换,则 SQ10[4:0]写 6 即可。具体使用多少个通道,由 SQR1的位L[3:0]决定,最多 16 个通道。

(2)注入转换

注入转换可以理解为插入转换,即插队的意思,它在规则通道转换的时候可以强行插入转换。如果在规则通道转换过程中,有注入通道插队,那么就要先转换完注入通道,等注入通道转换完成后,再回到规则通道的转换流程。

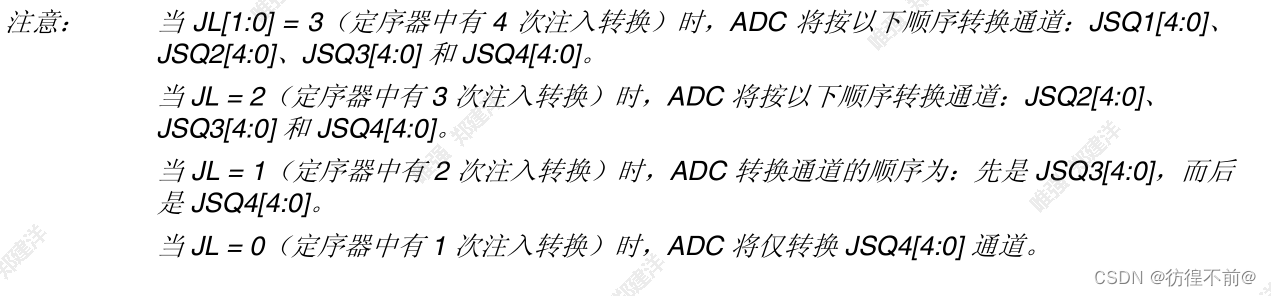

一个 注入转换组最多由 4 个转换构成。它的参数由注入序列寄存器 JSQR 配置,注入序列寄存器 JSQR 只有一个,最多支持 4 个通道,具体多少个由 JSQR的 JL[2:0]决定。如果 JL的 值小于 4的话,则 JSQR跟 SQR决定转换顺序的设置不一样。注入转换组中的转换总数必须写入 ADC_JSQR 寄存器中的 L[1:0] 位。

6、开始转换触发方式

(1)软件触发

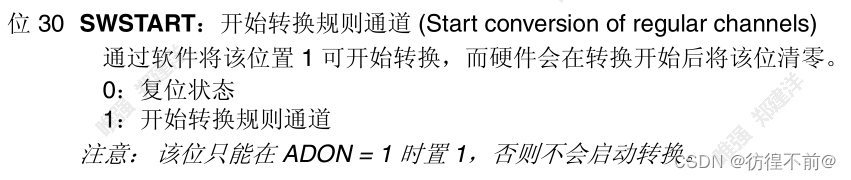

SWSTART 或 JSWSTART 位置 1 时,启动 AD 转换,由ADC 控制寄存器 2 (ADC_CR2)控制。

(2)外部事件触发

6、数据管理

(1)数据存储与数据对齐

转换后的结果存储在数据寄存器中。

来自规则通道的转换结果存储在32位规则数据寄存器 (ADC_DR)中,规则数据寄存器只有一个,数据有左对齐和右对齐两种方式;

来自注入通道的转换结果存储在32位注入数据寄存器中,注入数据寄存器有4个(ADC_JDRx) (x= 1..4),分别对应着各自的通道,数据也有左对齐和右对齐两种方式。

(2)使用DMA

由于规则通道组只有一个数据寄存器,因此,对于多个规则通道的转换,使用 DMA 非常有帮助。这样可以避免丢失在下一次写入之前还未被读出的 ADC_DR 寄存器中的数据。

在使能 DMA 模式的情况下(ADC_CR2 寄存器中的 DMA 位置 1),每完成规则通道组中的

一个通道转换后,都会生成一个 DMA 请求。这样便可将转换的数据从 ADC_DR 寄存器传输到用软件选择的目标位置。

7、转换模式

(1)单次转换

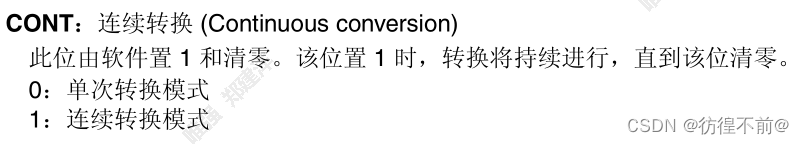

通过CONT位来控制转换模式是单词转换还是连续转换。 在单次转换模式下,ADC 执行一次转换。

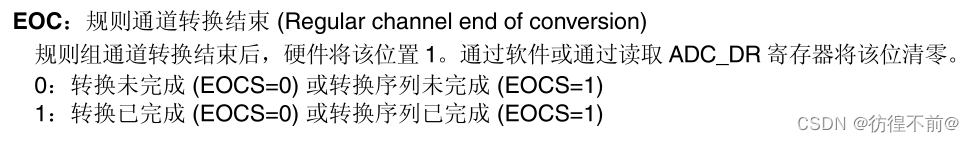

如果是规则通道,转换后的数据存储在16 位 ADC_DR 寄存器中,EOC(转换结束)标志置 1,若EOCIE 位置 1 时将产生中断;

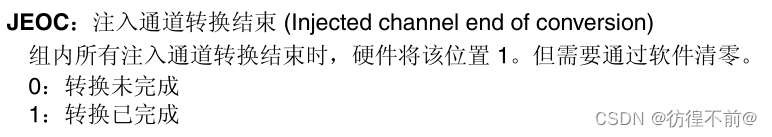

如果是注入通道,转换后的数据存储在 16 位 ADC_JDR1 寄存器中,JEOC(注入转换结束)标志置 1,若JEOCIE 位置 1 时将产生中断;

最后,执行一次转换后,ADC停止。

(2)连续转换

在连续转换模式下,ADC 结束一个转换后立即启动一个新的转换。这个模式只适用于规则通道,不适用于注入通道。每次转换之后,上次转换的数据存储在 16 位 ADC_DR 寄存器中(也就是说不断地会有新的数据覆盖ADC_DR 寄存器),然后EOC(转换结束)标志置 1, 若EOCIE 位置 1 时将产生中断,可在中断中读取ADC_DR 寄存器中的值。

(3)扫描模式

此模式用于扫描一组模拟通道。通过将 ADC_CR1 寄存器中的 SCAN 位置 1 来选择扫描模式。将此位置 1 后,ADC 会扫描

在 ADC_SQRx 寄存器(对于规则通道)或 ADC_JSQR 寄存器(对于注入通道)中选择的所有通道。为组中的每个通道都执行一次转换。每次转换结束后,会自动转换该组中的下一个通道。如果将 CONT 位置 1,规则通道转换不会在组中最后一个所选通道处停止,而是再次从第一个所选通道继续转换。

如果将 DMA 位置 1,则在每次规则通道转换之后,均使用直接存储器访问 (DMA) 控制器将转换自规则通道组的数据(存储在 ADC_DR 寄存器中)传输到 SRAM。

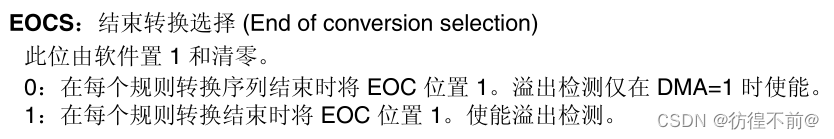

在以下情况下,ADC_SR 寄存器中的 EOC 位置 1:

● 如果 EOCS 位清零,在每个规则组序列转换结束时

● 如果 EOCS 位置 1,在每个规则通道转换结束时

从注入通道转换的数据始终存储在 ADC_JDRx 寄存器中。

(4)不连续采样模式

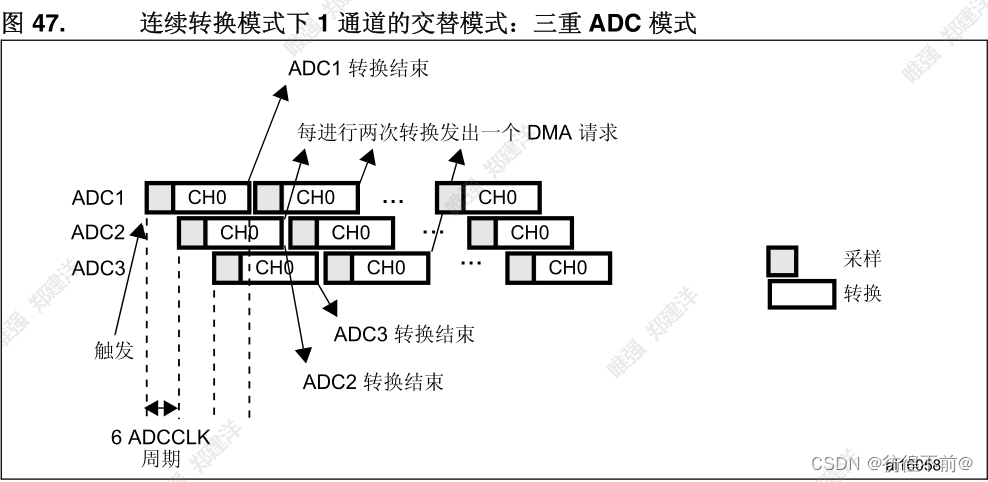

8、多重ADC模式

多重ADC模式下的DMA请求

DMA 模式 2:每发送一个 DMA 请求(两个数据项可用),就会以字的形式传输表示两个 ADC 转换数据项的两个半字。

在双重 ADC 模式下,发出第一个请求时会传输 ADC2 和 ADC1 的数据(ADC2 数据占用高位半字,ADC1 数据占用低位半字),依此类推。

在三重 ADC 模式下,将生成三个 DMA 请求:发出第一个请求时,会传输 ADC2和 ADC1 的数据(ADC2 数据占用高位半字,ADC1 数据占用低位半字)。发出第二个请求时,会传输 ADC1 和 ADC3 的数据(ADC1 数据占用高位半字,ADC3数据占用低位半字)。发出第三个请求时,会传输 ADC3 和 ADC2 的数据(ADC3数据占用高位半字,ADC2 数据占用低位半字),依此类推。

DMA 模式 2 用于交替模式 和规则同时模式(规则同时模式时,仅适用于双重 ADC 模式)。

示例:

a) 双重交替模式:每当有 2 个数据项可用时,就会生成一个 DMA 请求:

第 1 个请求:ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0]

第 2 个请求:ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0]

b) 三重交替模式:每当有 2 个数据项可用时,就会生成一个 DMA 请求

第 1 个请求:ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0]

第 2 个请求:ADC_CDR[31:0] = ADC1_DR[15:0] | ADC3_DR[15:0]

第 3 个请求:ADC_CDR[31:0] = ADC3_DR[15:0] | ADC2_DR[15:0]

第 4 个请求:ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0]

规则同时 + 注入同时组合模式

规则同时 + 交替触发组合模式

仅注入同时模式

仅规则同时模式

仅交替模式

仅交替触发模式

仅交替模式

此模式只能用于规则组,并且通常是用作采集一个通道。外部触发源来自 ADC1 的规则通道多路复用器,也就是说,三个ADC不需要都设置开始转换的触发源,只要设置ADC1的触发源。

AD 转换包括采样阶段和转换阶段,只有采样阶段才会对通道数据进行采集;而在转换阶段只是将采集到的数据进行转换为数字量输出,此刻通道数据变化并不会改变转换结果。在独立模式下的 ADC采集需要在采集并且转换完成后才会进行下一个的采集。双重或者三重 ADC的机制使用两个或以上 ADC同时采样两个或以上不同通道的数据或者使用两个或以上 ADC交叉采集同一通道的数据。双重或者三重 ADC模式较独立模式一个最大的优势就是转换速度快。

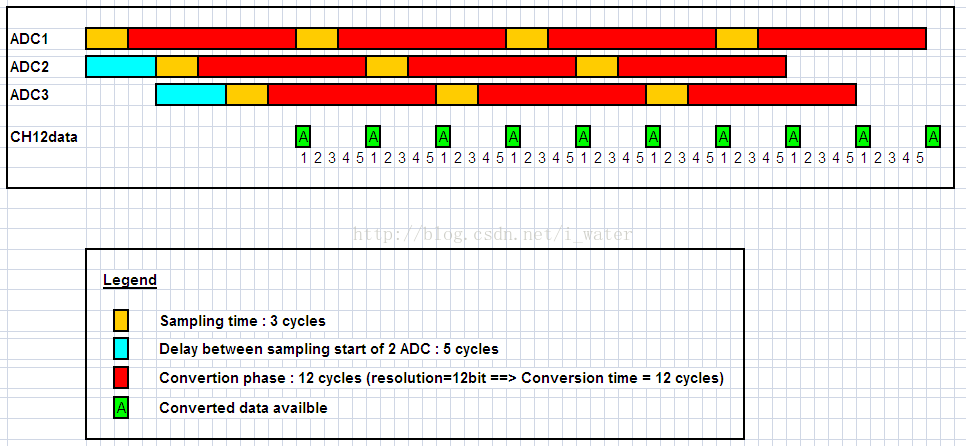

介绍三重 ADC交替模式,三重 ADC交替模式是针对同一通道的使用三个 ADC交叉采集,就是在 ADC1 采样完等几个时钟周期后 ADC2 开始采样,此时 ADC1处在转换阶段,当 ADC2 采样完成再等几个时钟周期后 ADC3就进行采样此时 ADC1 和 ADC2 处在转换阶段,如果 ADC3 采样完成并且 ADC1已经转换完成那么就可以准备下一轮的循环,这样充分利用转换阶段时间达到增快采样速度的效果。利用 ADC的转换阶段时间另外一个 ADC 进行采样,而不用像独立模式必须等待采样和转换结束后才进行下一次采样及转换。

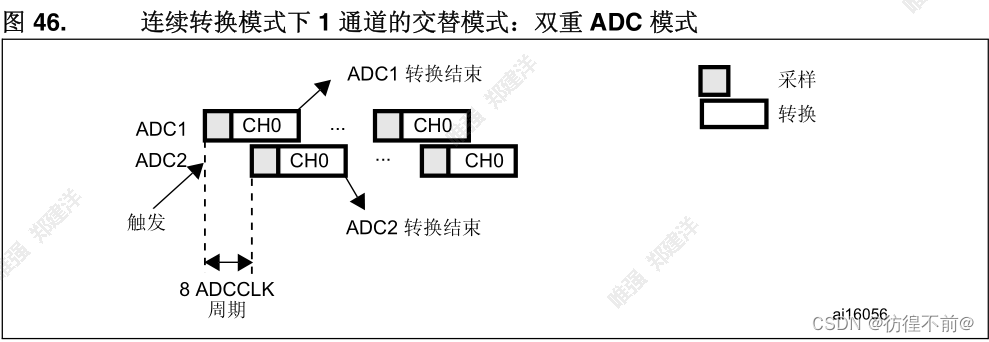

(1)双重ADC模式

出现外部触发之后:

● ADC1 立即启动

● 经过几个 ADC 时钟周期延迟后 ADC2 启动

2 个转换之间的延迟时间通过 ADC_CCR 寄存器中的 DELAY 位进行配置。但是要注意,延迟时间必须大于采样时间,如果延迟时间到了,ADC1仍在对输入信号进行采样,则 ADC2 无法启动转换(因为在给定时间内,只有一个 ADC 能够对输入信号采样)。如果发生这种情况下,延迟时间就不是我们所设置的时间,而是为采样时间 + 2 个ADC 时钟周期,例如,如果两个 ADC 的 DELAY = 5 个时钟周期,而采样时间为 15 个时钟周期,此时设置的延迟时间小于采样时间, 则ADC1 和 ADC2 之间的转换延迟就变为 17 个时钟周期。

如果 ADC1 和 ADC2 上的 CONT 位均置 1,则这两个 ADC 所选规则通道会连续进行转换。

ADC2 生成一个 EOC 中断之后(如果已通过 EOCIE 位使能),会生成一个 32 位 DMA 传

输请求(如果 ADC_CCR 寄存器中的 DMA[1:0] 位等于 0b10)。此请求首先会将存储在ADC_CDR 32 位寄存器高位半字中的 ADC2 转换数据传输到 SRAM,然后将存储在寄存器

低位半字中的 ADC1 转换数据传输到 SRAM。

(2)三重ADC模式

(3)交替模式,三重ADC下的采样频率

当配置延迟时间为5个时钟周期,则每转换一个数据的间隔时间为5个时钟周期,因此在三重模式下,ADC的最大采样频率为22.5MHz/5 = 4.5MHz,也就是说大约 2/9 ≈ 0.222222us采样一次。

三、HAL库编程

1、宏定义

- #define __HAL_ADC_ENABLE(__HANDLE__) \

- (SET_BIT((__HANDLE__)->Instance->CR2, (ADC_CR2_ADON)))

使能ADC外设,通过设置ADC_CR2寄存器的ADON位可给ADC上电。当第一次设置ADON位时,它将ADC从断电状态下唤醒,并且此时需要一段延迟时间 tSTAB 来让ADC稳定。

在STM32F1系列中,ADON位已经置1后,当再次将ADON位置1,若有规则通道并且是软件触发转换的,那么会直接开始转换数据,相当于一次软件触发。

2、函数

HAL_StatusTypeDef HAL_ADC_Start(ADC_HandleTypeDef* hadc);使能ADC外设,开始规则通道的转换。如果是软件触发,会使能SWSTART位立即开始转换;如果是外部触发就要等待外部事件的到来。

HAL_StatusTypeDef HAL_ADC_PollForConversion(ADC_HandleTypeDef* hadc, uint32_t Timeout)等待规则组转换完成。只适用于规则组并且是单次转换,并且不支持DMA。

HAL_ADC_PollForEvent(ADC_HandleTypeDef* hadc, uint32_t EventType, uint32_t Timeout)用于轮询特定的事件是否发生。一般用于轮询看门狗事件。