- 1目标检测综述(待补ing)

- 2机器学习医学_精密医学与机器学习

- 3解决uniapp中tabbar无法路由跳转_uniapp 页面放在tabar后,进行跳转没反应

- 4AI移动碰撞避免算法_移动碰撞算法

- 5改进YOLOv8系列:即插即用新的注意力机制RFAConv

- 6Linux安装及卸载Nginx_linux 如何卸载pcre-8.36

- 7疫情趋势下,远程控制软件成为刚需,ToDesk or 向日葵,哪一款最好用?_哪款远程控制软件最好用知乎

- 8淘宝线上扭蛋机小程序:推动扭蛋机销量

- 9IDEA添加 webapp文件夹同时支持thymeleaf与jsp共存_thymeleaf和webapp

- 10页面嵌套、蓝图连线,在WEB组态大屏和前端界面开发上的应用——UIOTOS前端零代码设计理念

Verilog -- 序列模三(整除3)检测器_verilog取余数%综合

赞

踩

Verilog – 序列模三(整除3)检测器

描述:输入口是1bit,每次进来一位数据,检查当前序列是否能整除3,能则输出1,否则输出0.

例如:

序列=1,out=0;

序列=11,out=1;

序列=110,out=1;

序列=1101,out=0;

首先需要找一下规律,一个数被三除,只可能会有三种情况:

1.余数为0;

2.余数为1;

3.余数为2;

假设当前序列表示的数是x,商为a,余数为b, 则有:

3

a

+

b

=

x

3a+b = x

3a+b=x

需要注意的是:当新进来1bit数据时,实际上隐含了一个条件就是序列将被左移,也就是说如果当前序列为

x

x

x,输入数据为0,则此时序列表示的数是

2

x

2x

2x,如果输入是1,则此时序列表示

2

x

+

1

2x+1

2x+1.

下面分类讨论:

- 余数为0的情况,也就是

3

a

=

x

3a=x

3a=x:

- 输入为0,因为之前余数为0表示已经能整除3,这时输入为0相当于序列乘上个2,仍然能被3整除,输出为1;

- 输入为1,则有 6 a + 1 = 2 x 6a+1=2x 6a+1=2x,可见此时余数为1;

- 余数为1的情况,也就是

3

a

+

1

=

x

3a+1=x

3a+1=x:

- 输入为0,则有 6 a + 2 = 2 x 6a+2=2x 6a+2=2x,可见此时余数为2;

- 输入为1,则有 6 a + 3 = 2 x + 1 6a+3=2x+1 6a+3=2x+1,此时序列可以被三整除,可见此时余数为0,输出为1;

- 余数为2的情况,也就是

3

a

+

2

=

x

3a+2=x

3a+2=x:

- 输入为0,则有 6 a + 4 = 2 x 6a+4=2x 6a+4=2x,可见此时余数为4 mod 3 = 1;

- 输入为1,则有 6 a + 5 = 2 x + 1 6a+5=2x+1 6a+5=2x+1,可见此时余数为5 mod 3 = 2;

也可以用下面的表来描述:

| last_Remainder | Input | Remainder | Output |

|---|---|---|---|

| 0 | 1 | 1 | 0 |

| 0 | 0 | 0 | 1 |

| 1 | 0 | 2 | 0 |

| 1 | 1 | 0 | 1 |

| 2 | 0 | 1 | 0 |

| 2 | 1 | 2 | 0 |

通过上面的分析可以发现,余数的三种情况可以作为状态机的三种状态,当前的状态以及输出只跟之前的状态和当前的输入有关,因此可以使用Mearly型状态机描述。

状态转换表:

| State\Input | 0 | 1 |

|---|---|---|

| 0 | 0/1 | 1/0 |

| 1 | 2/0 | 0/1 |

| 2 | 1/0 | 2/0 |

表中的值表示next_state/output

Verilog代码:

`timescale 1ns/1ps module seq_mod3_detector ( input clk, input rst_n, input data, output reg success ); reg [1:0] current_state; reg [1:0] next_state; always@(posedge clk or negedge rst_n) begin if(!rst_n) current_state <= 0; else current_state <= next_state; end always@(*)begin next_state = 0; case(current_state) 2'd0: if(data) next_state = 2'd1; else next_state = 2'd0; 2'd1: if(data) next_state = 2'd0; else next_state = 2'd2; 2'd2: if(data) next_state = 2'd2; else next_state = 2'd1; default: next_state = 0; endcase end always@(posedge clk or negedge rst_n) begin if(!rst_n) success <= 0; else begin case(next_state) 2'd0: if(data) success <= 0; else success <= 1; 2'd1: if(data) success <= 1; else success <= 0; 2'd2: if(data) success <= 0; else success <= 0; default: success <= 0; endcase end end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

testbench:

`timescale 1ns/1ps module seq_mod3_detector_tb(); reg clk; reg rst_n; reg data; wire success; reg [127:0] seq; always #1 clk = ~clk; initial begin clk = 1; rst_n = 1; data = 0; #2 rst_n <= 0; #2 rst_n <= 1; seq = 0; while(1) begin @(posedge clk) begin data = $random%2; seq = (seq<<1) + data; end end end seq_mod3_detector U_SEQ_MOD3_DETECTOR_0( .clk ( clk ), .rst_n ( rst_n ), .data ( data ), .success ( success ) ); initial begin $fsdbDumpvars(); $fsdbDumpMDA(); $dumpvars(); #200 $finish; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

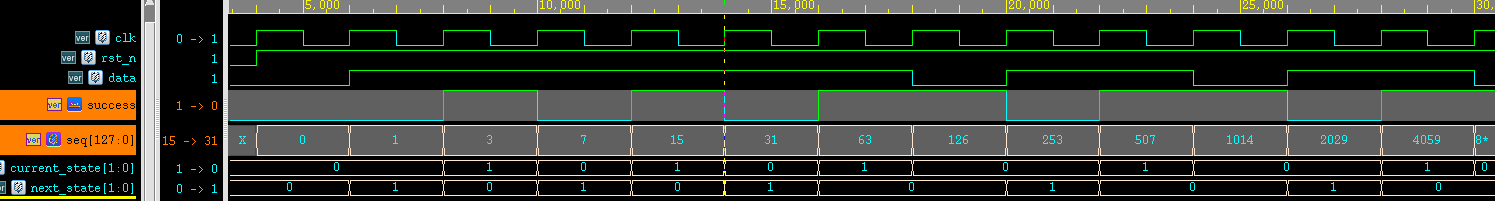

波形图:

可以看到,功能正确。