- 1Linux救援:开机进不了系统,显示”GRUB>”命令提示符的解决方法_开机出现grub无法进入系统

- 2C语言基础-值传递和指针传递

- 3PTA甲级之图的考查_pta甲级是什么

- 4高频JMeter软件测试面试题_jmeter面试

- 5RabbitMQ、RocketMQ、Kafka为啥性能差别这么大_rocketmq为什么比rabbitmq快

- 6【自用】国科大杭高院英语慕课学习(2023-4)_国科大英语慕课quiz答案

- 7python try里面嵌套try_try catch里面try catch嵌套

- 8学会用Python爬取小说网站,想看什么就爬什么,广告也不用看了~_怎么爬小时网站的小说

- 9[论文解读]UNet++解读 + 它是如何对UNet改进 + 作者的研究态度和方式_两个unet++

- 10第二十六期:HTTP 3的前世今生及尝鲜_http3诞生

ISE_软件基本使用流程(win10 的bug&工程&约束&仿真&烧写&mcs固化)

赞

踩

背景

关于ISE 14.7 是支持所有系列的XILINX器件的,之前一直想入手ISE,作为三大工具之一,也是必须要掌握的。一直耽搁耽搁,归根结底,其实还是自己的学习渴望不够强烈,如果学习渴望足够强烈,时间总会挤出来的,所以,这一点上,我感到深深的自责和愧疚之感。后悔也没啥用了,那也只能现在抓紧抓紧再抓紧吧。。。。(来自处女座的苦恼)

1、前言

由于vivado的诞生,ISE停留在了ISE 14.7,但是ISE 14.7是支持spartan 6的。

基本的流程如下:

可以看到这个流程,和我们之前用Alteral的,也是一样的。

2、流程

1、新建工程

选择器件,内嵌的综合工具默认是XST,仿真器选择modelsim-SE的verilog仿真

2、编写代码

然后,我们就可以添加文件了,编写verilog代码了。

这里补充一点,自动补全快捷键按 ctrl +enter

此处定义一个1秒钟变化一次的led小灯

`timescale 1ns / 1ps // // Company: // Engineer: // // Create Date: 12:30:05 05/12/2019 // Design Name: // Module Name: ISE_led_top // Project Name: // Target Devices: // Tool versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module ISE_LED( input sysclk, input rst, output led ); reg [28:0] time_cnt; reg led_reg; always @ (posedge sysclk or negedge rst) begin if(!rst) time_cnt<=0; else if (time_cnt=='d50000000) time_cnt<=0; else time_cnt<=time_cnt+1'b1; end always @ (posedge sysclk or negedge rst) begin if(!rst) led_reg<=0; else if(time_cnt=='d50000000) led_reg<=~led_reg; else led_reg<=led_reg; end assign led=led_reg; endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

点击XST可以进行综合分析,从而判断代码是否出错。

有错是正常的,没有一个人敢保证不用编译器检查,第一遍写代码就完全正确。

XST编译成功后的界面。

3、时序约束

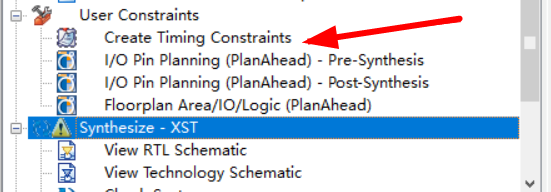

在上图中,我们用Creat Timing Contraints来创建时序约束。

另外在ISE中,时序约束文件,被称之为UCF。其实就是user contraints file的简称。

一般来说,对于一些简单的工程,我们仅仅需要约束时钟就可以了。

这里,我要说明一下,ISE对代码的检测还是比较严格的,如果我输出端口没有被赋值,都会报错,只要有错误,那么时序约束界面就可能不会给出clock domains这个选项。

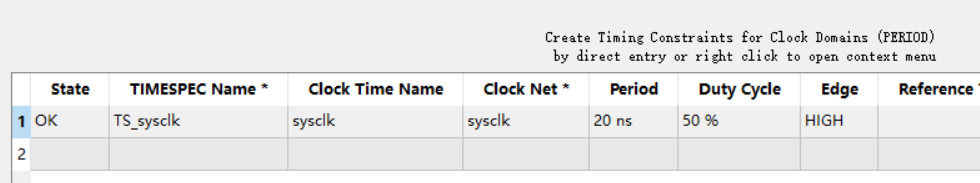

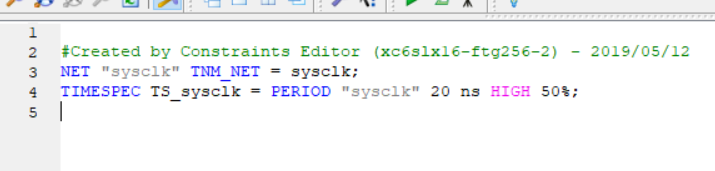

在图中,第一栏TIMESPEC(Timing Specificaition,时钟说明)名称为TS_sysclk,表示创建一个时钟约束标识符“TS_sysclk”;第二栏“Clock net name”(时钟管脚名)自动设为“sysclk”,第三栏指定“TIME”(时钟周期)为20ns,“initial clockedge”(最初的时钟沿)为上升沿,“rising duty cycle”(上升沿的占空比为50%),设置完后,点击[ok]即可。

这里要说明下,其实TS_sysclk就是和timequest一样,只是一个名字而已,实际上,重要的是关联的目标sysclk。

4、分配管脚

1、手动分配管脚

如果打不开报错的话,而且已经解决过了wein10的兼容性问题,那么可以清楚工程文件

此时我们可以看到ucf文件中,已经增加了对管脚的约束。

2、使用ucf文件分配管脚

可以导出来管脚信息

5、配置工程

在工程中,我们需要将没有使用的管脚配置为浮空状态。在编译流程窗口下找到【generate programming file】并右键点击【process properities…】

在工程中,我们需要将没有使用的管脚配置为浮空状态。在编译流程窗口下找到【generate programming file】并右键点击【process properities…】

我们将没有使用的管脚配置为浮空状态。

我们将没有使用的管脚配置为浮空状态。

6、下载程序

注意,如果你的管脚分配不恰当,就会导致实现implement不通过

点击generate programming file就可以对整个工程进行全编译。

连接下载器

双击boundary scan

点击initial chain,这个时候,软件会自动识别。

此时,又会弹出一个窗口问我们是否要添加一个额外的PROMs,由于我们进行在线下载的,所以我们不需要。也就是说,我们并没有采取固化操作。

点击OK即可

然后在弹出来的窗口中点击yes,选择生成后的bit文件。

在初始化完毕后,点击操作中的program即可下载程序

此时小灯就能开始闪烁啦

3、win10与ISE的bug解决方案

https://blog.csdn.net/feq123/article/details/80900389

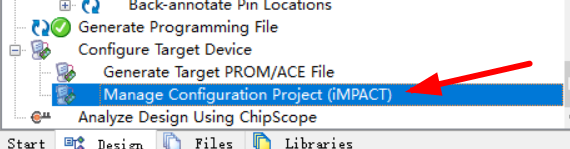

4、固化程序

前面的2,已经把基本流程讲解完毕,现在再做一些补充,关于如何固化程序,这一点,从这么一个背景说起,最近两天想叫外协写的程序发过来,我们自己烧写,别人当然不会给源代码,于是给了我们一个叫什么m啥的文件,当然别人也不会给bit文件,bit文件貌似不能固化。

由于我们下载的bit文件,所以开发板掉电会丢失

如果我们想要不丢失,我们就必须利用jtag接口下载MCS文件到FLASH中,就可以实现程序掉电不丢失。

我们可以在上图的位置点击,也可以在iMACT中点击。

创建PROM文件

选择要转换的bit文件后,然后选择no,代表只添加一个bit文件。

点击generate,生成mcs文件

生成mcs文件后,返回下载页面,双击蓝色虚线框的SPI,选择mcs文件

先把flash给擦除,然后再烧写程序进进去。

然后双击program即可。

总之一句话,就是要先将bit文件转换成mcs文件,然后通过flash的SPI配置烧写到flash中即可。

5、ISE搭配Modelsim软件的使用

1、关联modelsim路径

在ISE中调用Modelsim,就像alteral一样,只要我们设置好了路径,我们就可以直接调用modelsim,至于如何脱离了ISE平台,采用do文件仿真,在后面有时间,我会专门写一篇针对这三大工具平台,独立的进行仿真。

2、添加TB文件

表示待仿真的文件是ISE_LED,与之关联的文件是ISE_LED.

表示待仿真的文件是ISE_LED,与之关联的文件是ISE_LED.

此时,我们可以看到TB文件已经有了不少例化被测试的模块了。

现在,我们要做的就是写激励就行了。

`timescale 1ns / 1ns // Company: // Engineer: // // Create Date: 20:02:51 05/12/2019 // Design Name: ISE_LED // Module Name: D:/ISE_FPGA_Project/liruifeng_tem/ISE_learning/ISE_LED/ISE_LED/ISE_LED_tb.v // Project Name: ISE_LED // Target Device: // Tool versions: // Description: // // Verilog Test Fixture created by ISE for module: ISE_LED // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // module ISE_LED_tb; // Inputs reg sysclk; reg rst; // Outputs wire led; // Instantiate the Unit Under Test (UUT) ISE_LED uut ( .sysclk(sysclk), .rst(rst), .led(led) ); initial begin // Initialize Inputs sysclk = 0; rst = 0; // Wait 100 ns for global reset to finish #100 rst=1; forever begin #20 sysclk=~sysclk; end // Add stimulus here end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

3、编译仿真库实现功能仿真

编写完了仿真文件,接着,我们需要编译仿真库。

就可以启动modelsim了,这里指的注意的是:我们修改了verilog程序代码和仿真文件代码(前提是不修改端口信号),我们不需要重新编译工程,我们只要关闭modelsim仿真软件,再一次点击开始仿真即可。如果我么你修改了端口的输入和输出,那么这里最好重新全编译一次,并且我们需要重新生成仿真模板文件进行修改。至此,我们就完成了功能仿真。

以25M时钟源,可以看到每隔2S钟,输出变化一次,符合预期标准。

补充:其实,我试了下,直接点击仿真行为仿真即可

上图是把始终晶振更改为50M后,直接点击行为仿真。

4、门级仿真

至于门级仿真就是布线后的仿真,综合后,进行ISE的实现操作(implement),包括转换、映射、布局布线。在这三个过程中每一个过程都会生成一个仿真模型,由于翻译和映射不会产生延时,因此常用布局布线后产生的仿真模型进行时序仿真。

在实现过后,点击【Generate Post Place&Route Simulation Model】开始建立时序布局布线后的仿真模型。

如上图所示,选择布线后模型

6、ISE无法编译XILINX库文件的解决办法

今天,我在学习vivado的时候,也需要配置modelsim的路径,于是我打开ISE,本来想查看一下。结果发现之前都好好的,编译XILINX库,居然报错,通不过了。明明路径都已经给出了,但是却编译不通过错误。

其实我们只需要在执行文件后面加一个\即可,这个和quartus的modelsim有时候也出现这种情况是一样的。

6、使用ISE自带的内嵌仿真器ISim

这里,我为什么要单独说一下ISim的使用流程,就是因为ISim,这个东西和VIVADO自带的仿真器也非常相似,不知道是不是因为一个公司开发的,那批人就在源代码上面改了改的原因。至于quartus的自带仿真器件的仿真,非常的low,一半我们都不用。所以关于quartus的自带仿真就不介绍了。

如上图所示,将仿真工具选为ISim

可以仿真时间

下面,我们用后仿真试试看。

这里,我就不给出仿真波形了,因为我试了,1s仿真时间太长了。

至此,ISE基本使用流程讲解完毕