- 1Unity C# List中每次取5个_unitylist获取5到8

- 2【Windows、Linux 直接启动Jar包程序】_windows nohup java -jar

- 3创建网站最简单教程:域名、服务器、备案...一条龙——通过宝塔面板tomcat部署阿里云服务器,域名直接访问java项目_linux宝塔面板使用tomcat部署项目

- 4pyqt5界面的布局与资源文件的载入_pyqt5布局文件

- 5vue项目安装scss_vue 安装scss

- 6计算机毕业设计Python+django医院后勤服务系统flask

- 7关于Metasploit-学习笔记-基础命令以及参数

- 8使用ENV工具搭建工程_env.exe

- 9Gerrit 提示冲突,不能合并代码(git解决远程冲突)_the change cannot be merged

- 10docker拉取Ubuntu20.04_ubuntu20.04 拉起docker

Fpga开发笔记(二):高云FPGA发开发软件Gowin和高云fpga基本开发过程_高云cpld编译综合后

赞

踩

若该文为原创文章,转载请注明原文出处

本文章博客地址:https://hpzwl.blog.csdn.net/article/details/135620590

红胖子网络科技博文大全:开发技术集合(包含Qt实用技术、树莓派、三维、OpenCV、OpenGL、ffmpeg、OSG、单片机、软硬结合等等)持续更新中…

FPGA开发专栏

上一篇:《Fpga开发笔记(一):高云FPGA芯片介绍,入手开发板套件、核心板和底板介绍》

下一篇:敬请期待…

前言

本篇安装高云的开发软件Gowin,并且描述了一个基于高云fpga的程序的开发环境和完整的下载运行过程。

Gowin软件

概述

Gowin 软件是广东高云半导体股份有限公司的 FPGA 开发软件。

下载地址

http://www.gowinsemi.com.cn

申请license

申请license地址:http://www.gowinsemi.com.cn/faq_view.aspx

这个过程也有一个和谐的方式,可查看:

http://www.corecourse.cn/forum.php?mod=viewthread&tid=29510

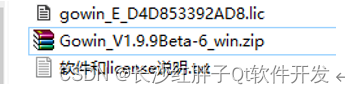

下载好软件、获取到license后就是安装软件了。

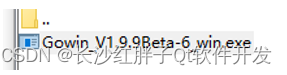

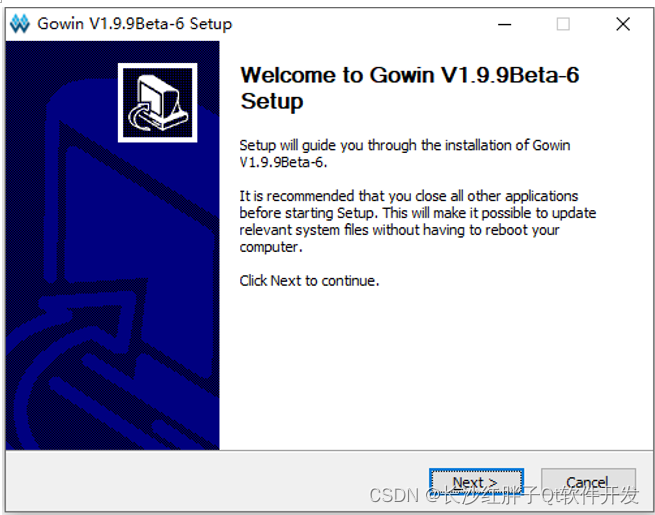

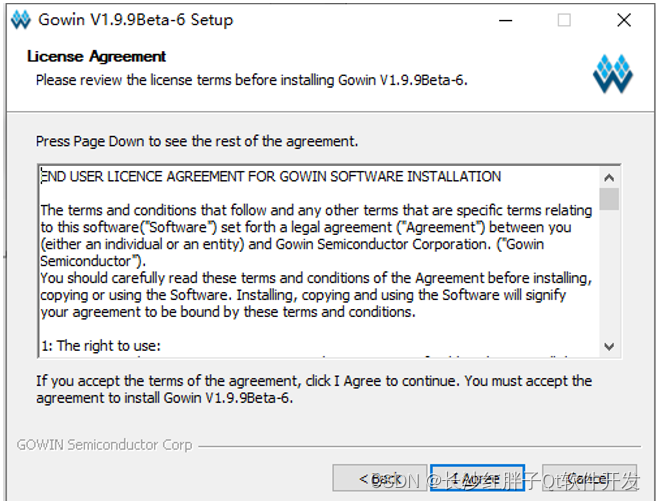

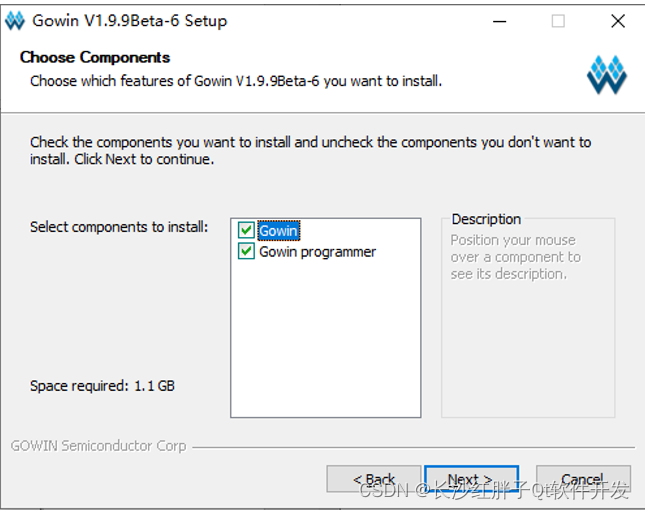

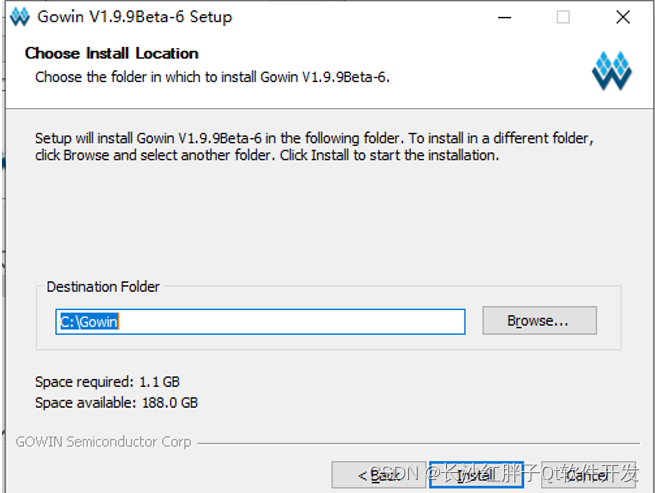

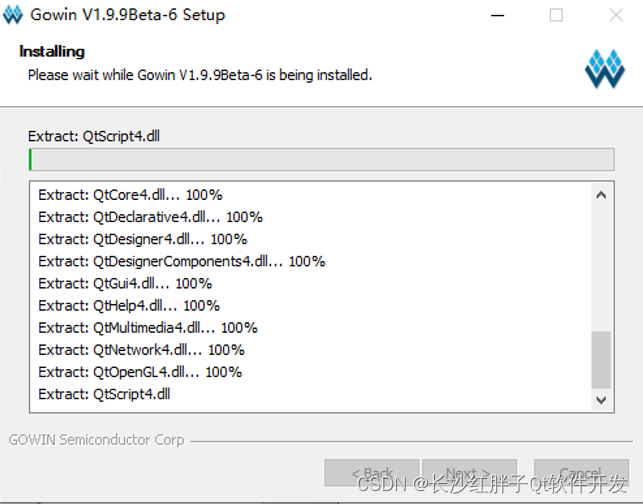

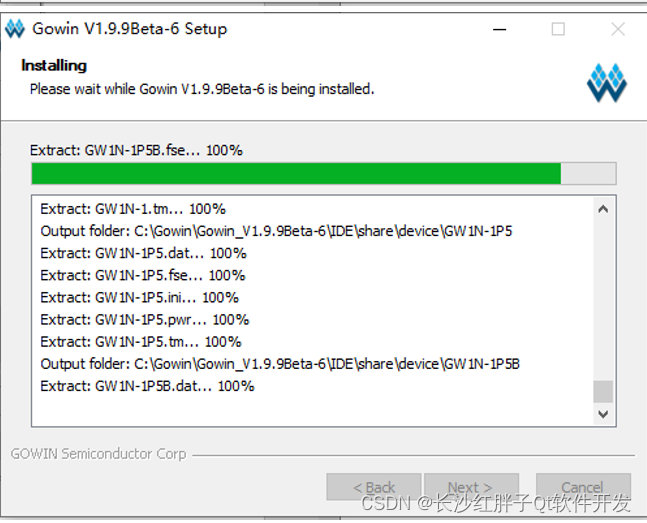

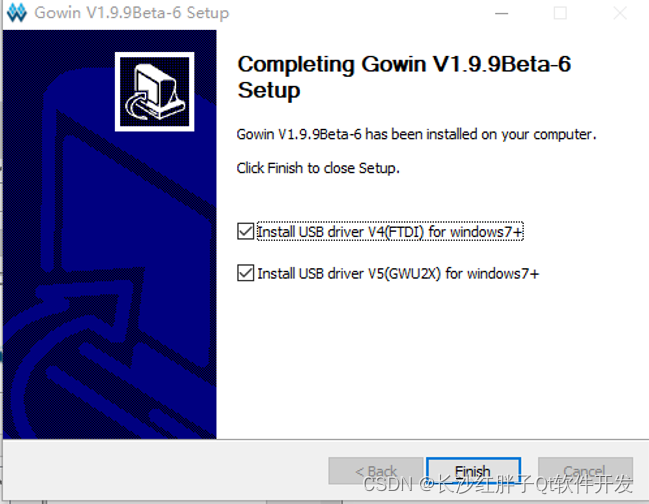

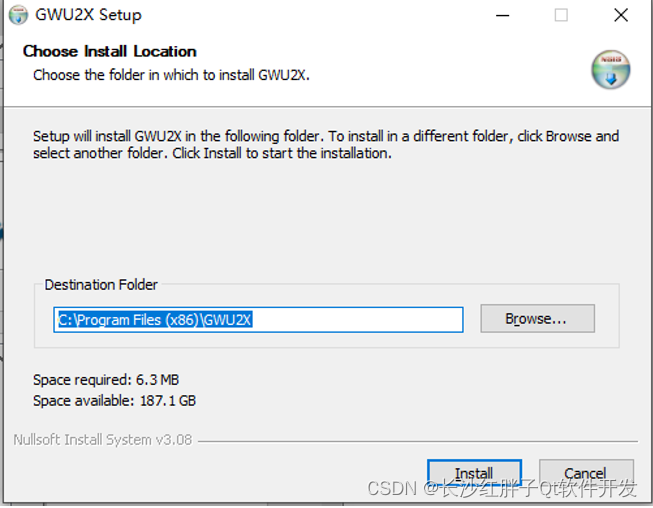

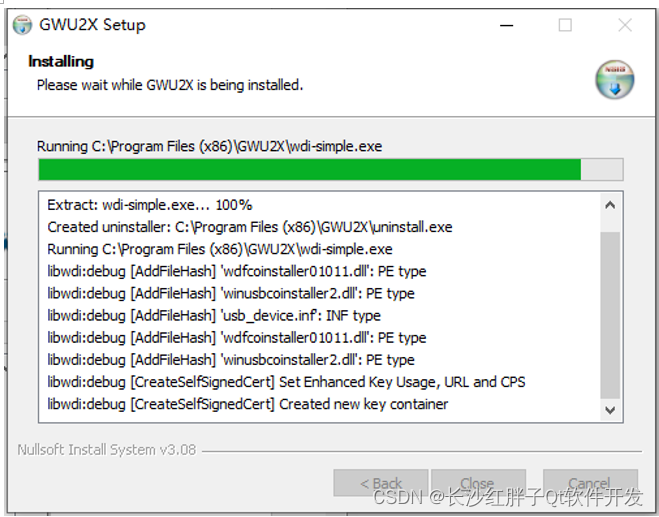

安装Gowin软件

然后,就没有然后了,直接没了,是安装完成了。

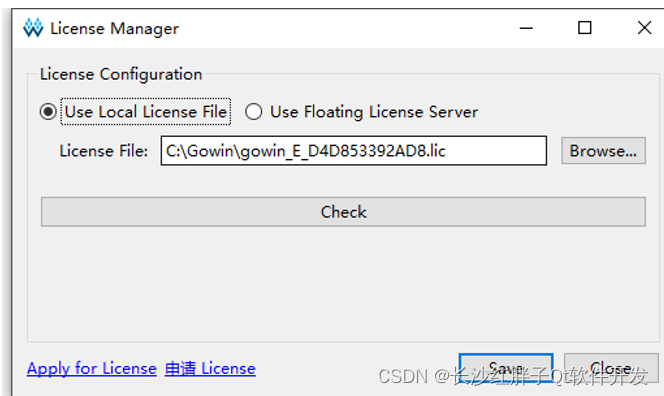

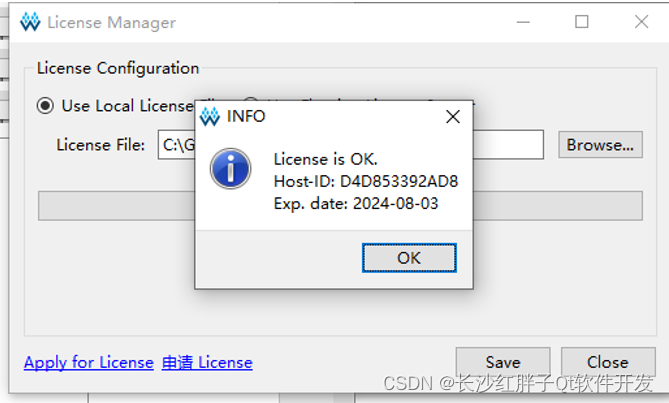

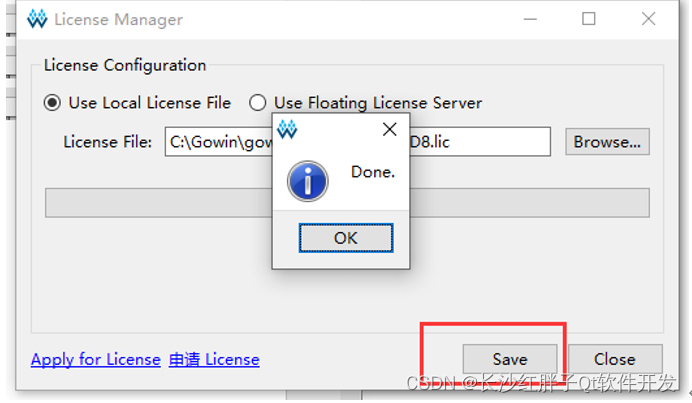

License注册

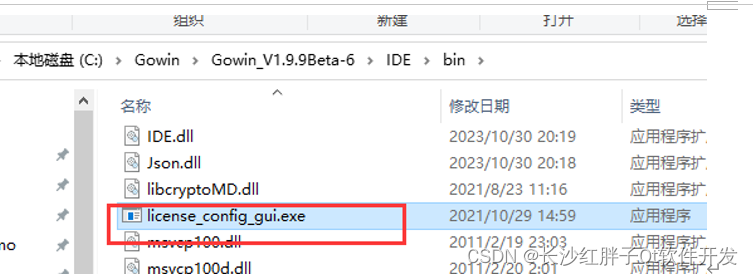

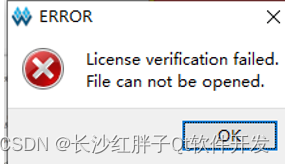

这是没有license,打开安装目录下:

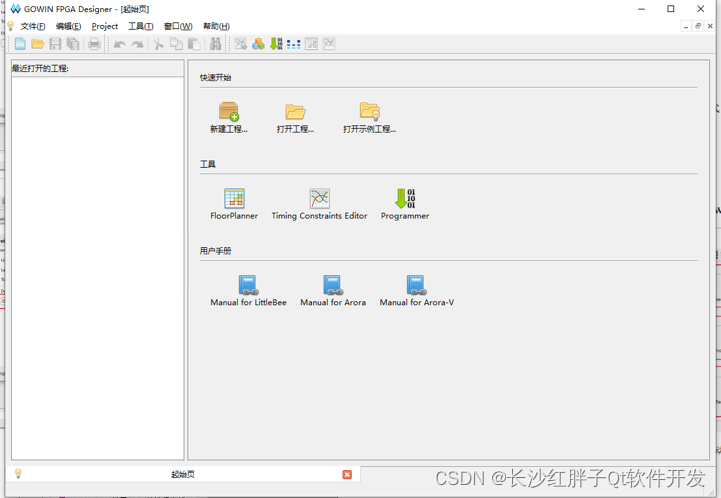

启动软件

拖出来,放到“开始”屏幕上:

点击打开:

以上是注册license失败了或者未注册,退回去,继续注册。

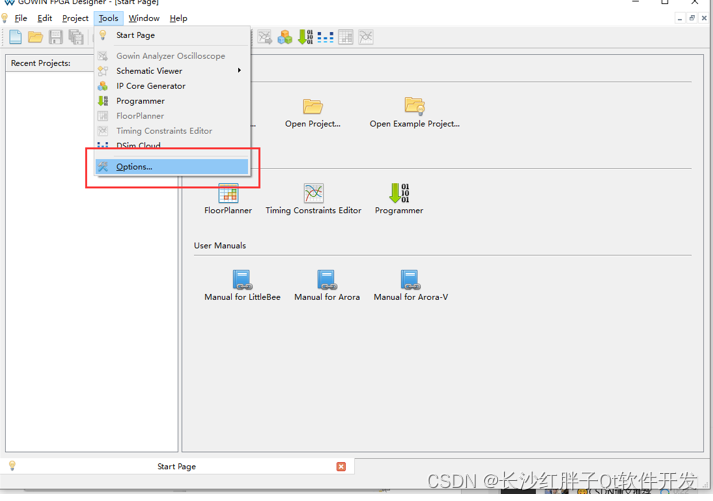

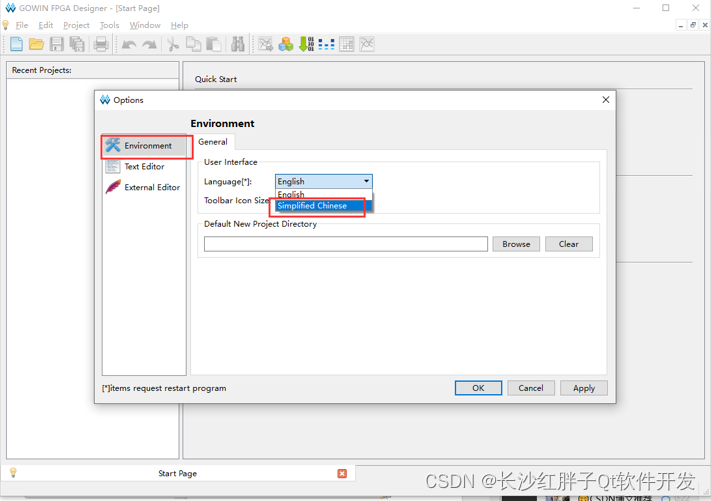

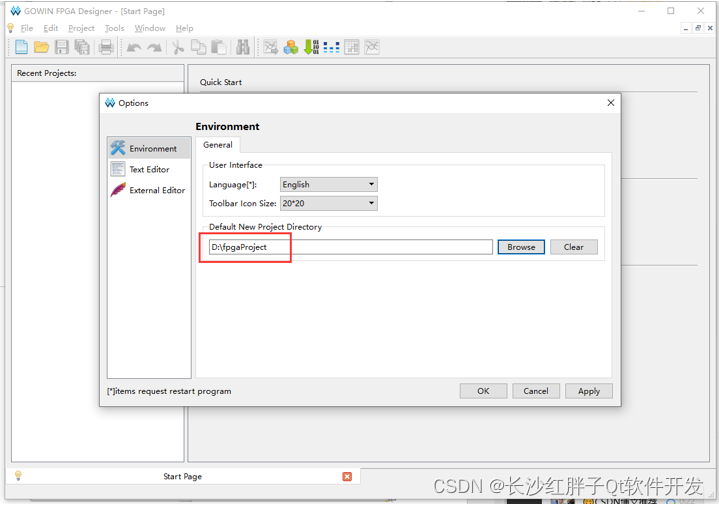

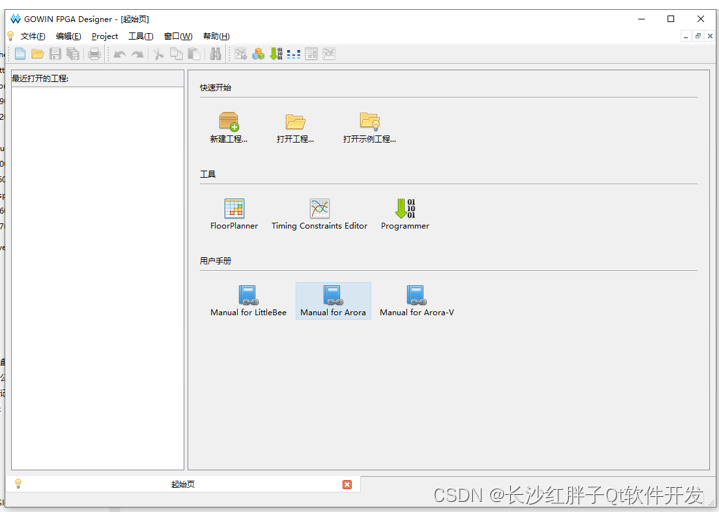

配置中文和新建工程默认路径

Fpga开发过程

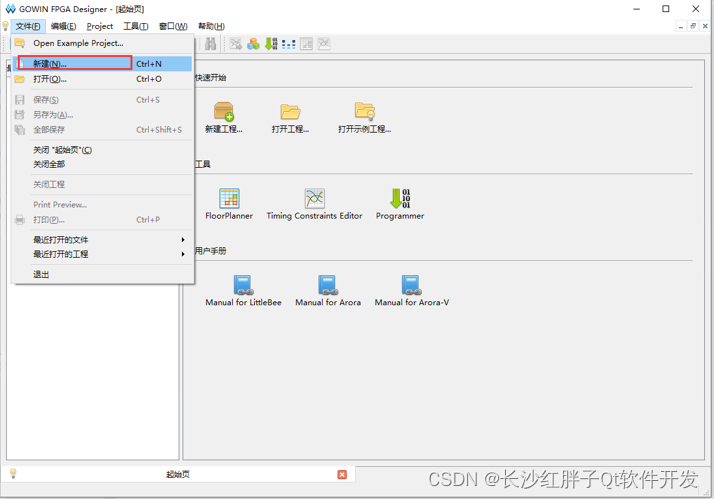

步骤一:打开软件

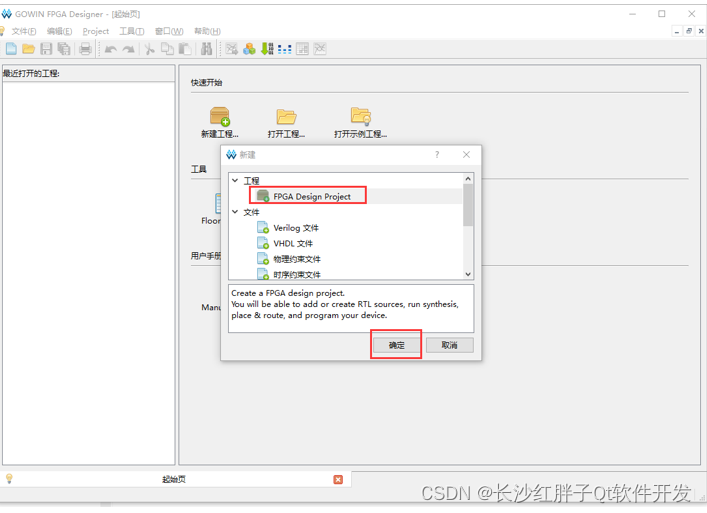

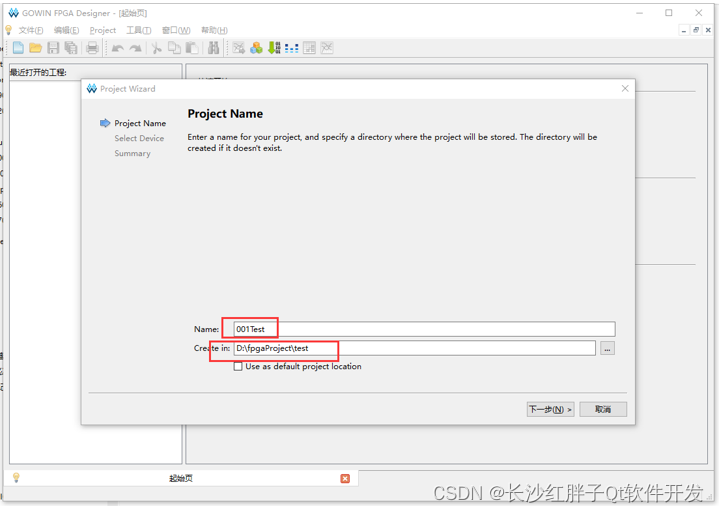

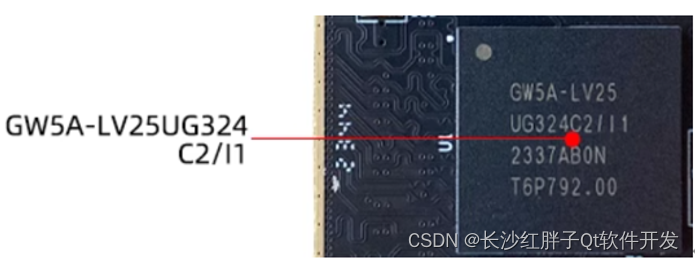

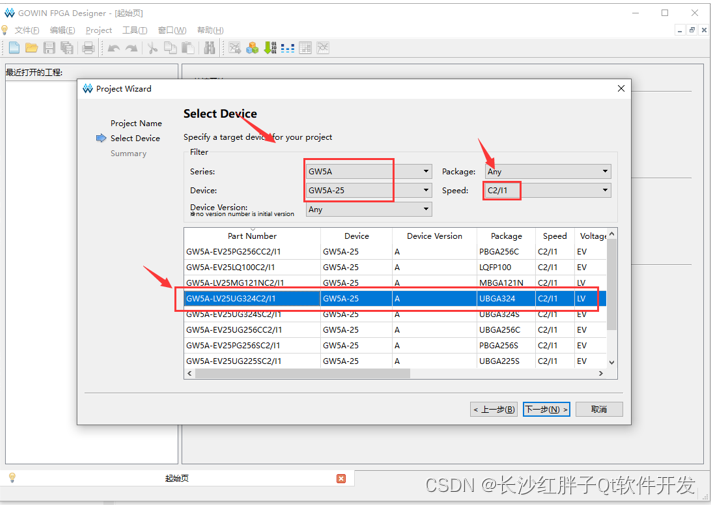

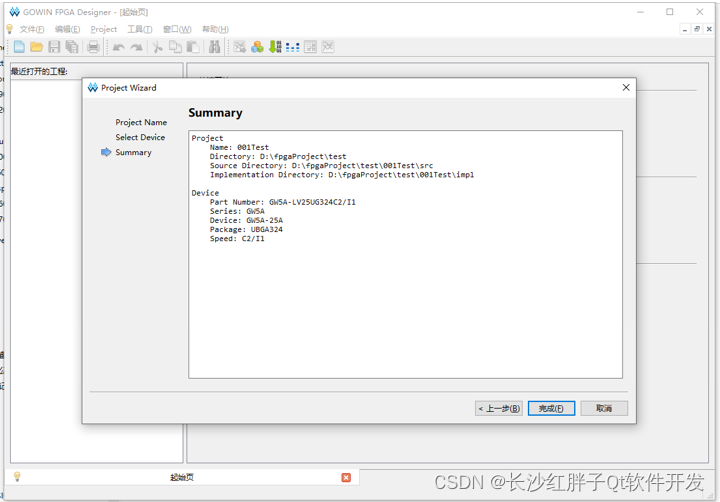

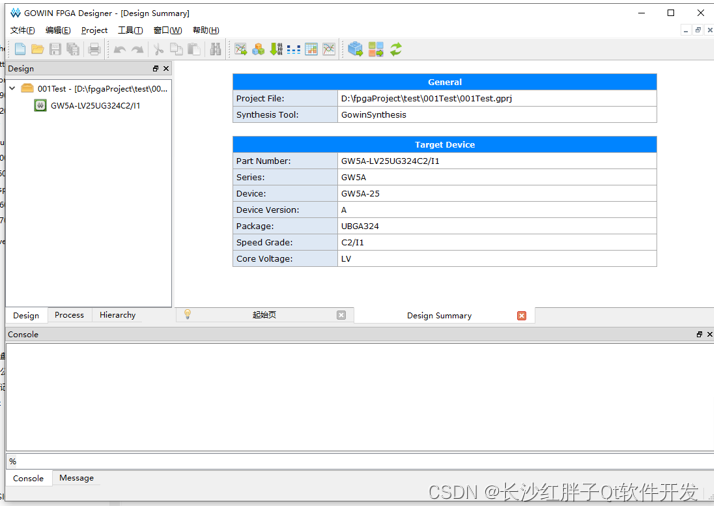

步骤二:创建工程/打开工程

步骤三:编辑/添加verilog源文件

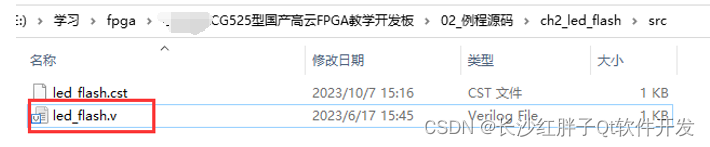

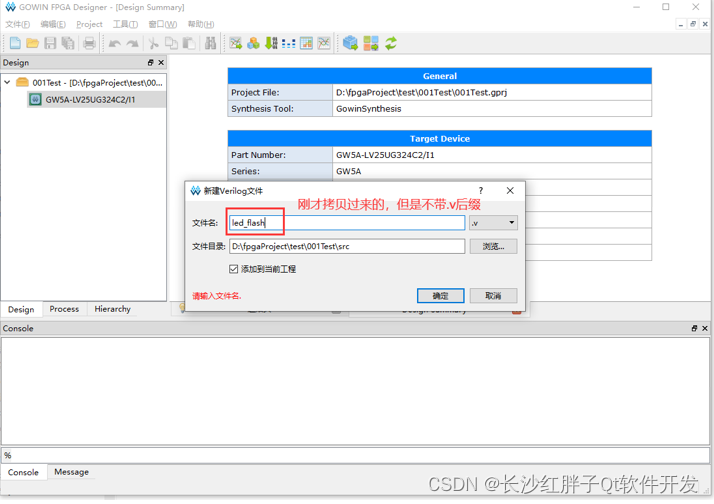

这里添加一个verilog的程序源码,从demo里面随便拿一个(这是一个反转led灯的demo程序源码):

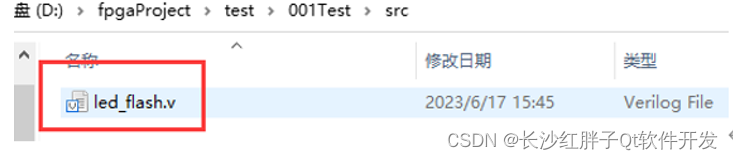

复制到工程的src下:

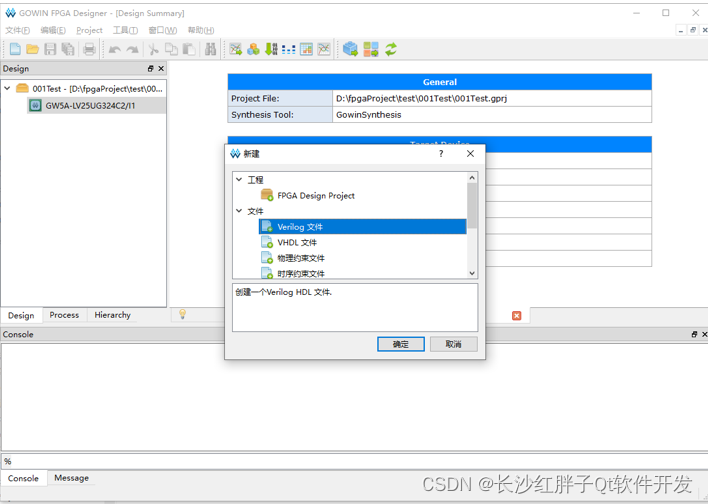

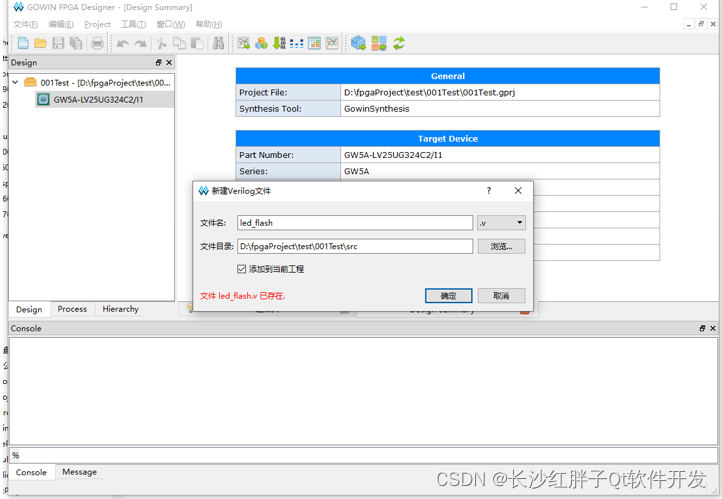

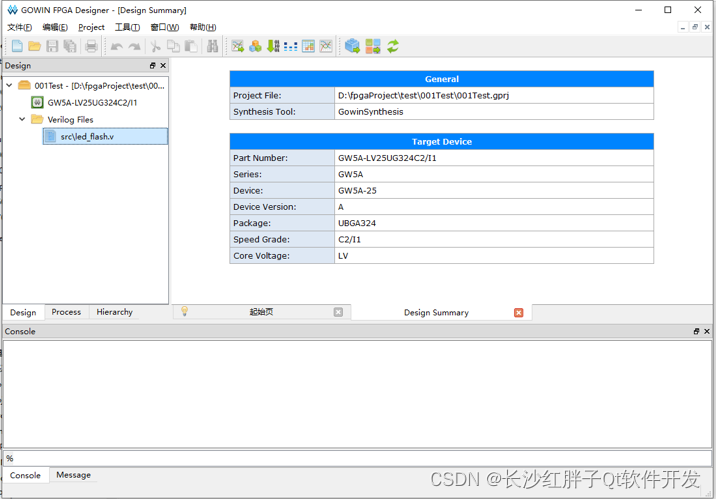

然后添加下verilog文件:

上面是新建文件的方式,下面是添加已有文件的方式:

选择src目录下的.v文件:

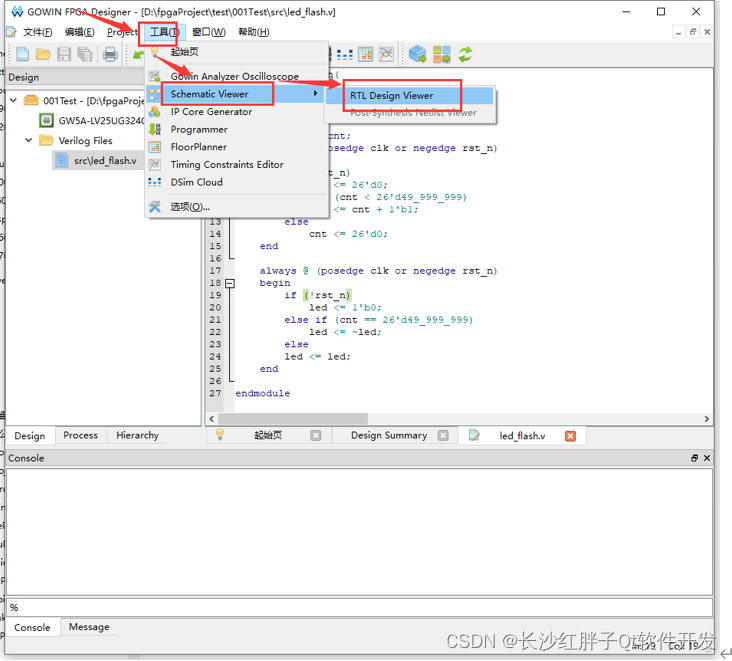

步骤四:RTL语法分析(相当于代码编程的编译)

点击后:

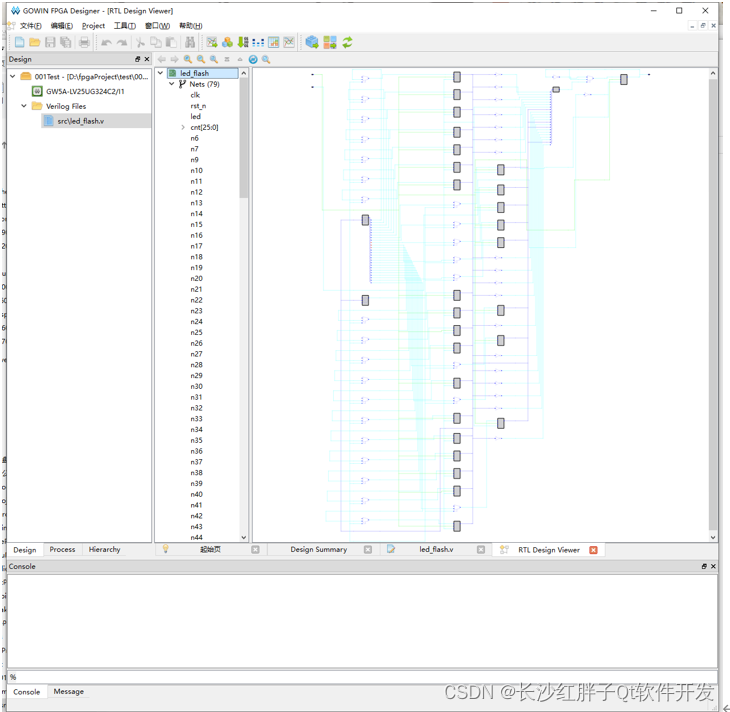

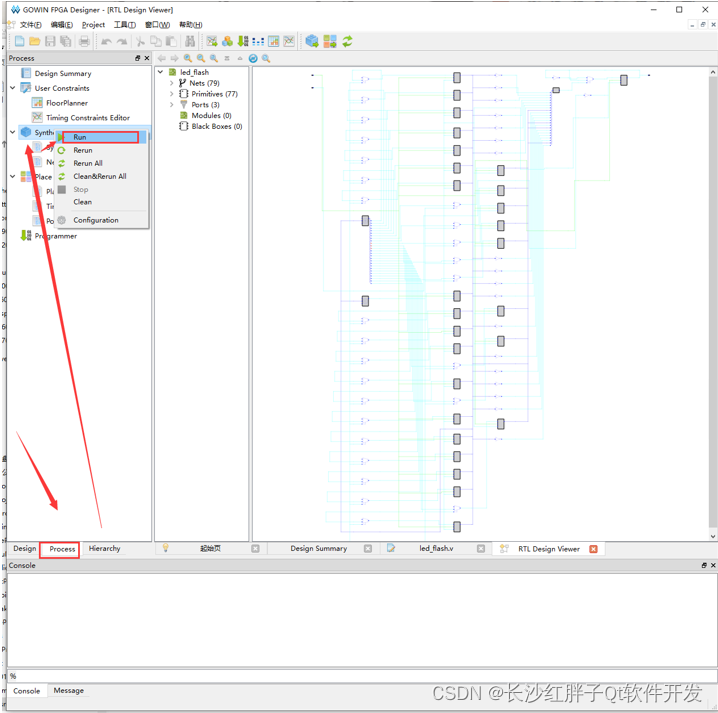

然后开始分析综合:

完成后,就是生成了fpga的底层资源电路网表:

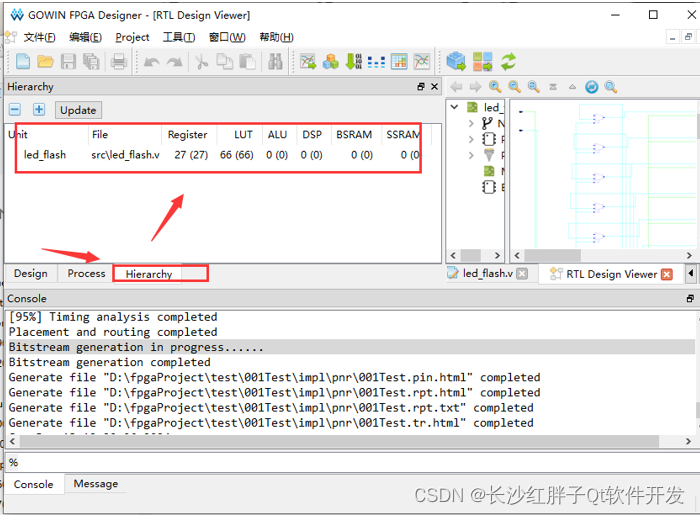

完成后,Hierarchy显示模块使用的资源:

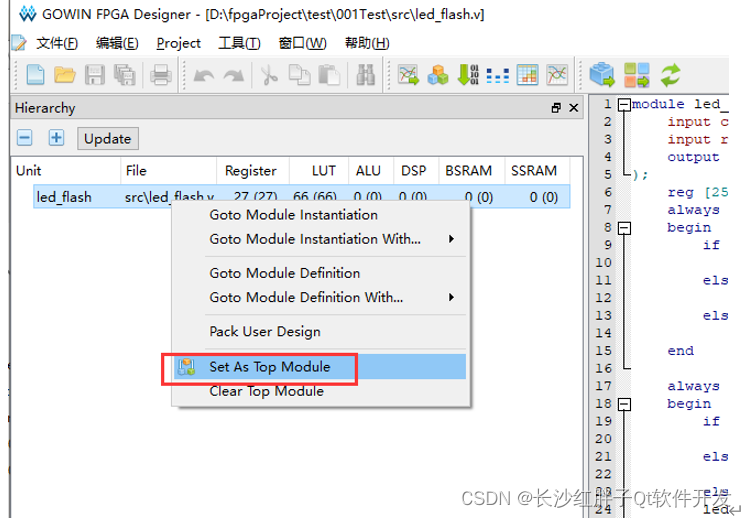

设置顶层文件:

这个好像是跑哪一个程序。

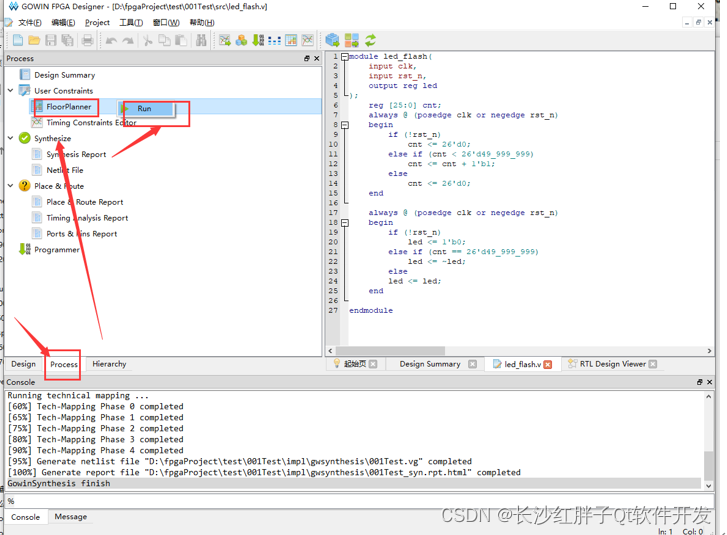

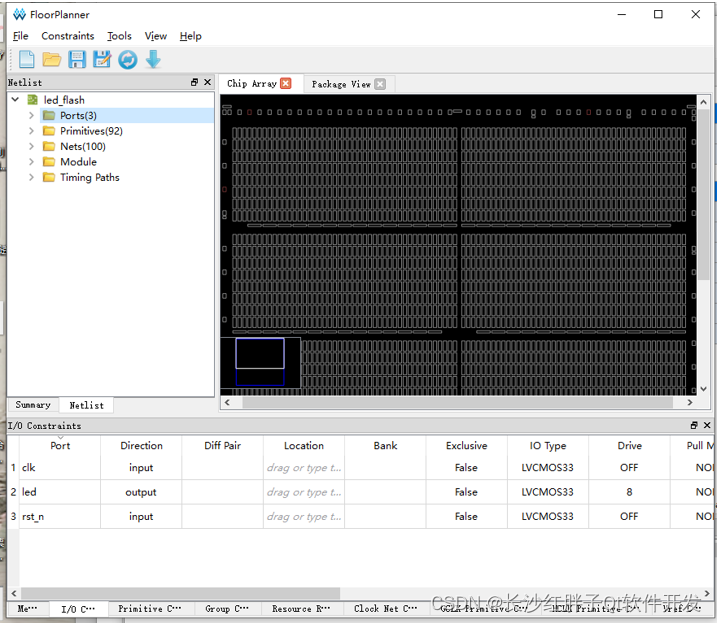

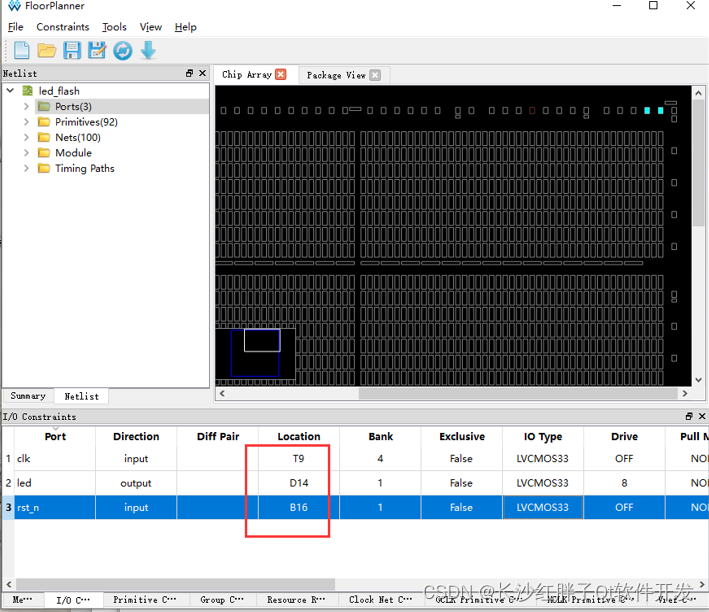

步骤五:物理约束

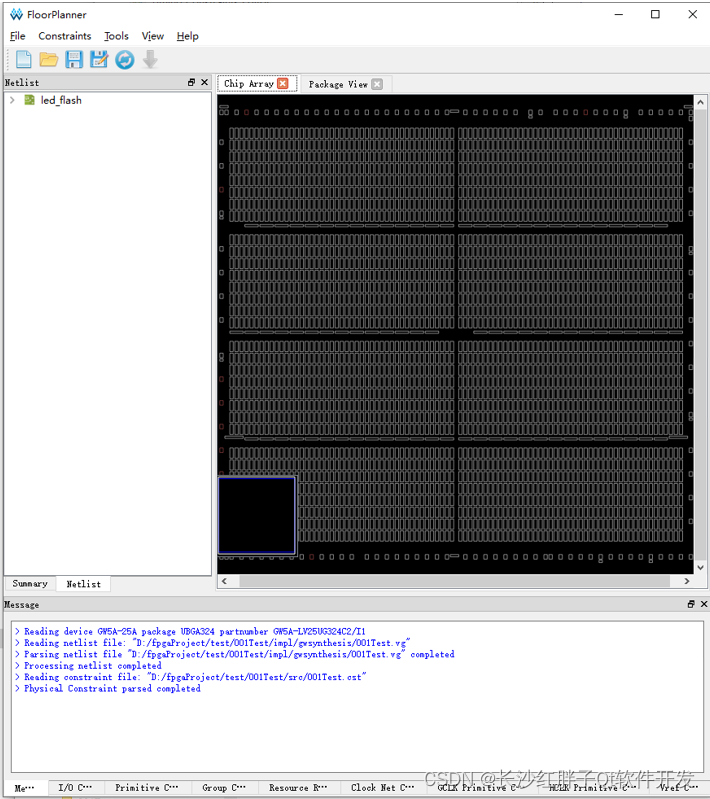

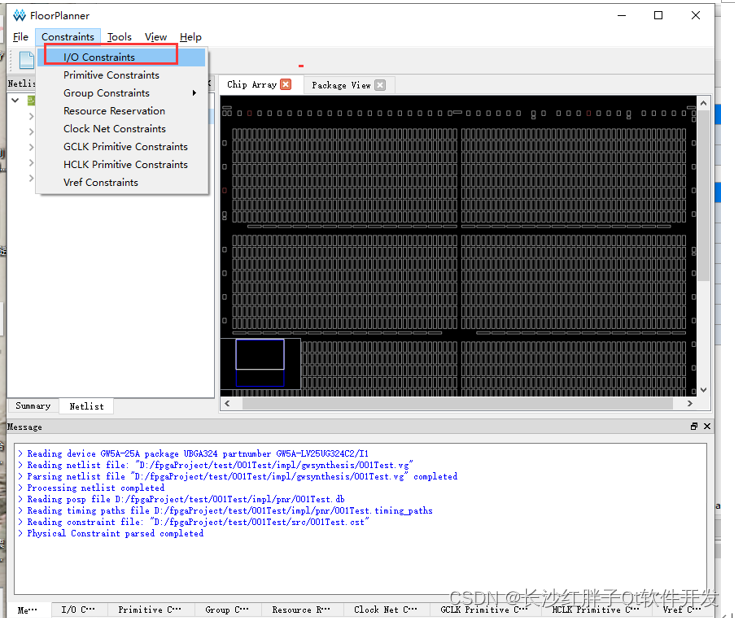

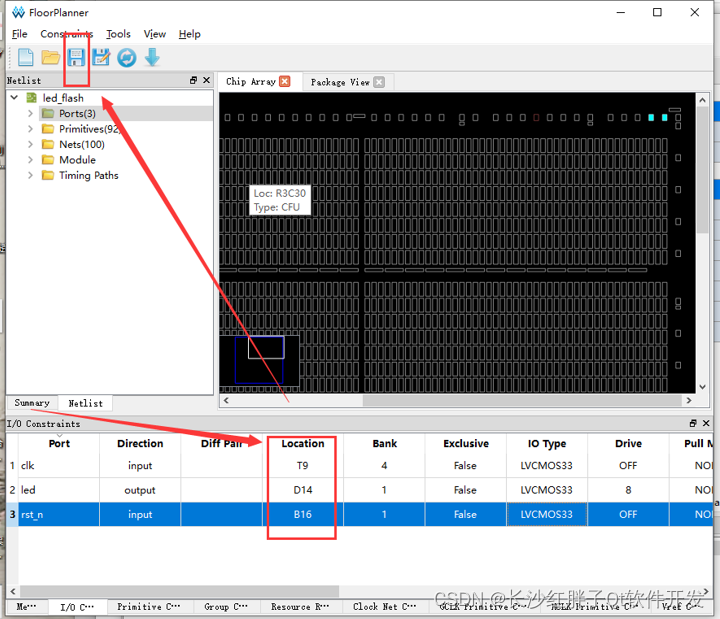

进入FloorPlanner界面,点击I/O Constraints,进行I/O约束,然后根据自己的板卡分配引脚和电平标准,

弹出新框:

点击I/O Constraints:

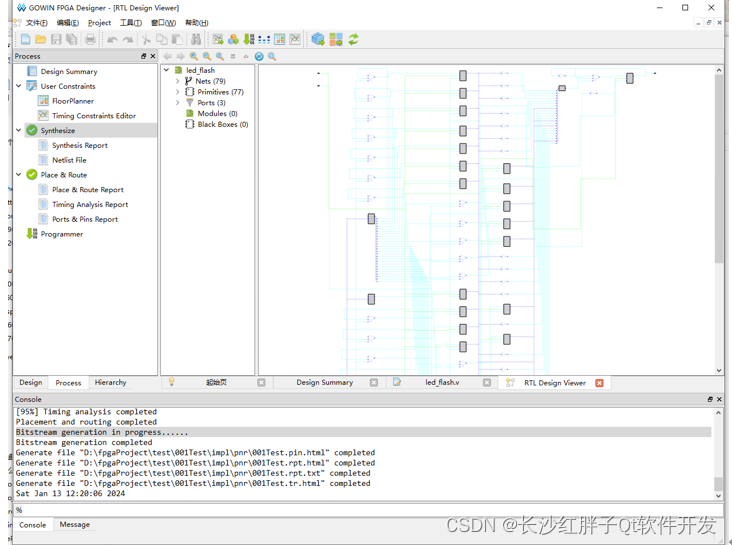

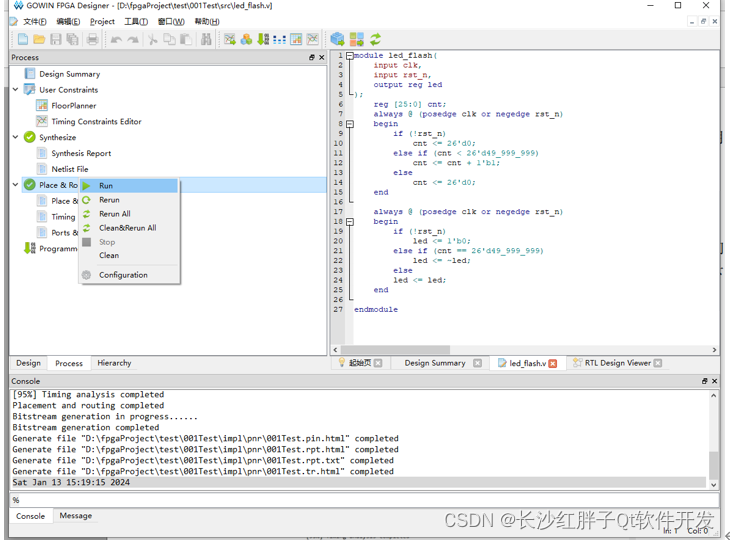

步骤六:布局布线

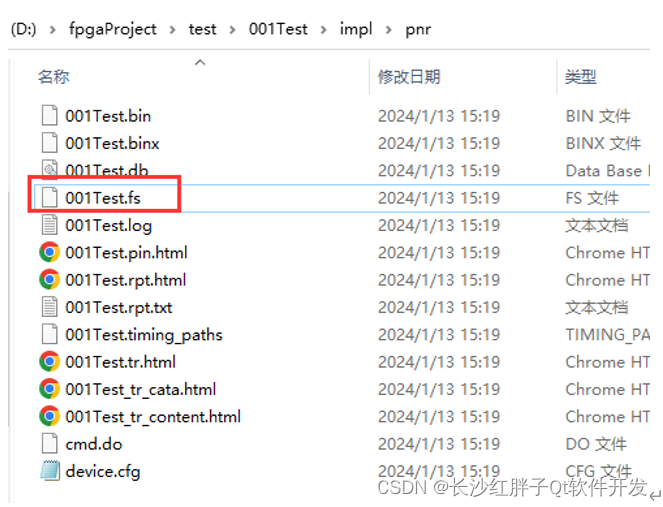

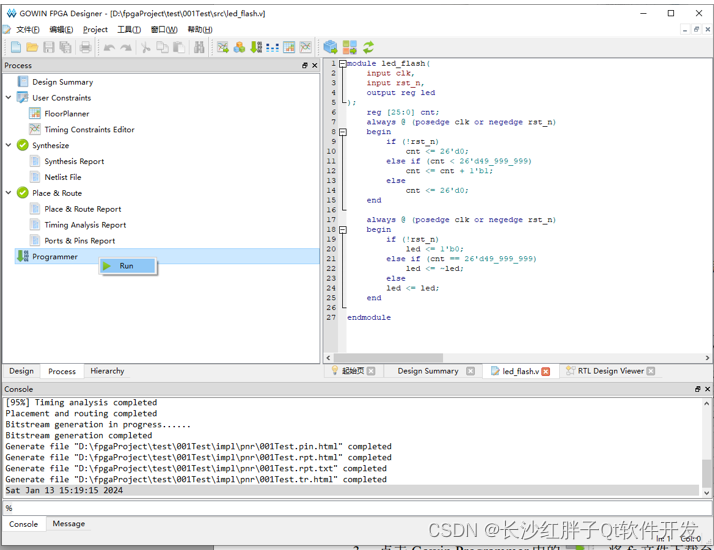

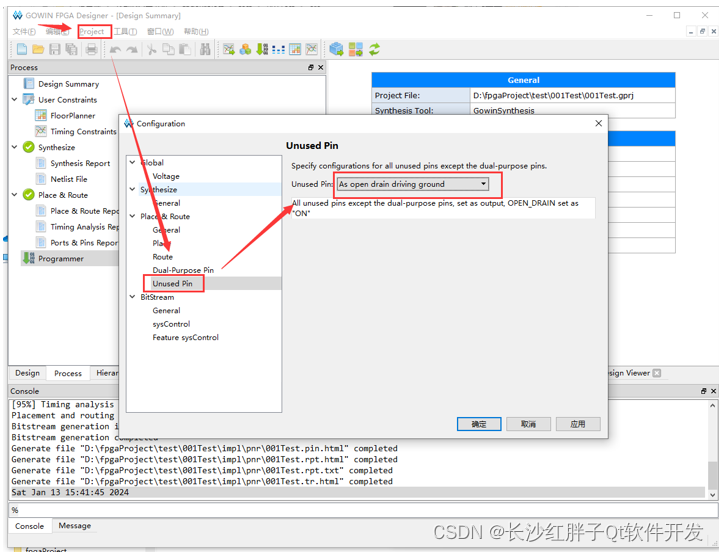

通过点击 Process->Place&Route 进行布局布线,布局布线成功便可看到“Bitstream generation completed”,此时代表fs文件生成成功,如下:

步骤七:板级验证(相当于单片机在线调试)

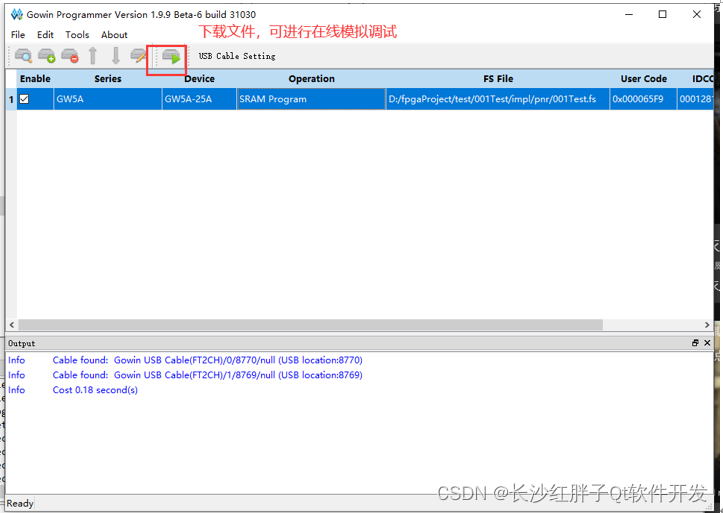

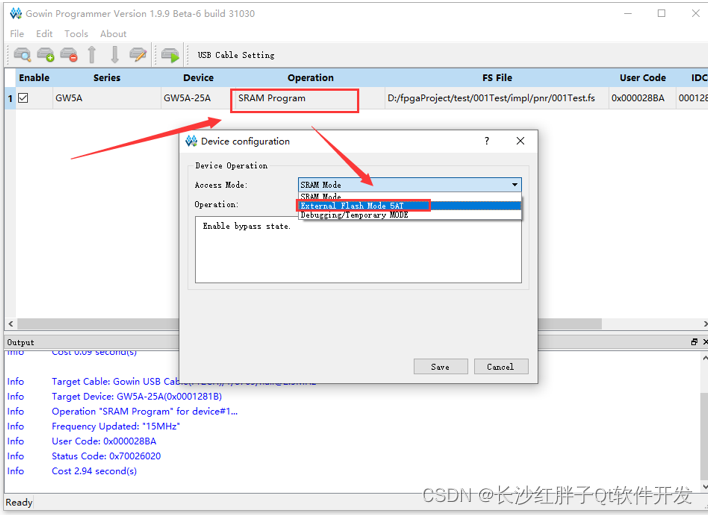

将fs文件下载到FPGA芯片中,用于完成对 FPGA 的配置:

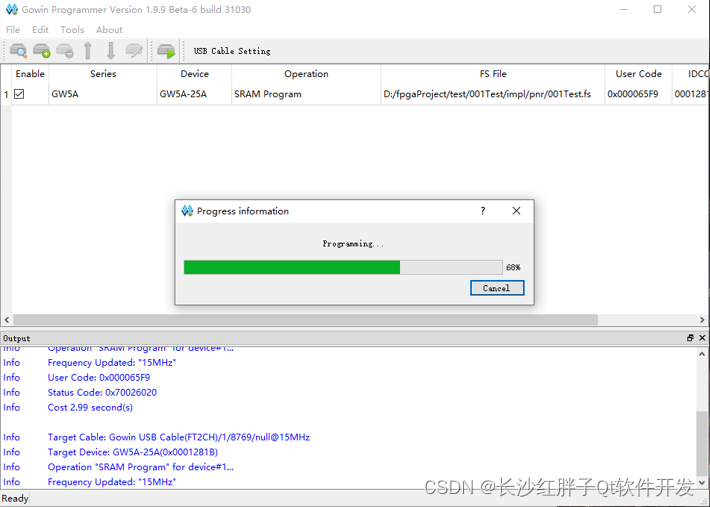

检测到了设备,确认编程:

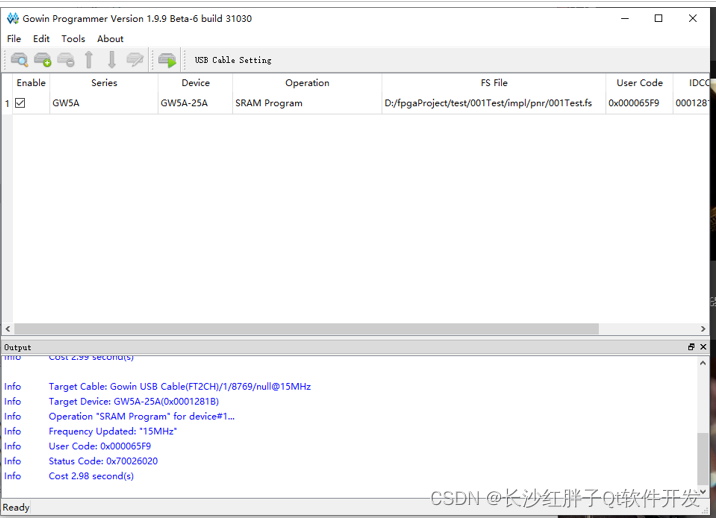

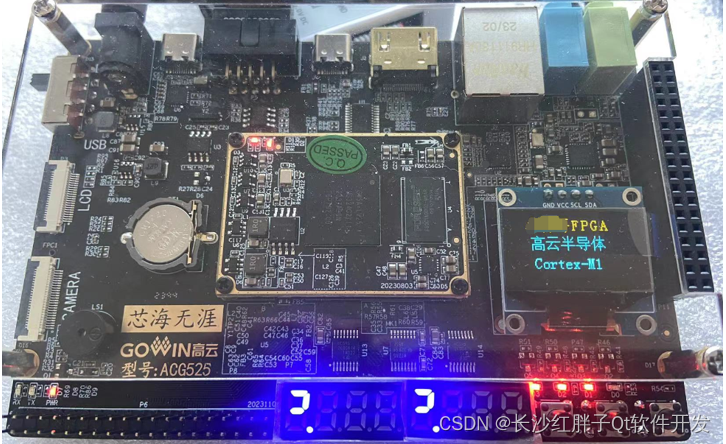

在线调试结果:

有三灯一直亮,可以配置下引脚输出为低电平(默认上拉高电平:

(这里是下下来直接运行了)

(注意:此时相当于单片机下载程序下去在线调试,断电后就没了,需要下载刷固件)

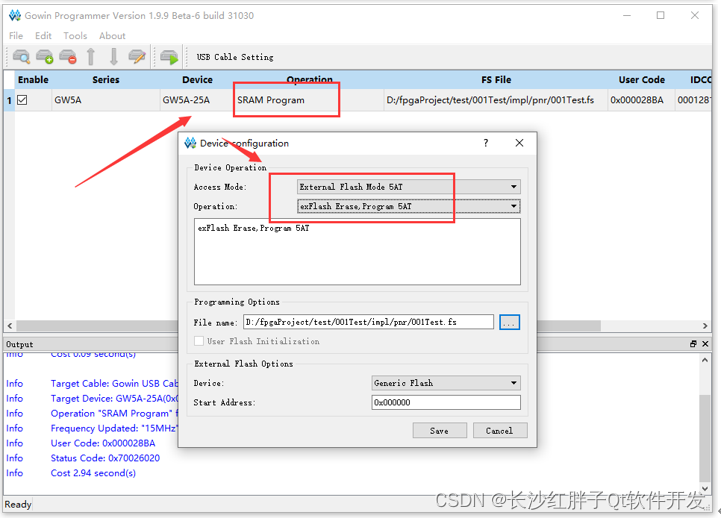

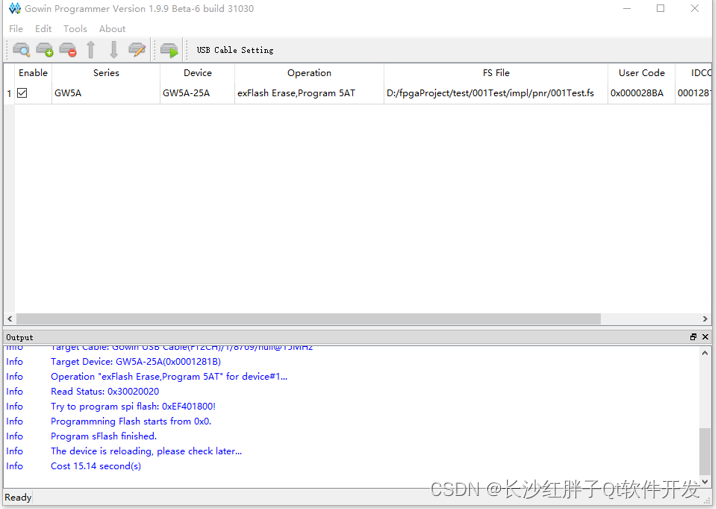

步骤八:程序固化(相当于下载程度到单片机上)

然后再在慢一些,下载完成:

入坑

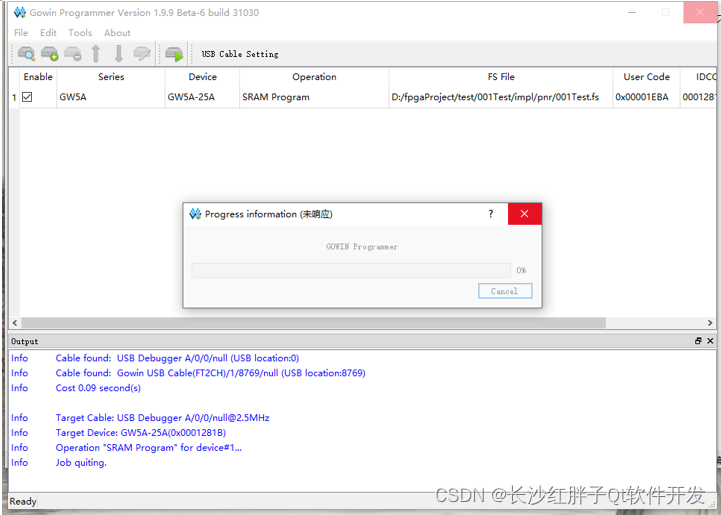

入坑一:下载程序卡死

问题

无响应卡死

原因

不清楚

解决

继续点击run可以开第二个这个窗口,就可以下载,测试发现第一个必然卡死,卡死的前提下开第二个,第二个可以下载,要是关了再开也是一个,还是卡死,当作是这个下载软件的bug了。

入坑二:下载后LED0不闪烁

问题

不闪烁,四灯全亮

原因

未约束管脚输出

解决

要配置好引脚约束(实际就是配置引脚输出)

上一篇:《Fpga开发笔记(一):高云FPGA芯片介绍,入手开发板套件、核心板和底板介绍》

下一篇:敬请期待…

本文章博客地址:https://hpzwl.blog.csdn.net/article/details/135620590