- 1一文详解多模态大模型发展及高频因子计算加速GPU算力 | 英伟达显卡被限,华为如何力挽狂澜?_dalle重塑技术

- 2GPT-4劲敌Claude 3来了,上下文和多模态显著提升:OpenAI是可被超越的

- 3【吴恩达】prompt engineering(原则 迭代 文本概括 推断、订餐机器人)

- 4Docker 操作mongo_docker exec -it mongo mongo admin

- 5pycharm无法识别conda环境(已解决)_pycharm检索不到虚拟环境

- 6【自然语言处理】【知识图谱】知识图谱表示学习(一):TransE、TransH、TransR、CTransR、TransD

- 7AI大模型学习:理论、实践与未来展望_ai大模型技术进展学习心得

- 8DevOps生命周期的基本指南

- 9使用vscode编写、运行Python程序_vscode运行python

- 10nltk.download()报错getaddrinfo failed_nlgetaddrinfo failed

GT收发器第六篇_GT channel内部时钟关系

赞

踩

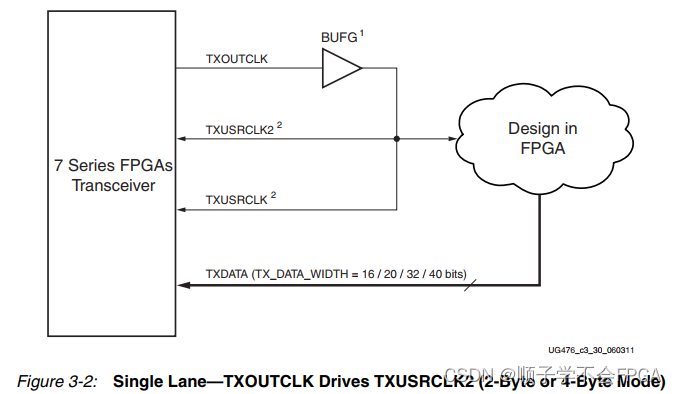

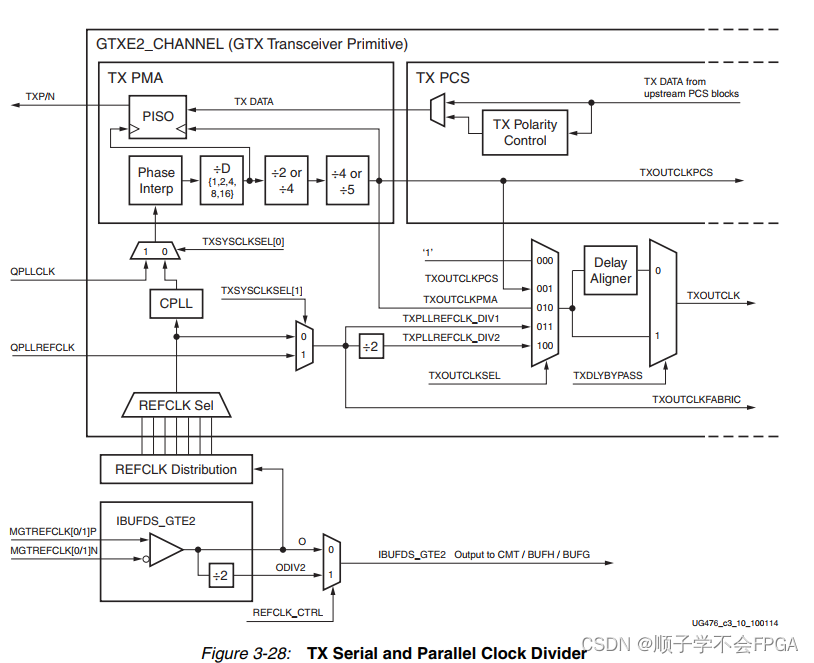

一、TX端时钟

TX端可分为4个区域,分别为FPGA TX接口、PCS靠FPGA侧、PCS靠PMA侧、PMA,如下图。GTX/GTH发射器包括TXBUFFER和TX相位校准电路,以解决时钟域之间的相位差。TX相位校准电路用于TXBUFFER被旁路时。所有TX数据路径必须使用TXBUFFER或TX相位校准电路。

- FPGA TX接口位于TXUSCLK2时钟域内。

- PCS靠FPGA侧位于TXUSCLK时钟域内。

- PCS靠PMA侧位于XCLK时钟域内。(若使能TXBUFFER,XCLK和TXUSCLK的相位调整由FIFO完成)

- PMA位于TX Serial Clk时钟域内(来源于参考时钟)。

时钟间关系:

TXUSCLK2和TXUSCLK来源于TXOUTCLK。

TXOUTCLK来源于QUAD的参考时钟。XCLK来源有两个,一个是TXOUTCLK,一个是TXUSCLK,具体是由TX_XCLK_SEL进行选择,具体如下:

(1)如果使能TXBUFFER,则XCLK来源于TXOUTCLK。

(2)如果旁路TXBUFFER(即使能相位锁定功能),则XCLK来源于TXUSCLK(则PCS内无相位锁定问题)。TX相位对准电路用于调整PISO并行时钟域与TX XCLK域之间的相位差,从而将数据从PCS传输到PISO。

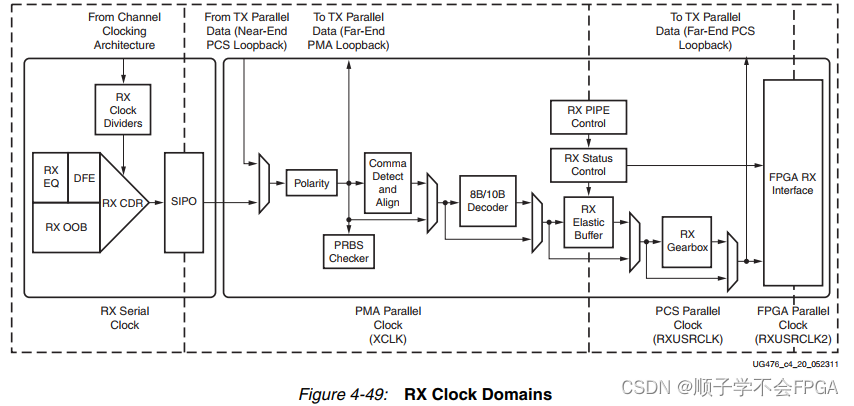

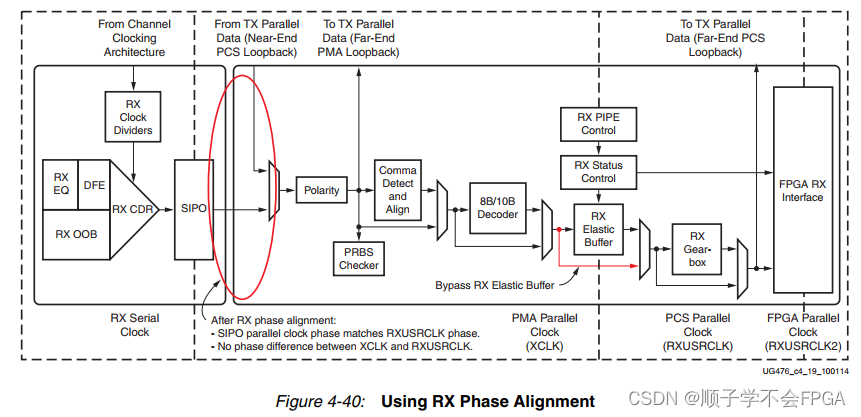

二、RX端时钟

- FPGA RX接口位于RXUSCLK2时钟域内。

- PCS靠FPGA侧位于RXUSCLK时钟域内。

- PCS靠PMA侧位于XCLK时钟域内。(若使能TXBUFFER,XCLK和TXUSCLK的相位调整由FIFO完成)

- PMA位于RX Serial Clk时钟域内(来源于线路恢复时钟)。

时钟间关系:

RXUSCLK2和RXUSCLK来源于RXOUTCLK或者TXOUTCLK(具体可见线路恢复时钟的介绍),TXOUTCLK来源于QUAD的参考时钟,RXOUTCLK来源于QUAD的参考时钟或者线路恢复时钟。XCLK来源有两个,一个是RXREC(恢复时钟),一个是RXUSCLK,具体是由RX_XCLK_SEL进行选择,具体如下:

(1)如果使能弹性缓冲区,则XCLK来源于RXREC。

(2)如果旁路弹性缓冲区(即使能相位锁定功能),则XCLK来源于RXUSCLK(则PCS内无相位锁定问题)。RXOUTCLK必须来自SIPO恢复的时钟(因为RXOUTCLK来源于QUAD的参考时钟或者线路恢复时钟),RXUSRCLK必须来自RXOUTCLK(因为RXUSCLK2和RXUSCLK来源于RXOUTCLK或者TXOUTCLK)。

小结:

主要是对于TXBUFFER和接收弹性缓冲区的理解,在使用缓冲区或者使用相位锁定电路时,不同的时钟对应关系。可以结合线路恢复时钟的介绍进行阅读。