热门标签

热门文章

- 1Air724UG 核心板学习记录-开发板介绍

- 2看大神如何用python爬虫爬取京东商品评论_python爬虫爬取京东电商平台商品评论,要求根据商品关键字爬取

- 3探索【Stable-Diffusion WEBUI】的附加功能:图片缩放&抠图_4x-ultrasharp

- 4AI程序员的出现与程序员的未来:饭碗之争的真相

- 548位一作相聚CVPR 2024预讲会/附全部议程

- 6Flask之ajax操作示例_flask 处理 ajex

- 7LLaMA模型指令微调 字节跳动多模态视频大模型 Valley 论文详解_valley: video assistant with large language model

- 8(五)比赛中的CV算法(下)目标检测终章:Vision Transformer_为什么不用vision transformer 做bacbone 进行目标检测

- 9包含密钥的OMP压缩感知模拟(MATLAB)

- 10备战蓝桥杯,用JAVA刷洛谷算法题单:【算法2-1】前缀和、差分与离散化

当前位置: article > 正文

FIFO原理及其应用

作者:小小林熬夜学编程 | 2024-04-05 19:28:31

赞

踩

fifo

1 FIFO原理

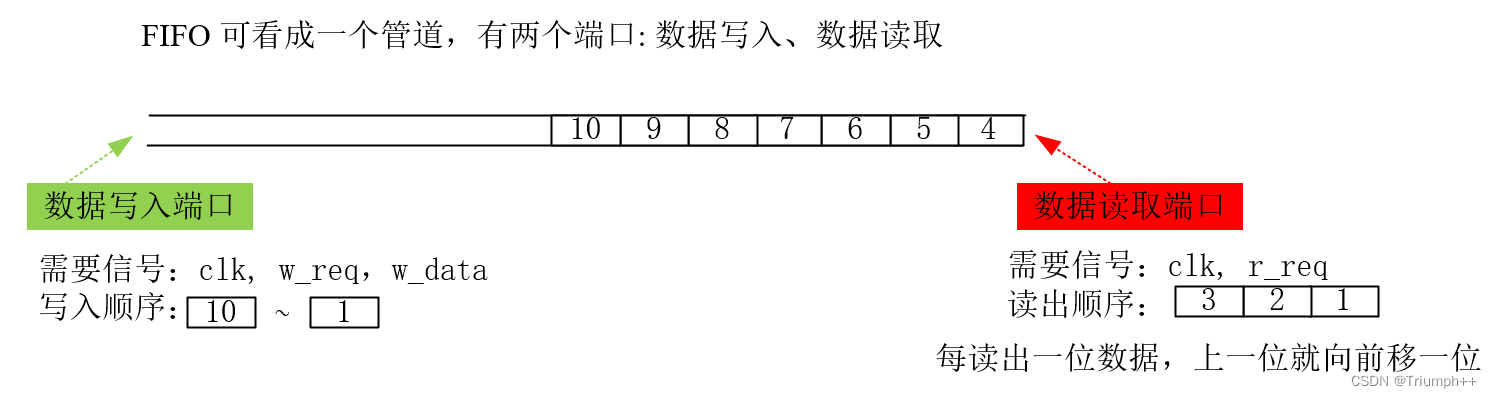

FIFO(First In First Out,即先入先出),是一种数据缓冲器。先被写入的数据会按顺序先被读出。FIFO可看做一个管道,有数据写入端口和 数据读取端口:

如图,数据写入端口从1~10依次写入数据,则数据读取端口也从1~10依次读取数据。输出端口每读出一位数据,FIFO中的后一位数据就向前移一位。如读取端口读出1、2、3后FIFO输出端口的第一位变为4。

1.1 FIFO的使用

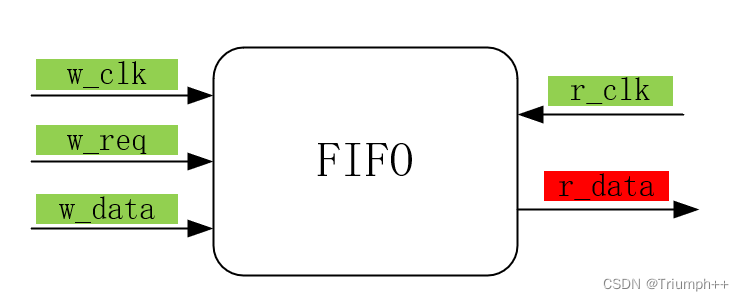

写数据端口:

- w_clk : 写数据时钟信号

- w_req : 写请求信号

- w_data : 要写入的数据

读数据端口:

- r_clk : 读数据时钟信号

- r_data : 读出的数据

1.2 FIFO的分类

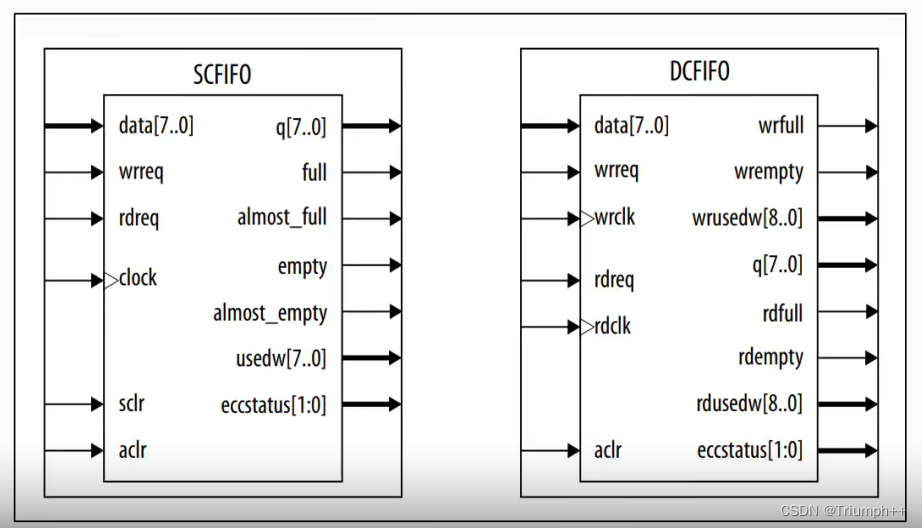

- SCFIFO (同步FIFO) : w_clk 和 r_clk 一致

- DCFIFO (同步FIFO) : w_clk 和 r_clk 不一致

1.3 读取数据的模式

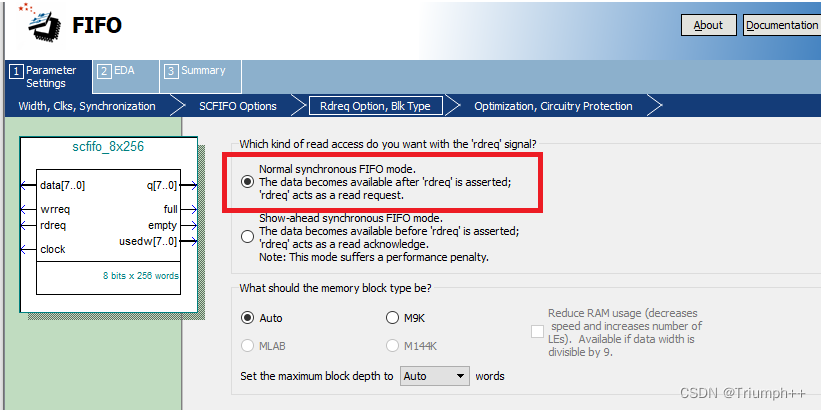

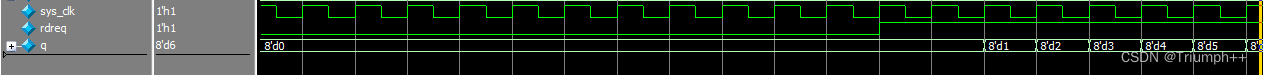

(1) 普通同步FIFO模式

设置:

读取数据波形:

数据输出q滞后读请求信号rdreq一个时钟周期!

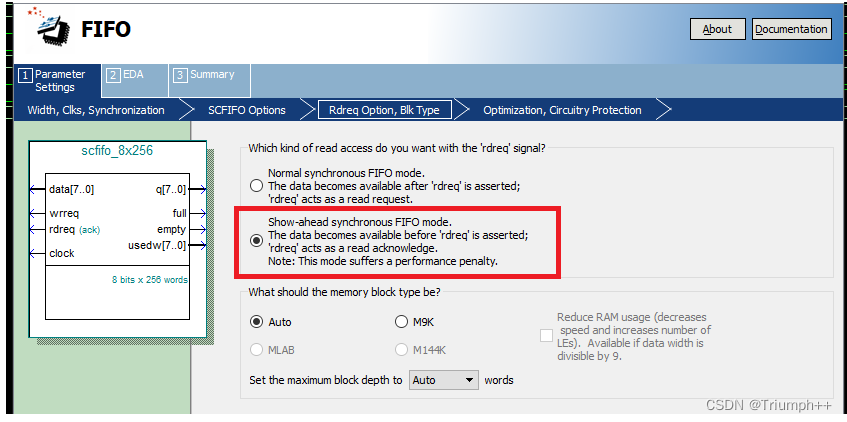

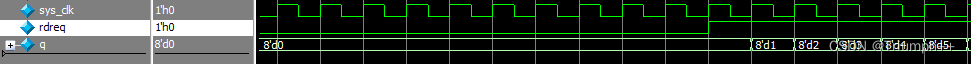

(2) 先出数据FIFO模式

设置:

读取数据波形:

rdreq有效立即输出信号,rdreq信号与数据输出q同步!

2 FIFO的应用

2.1 多bit数据做跨时钟域转换

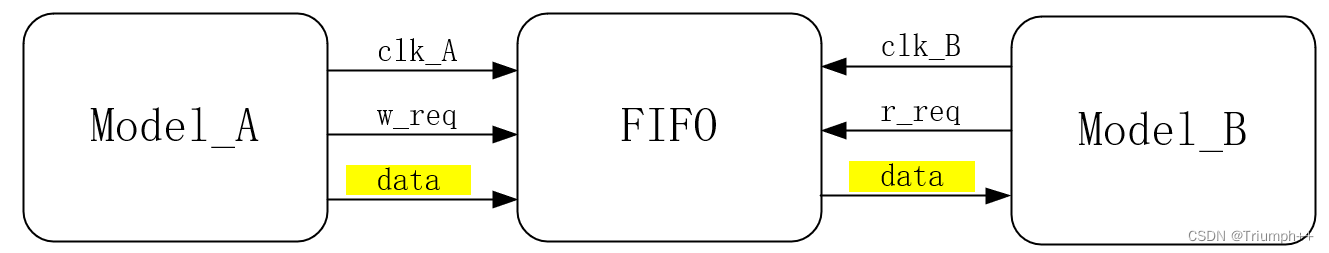

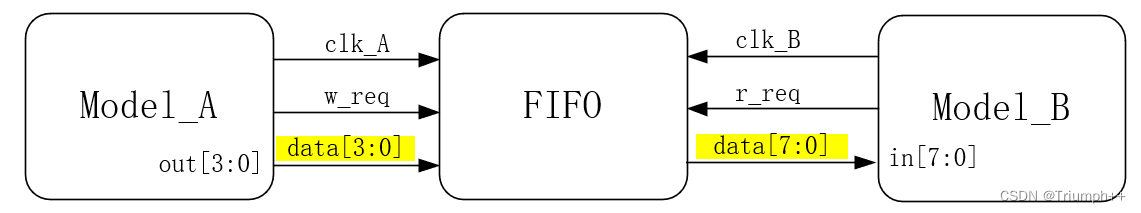

当两个模块的时钟不一致,它们之间需要进行数据传输时。(如A模块的数据需要传输到B模块进行处理),此时就需要做跨时钟域处理。先把模块A的数据按照clk_A写入FIFO,然后模块B再按clk_B读取FIFO中的数据,因此数据data在模块B中就能得到正确的处理!

2.2 带宽同步

当两个模块的数据传输端口带宽不一致,其它们之间需要进行数据传输时。此时就需要做带宽同步处理。 先把模块A的数据按照clk_A写入FIFO(设模块A输出的数据位宽为4,此时也把FIFO的数据写入端口位宽设置为4),然后模块B再按clk_B读取FIFO中的数据(设模块B输入的数据位宽为8,此时也把FIFO的数据读取端口位宽设置为8),从而实现了带宽同步。

此时数据拼接的方式为:

即两个数据位宽为 4 的数据拼接为 一个数据位宽为8的数据,先输入的为高4位,后一位为低4位!

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小小林熬夜学编程/article/detail/367568

推荐阅读

相关标签