- 1js 将数组返回带children的递归数组

- 2PYQT5 004 多窗口_pyqt5多窗口

- 3程序员们一个一个的都挺神的,堪称 35 岁毕业之后再就业的标兵,不服不行_程序员再就业

- 4使用Flask和Flask-JWT-Extended保护API免受跨站请求攻击

- 5稀碎从零算法笔记Day52-LeetCode:从双倍数组中还原原数组

- 6新手程序员试用期指南 | 职场必备法则_程序员入职后要熟悉多久

- 7Java类加载_-xx:reservedcodecachesize

- 8Mujoco Humanoid环境介绍_humanoid mujoco

- 9RK3566系统移植:基于RK-Linux-SDK移植U-Boot的嵌入式方案

- 102023年NOC大赛加码未来编程赛道-初赛-Python(小学高年级组-卷2),包含答案解析_noc ai创新编程 初中组

STM32单片机学习全集(来自江科大自化协)_stm32单片机教程 csdn

赞

踩

1.C语言和基本外设

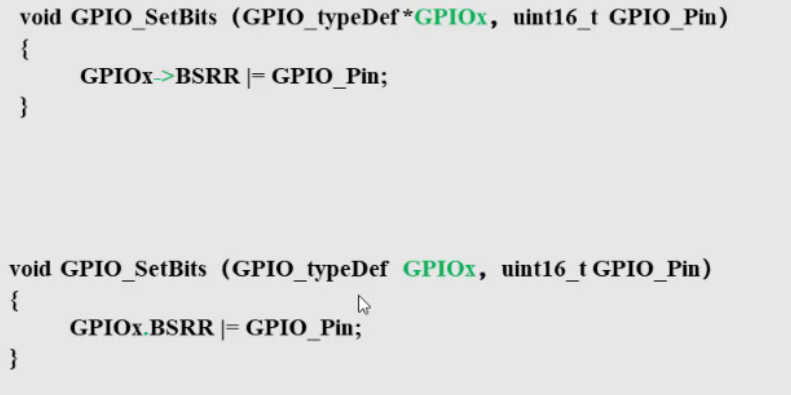

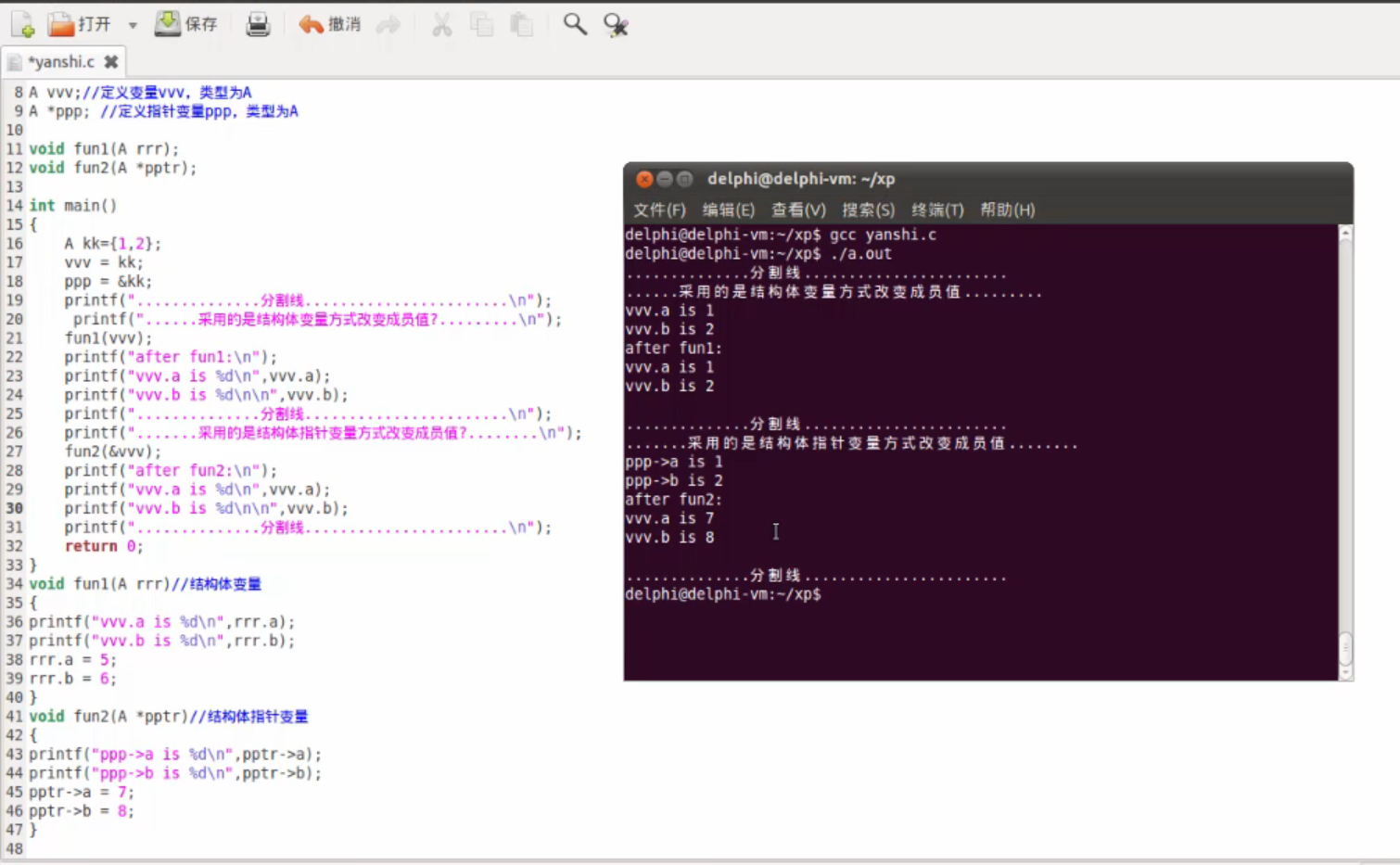

1.1指针

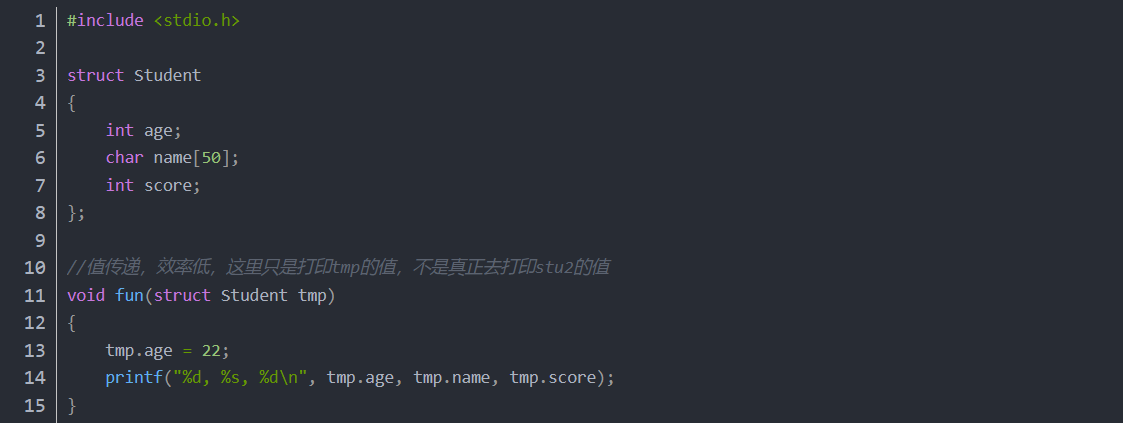

1.1.1结构体指针:

这两种形式并不一样,原因在于若使用.的形式传递,无返回值等于没有进行传递。

多变量函数参数传递:

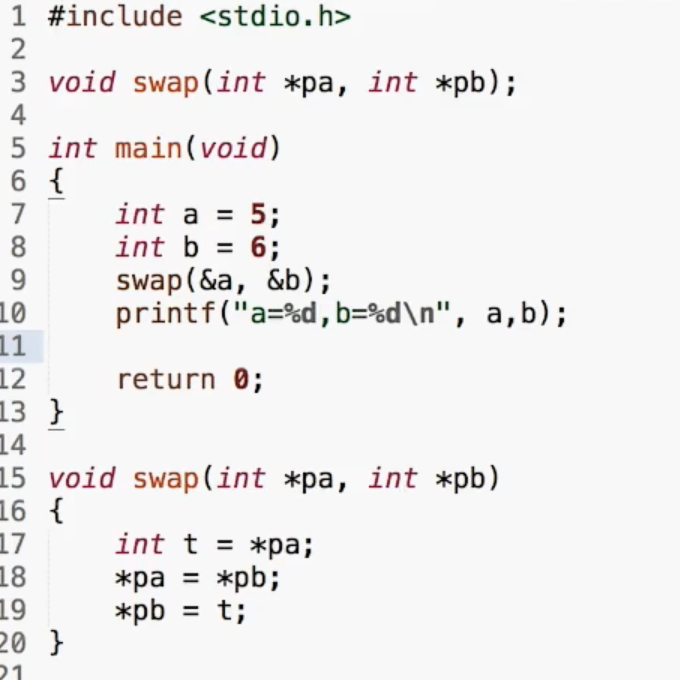

在函数内部只做运算而不输出值,指针其实就是地址。用&取地址给他传递参数,在函数内部做运算的其实就是传进去的地址上的数。

若不使用指针,值是无法在内部进行传递的。

1.1.2结构体的值传递和址传递

下面是址传递:

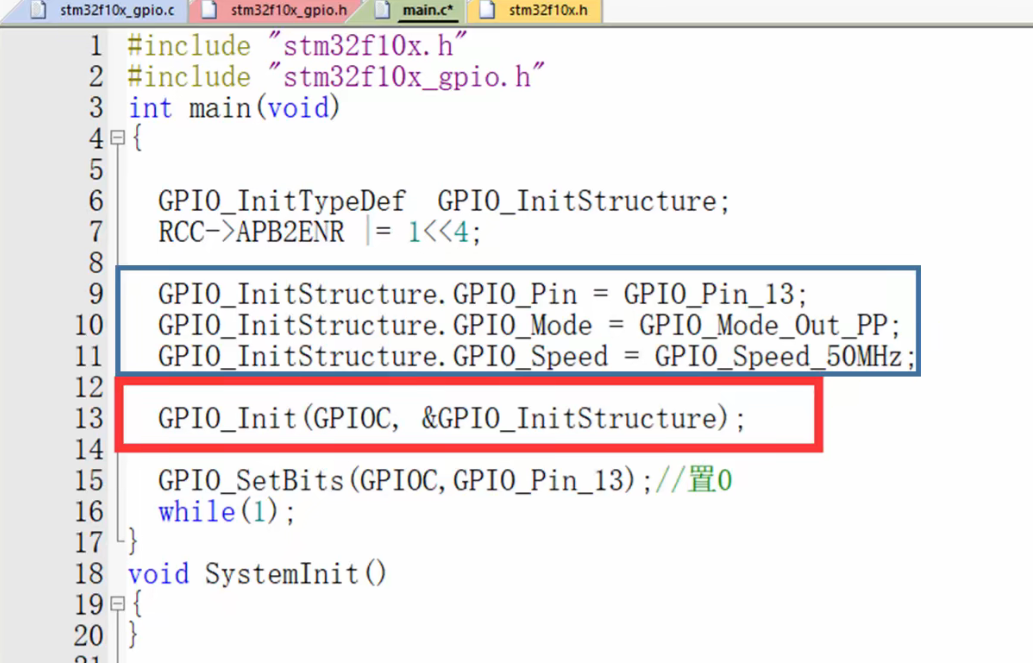

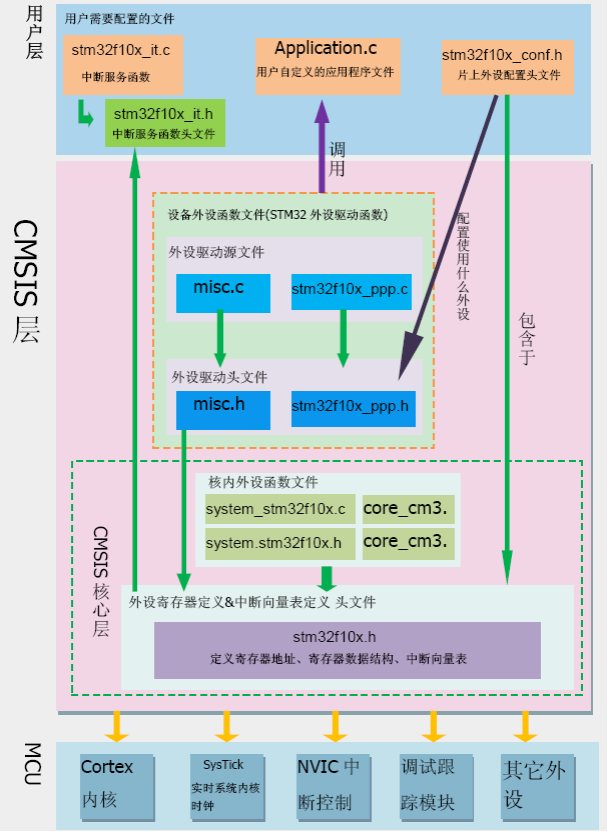

1.2库函数格式

配置库函数就是配置这些函数文件。

片上外设指的是芯片内部除了内核以外的外设。

NVIC:嵌套向量中断控制器。stm32f10x_ppp.c和stm32f10x_ppp.h,ppp代表外设

stm32有唯一的96位ID,可用于加密或者识别。

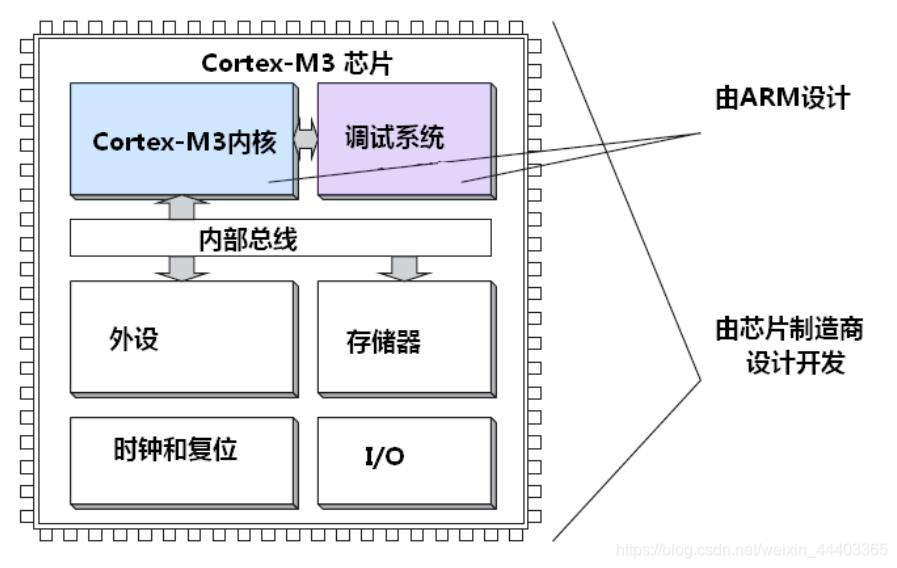

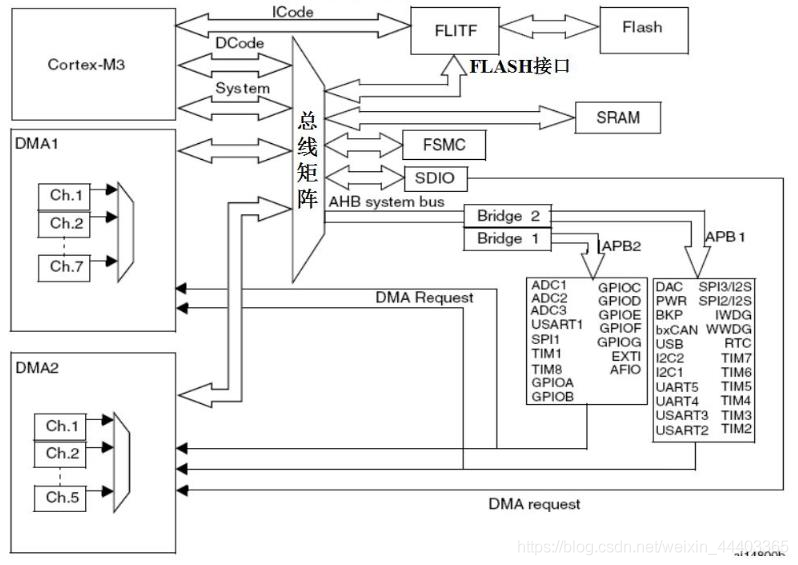

1.3stm32F10x结构

除掉内核以外的外设称为片上外设:

具体结构:

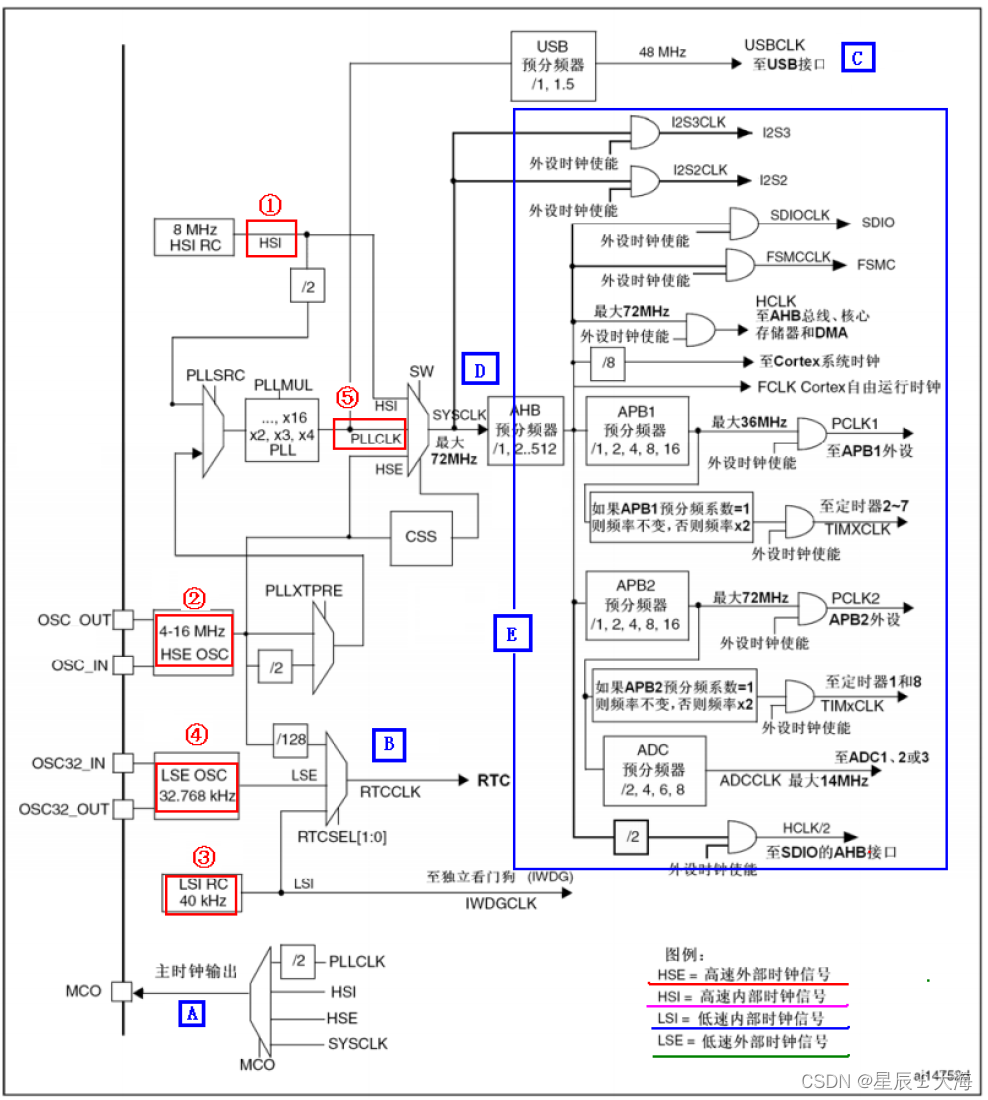

时钟:

2.GPIO

2.1三极管

NPN(箭头向外)三极管,若三极管导通,则必然要有电流流过ce或ec,也就是三极管CE两侧必须要有电源。(集电极要高,发射极要低),电子由发射极到基极的定向移动引起发射极到集电极的电子定向移动。(电子移动共两个回路)

硅材料三极管基极电压<0.6v,eb就不导通,此时截止

当电压处于0.6v~0.7v时,Ic=βIb,此时对cb端有放大作用

当电压>0.7v时,处于饱和状态

PNP(箭头向内)三极管,若三极管导通,则要有电流从e流向c,此时电子由基极向发射极的定向移动引起集电极电子向发射极移动。电流方向与之相反,箭头方向就是电流的方向。

开关电路利用三极管的截至和饱和,在0.6v~0.7v时,电流有线性放大关系。

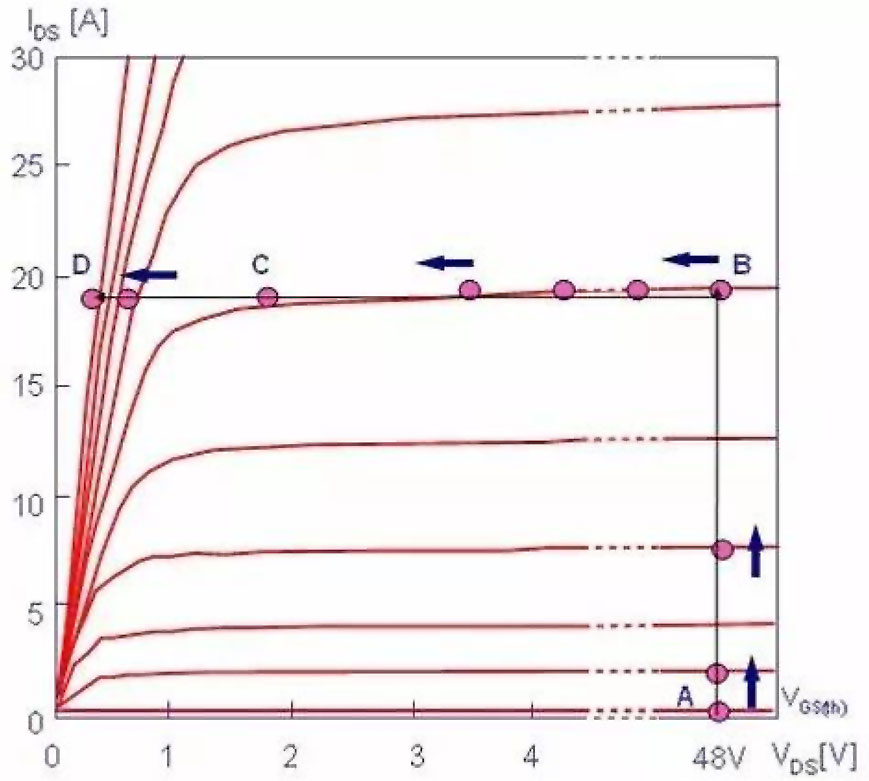

2.2mos管

给纯硅分别掺杂三价硼和五价磷,分别得到P型半导体和N极半导体,空穴带正电,自由电子带负电。对两种半导体进行掺杂,P区带正电的空穴会吸引N区带负电的自由电子,PN半导体放一起,就构成了二极管。

MOS管的栅极输入阻抗非常高,这是因为有绝缘层的存在,几乎限制了电子的定向运动。符号代表了电子的运动方向。把所有竖着的黑线当成是铁板,实际上三极管的N沟道产生的原理就是电容的电荷聚集。

下面是他的伏安特性曲线:

2.2GPIO的8种工作模式:

控制寄存器CR,状态寄存器SR,数据寄存器DR。

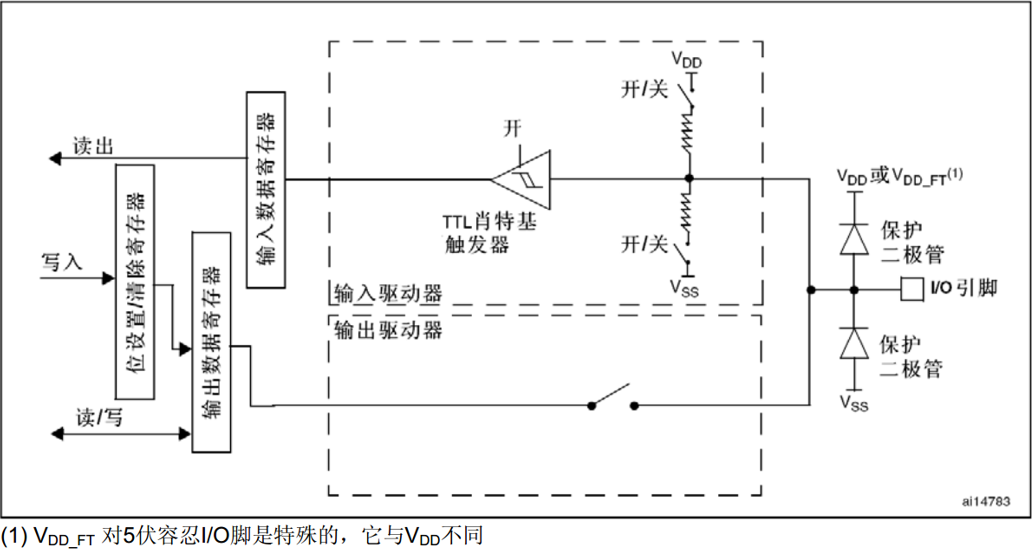

浮空输入_IN_FLOATING/带上拉输入_IPU/带下拉输入_IPD

浮空输入时,它可以接受外部过来的高电平或者低电平,经过两个保护二极管之后进入输入寄存器。输入寄存器再将数据输入到CPU中,CPU就能读取到外部输入的高低电平。

上下拉输入的区别在于上下拉电阻,一般是30kΩ~50kΩ,上拉是上拉到Vcc,下拉是下拉到GND。

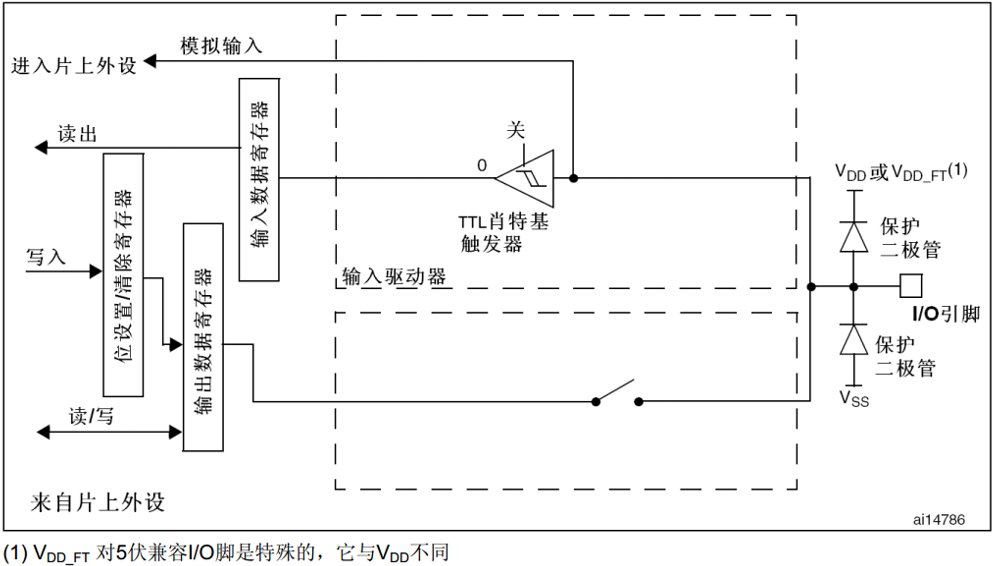

模拟输入_AIN:

此模式下,可以将外部进入的模拟量转换为数字量。(AD转换)

开漏输出_OUT_OD

开漏输出最主要的特性就是高电平没有驱动能力,需要借助外部上拉电阻才能真正输出高电平。

- 开漏输出的这一特性一个明显的优势就是可以很方便的调节输出的电平,因为输出电平完全由上拉电阻连接的电源电平决定。所以在需要进行电平转换的地方,非常适合使用开漏输出。

- 开漏输出的这一特性另一个好处在于可以实现"线与"功能,所谓的"线与"指的是多个信号线直接连接在一起,只有当所有信号全部为高电平时,合在一起的总线为高电平;只要有任意一个或者多个信号为低电平,则总线为低电平。而推挽输出就不行,如果高电平和低电平连在一起,会出现电流倒灌,损坏器件。

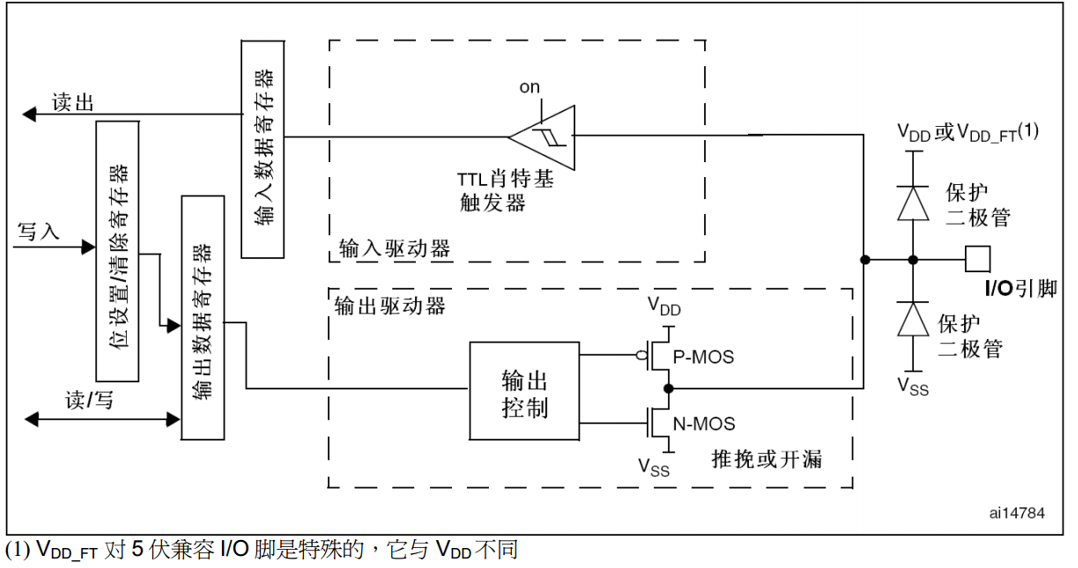

首先由 CPU 向 位设置/清除寄存器 中写入 1/0,然后 它 将电平的高低映射到 输出数据寄存器 中。随后再到 ② 输出控制电路 中, 若输出控制电路接收到 1(高电平),则 N-MOS管 截止。此时 I/O端口 处的电平不是通过接收到 1(高电平)的 输出控制电路 和截止的N-MOS管 来控制的,而是通过外部的 “上拉”或 “下拉”来决定(图五中未画出)。若 ② 输出控制电路 接收到 0(低电平),则③N-MOS管导通,此时 ④I/O端口处的电平被③N-MOS管拉低为低电平。

在输出状态下,④ I/O端口 的电平还可通过 ④ I/O端口 → ⑥ 输入数据寄存器 → ⑦ CPU读取 的线路读取(此状态在 ② 输出控制电路 接收到高电平“1”时启用)。

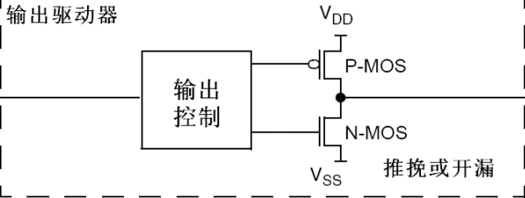

推挽输出_OUT_PP

推挽输出具有强驱动能力,输出高电平能力比开漏输出强很多,但推挽输出的一个缺点是,如果当两个推挽输出结构相连在一起,一个输出高电平,即上面的MOS导通,下面的MOS闭合时;同时另一个输出低电平,即上面的MOS闭合,下面的MOS导通时。电流会从第一个引脚的VCC通过上端MOS再经过第二个引脚的下端MOS直接流向GND。整个通路上电阻很小,会发生短路,进而可能造成端口的损害。这也是为什么推挽输出不能实现" 线与"的原因。

开漏复用输出_AF_OD/推挽复用输出_AF_PP

没什么不同,只是高低电平来自片上外设。

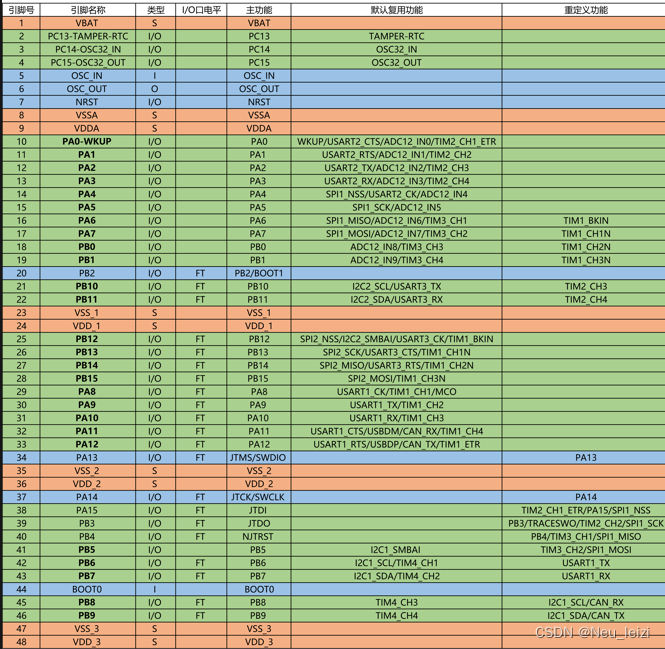

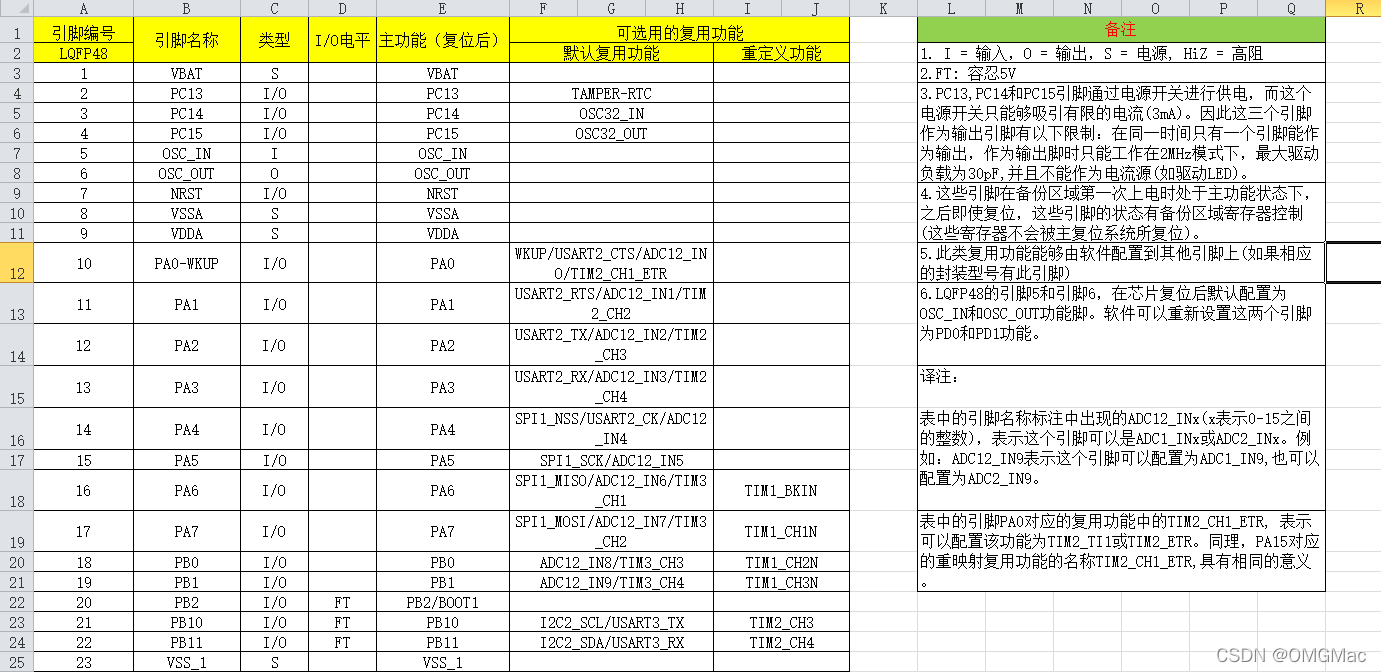

2.3GPIO引脚定义表

用四个位(十六进制数0~7)来表示各个引脚的工作模式。

3.EXTI和NVIC

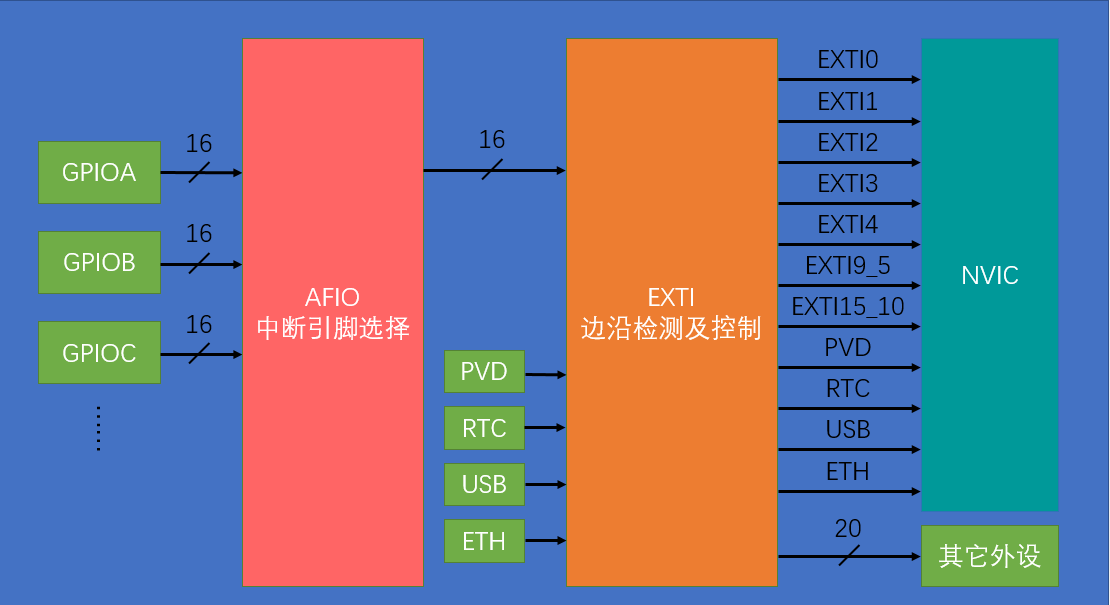

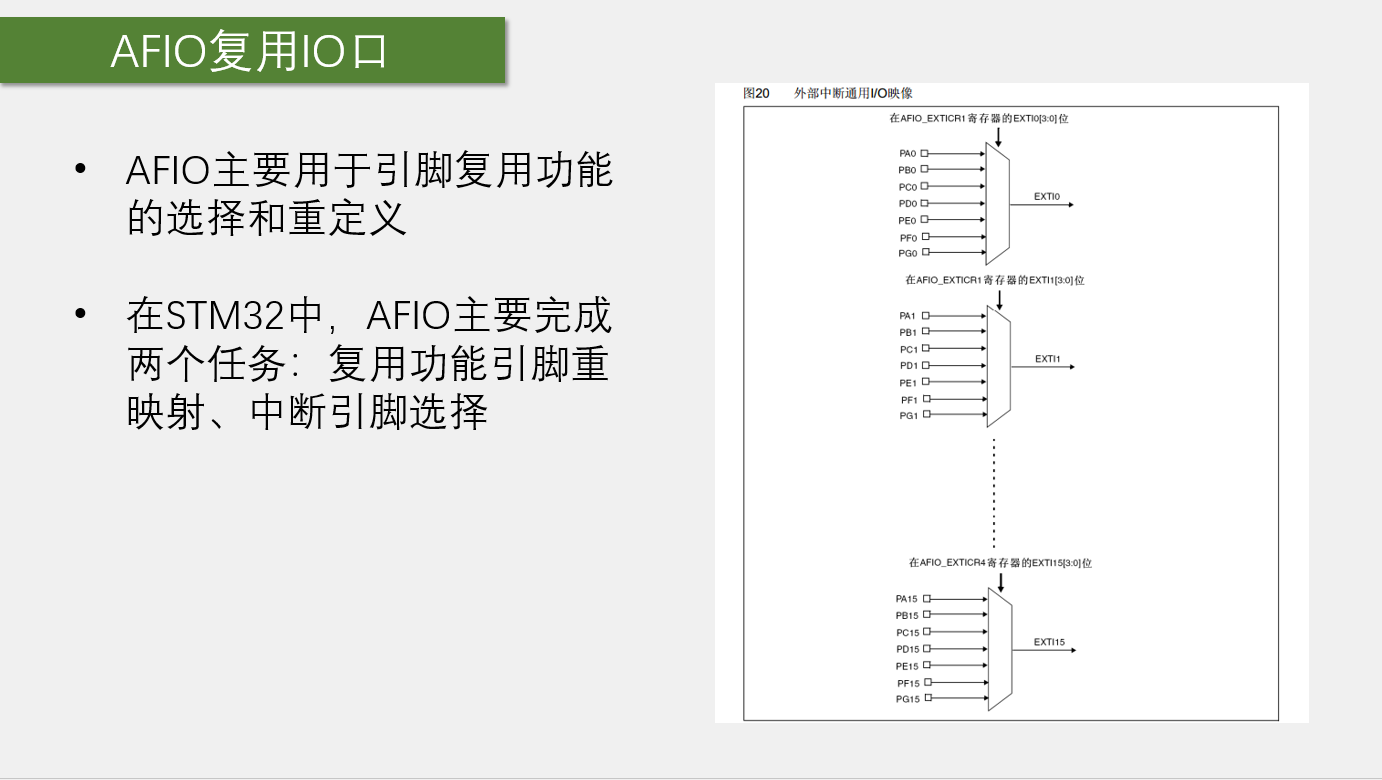

3.1EXTI基本结构

GPIO先经过AFIO配置进入EXTI的路,再通过EXTI进入NVIC。(按键等短时间变化的量不适合在中断中读取)

选择AFIO后再配置EXTI。

3.2NVIC

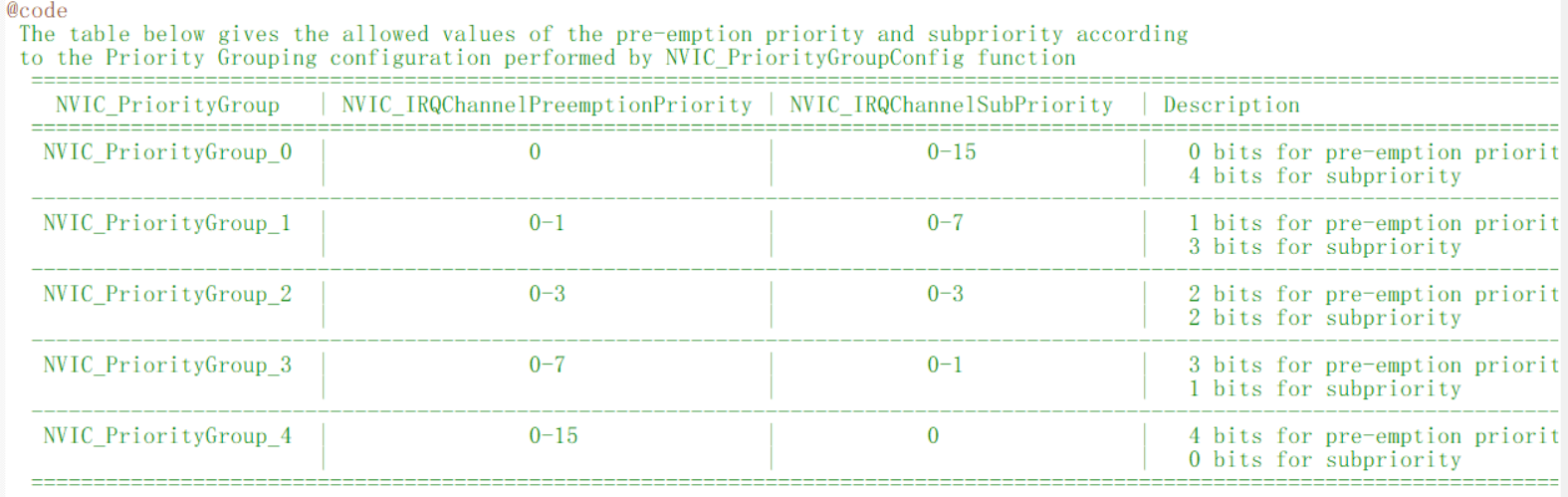

共五个位(0~4),按占位的方式来分配响应优先级和抢占优先级。(输入值十六进制数)

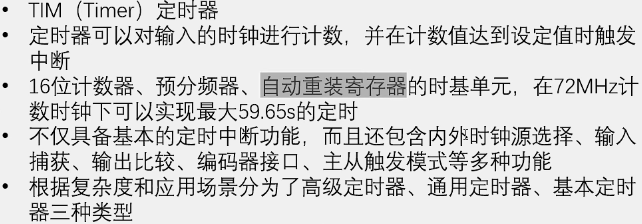

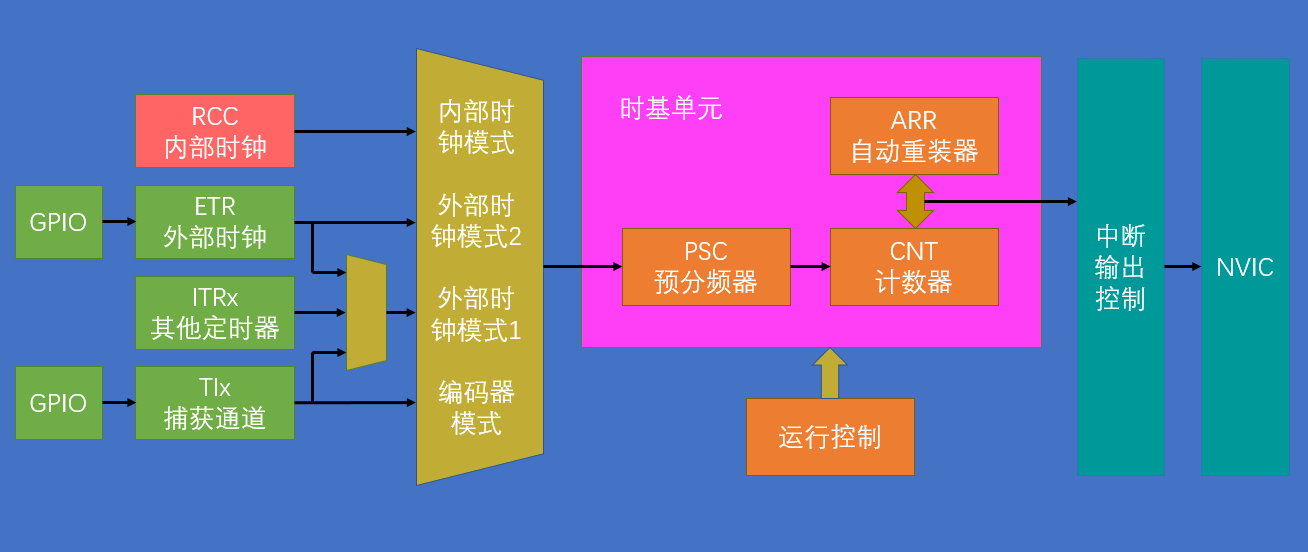

4.TIM定时器

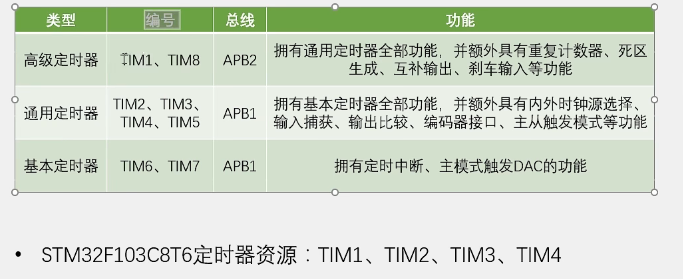

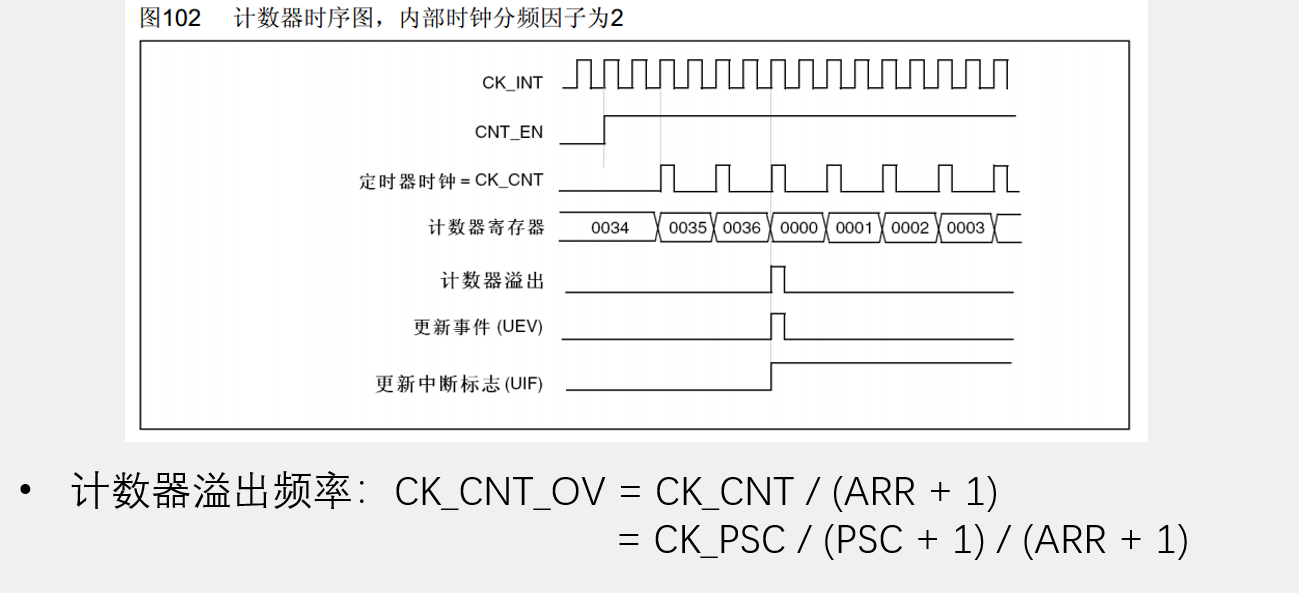

4.1时基单元:计数器,预分频器,自动重装寄存器

三者均是十六位,最长定时时间计算(支持定时器级联):

频率=72MHz/216(**预分频器**)/216(CNT计数器)

时间T=1/频率=59.65s

定时器类型:

基本定时器:

预分频器16位,实际分频系数=预分频系数+1(从零开始写)

计时器也是16位,最多计数216。当CNT自增到重装值216时,计数器清零,自动重装寄存器用来存储这一个值。

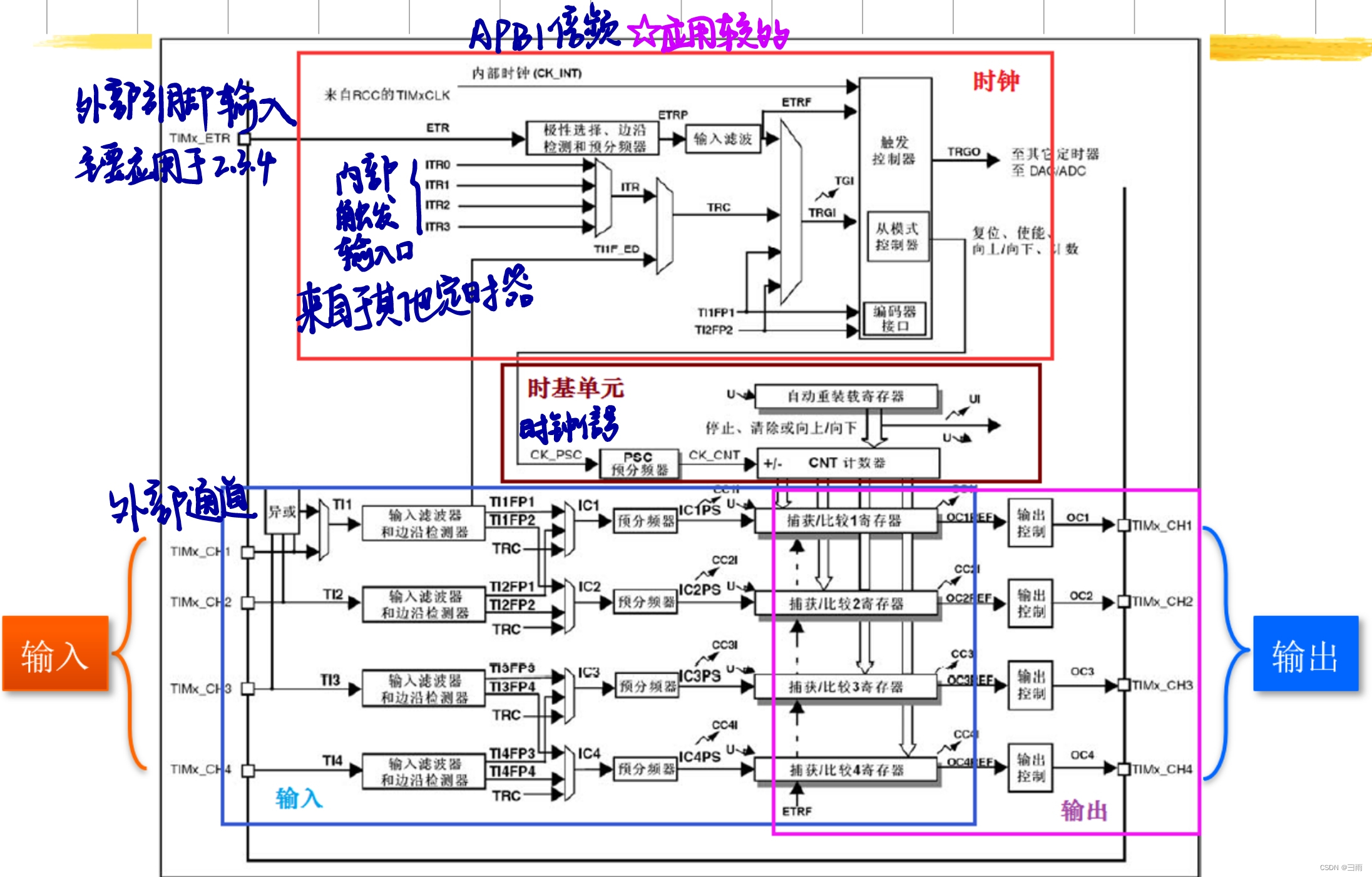

通用定时器:

支持向上计数,向下计数,中央对齐。时钟可以选择内部时钟,也可以选择外部时钟。

TIMx_ETR可以外接一个时钟,ETR接到TRGo这一路又叫外部时钟模式二。

SYSCLK=72M

AHB时钟=72M

APB1时钟=36M

所以APB1的分频系数=AHB/APB1时钟=2。所以,通用定时器时钟CK_INT=2*36M=72M

②外部时钟模式1:外部输入脚(TIx)

③外部时钟模式2:外部触发输入(ETR)

④内部触发输入(ITRx):使用一个定时器作为另一个定时器的预分频器,如可以配置一个定时器Timer1而作为另一个定时器Timer2的预分频器。

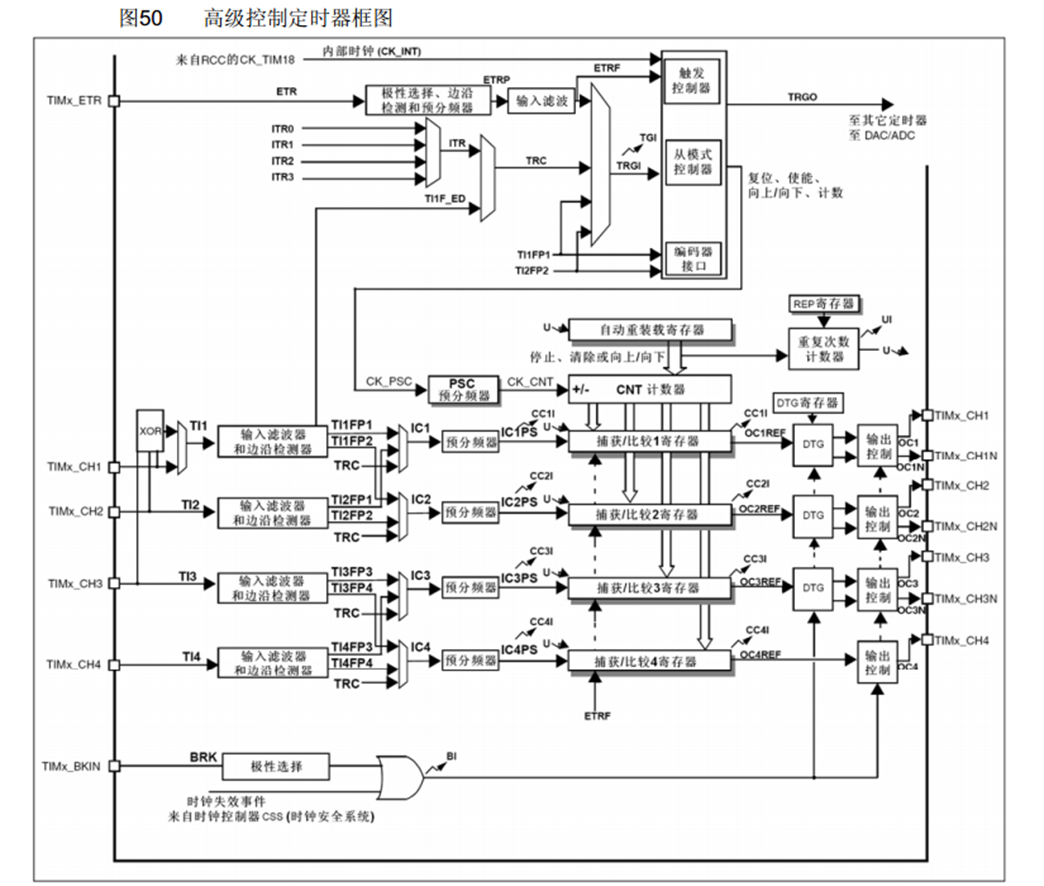

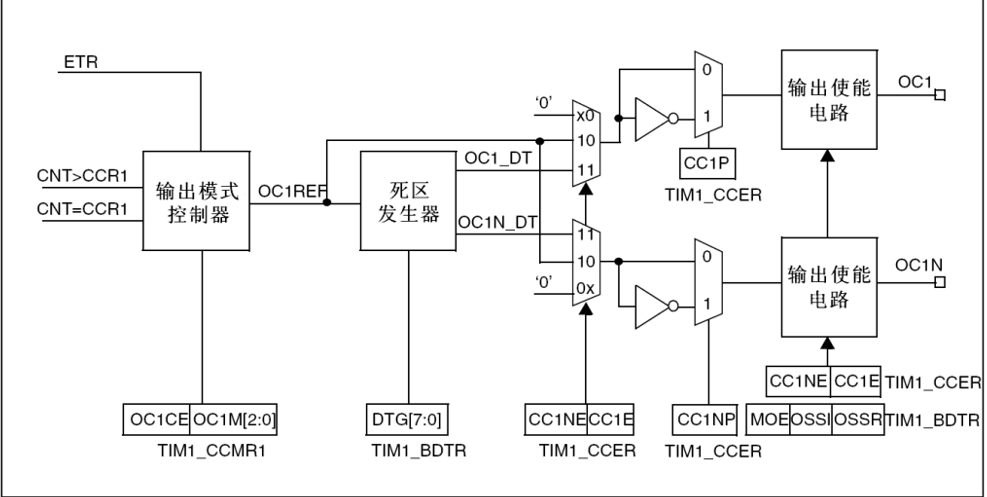

高级定时器:

为保证PWM驱动电机时产生的互补PWM波发生直通现象(直通现象会导致桥臂出现快速上升的大电流),故PWM开关切断输出时要产生一定的死区(DTG的作用)。

刹车输入给电机驱动提供保障,刹车信号或内部时钟故障,TIMx_BKIN会切断电机的输出。

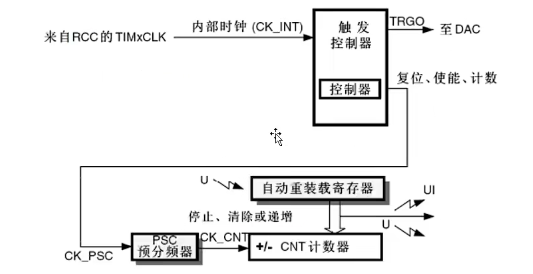

定时器基本结构:

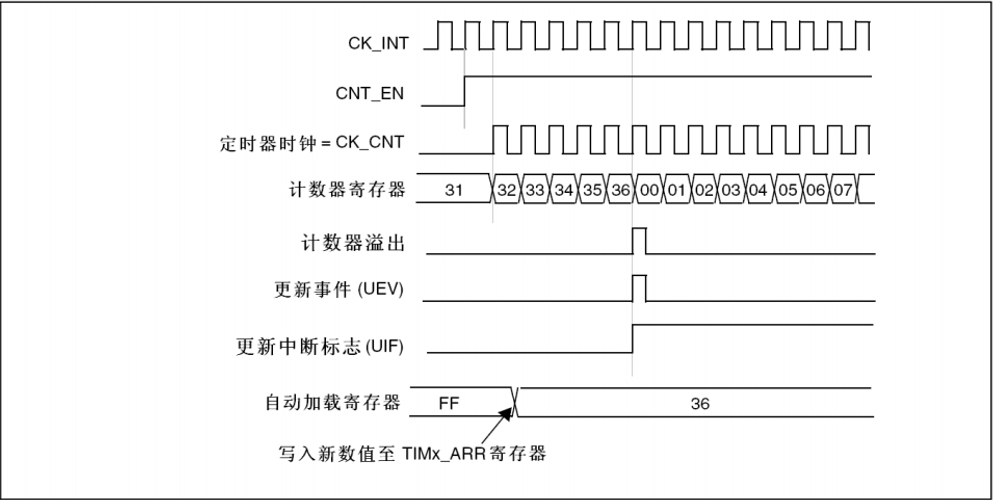

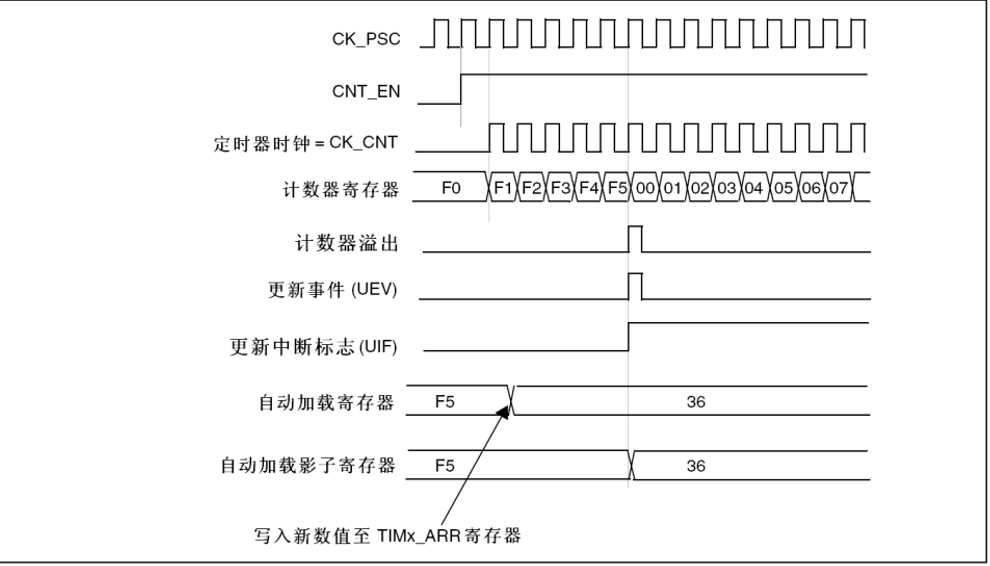

4.2CNT和预分频器时序逻辑

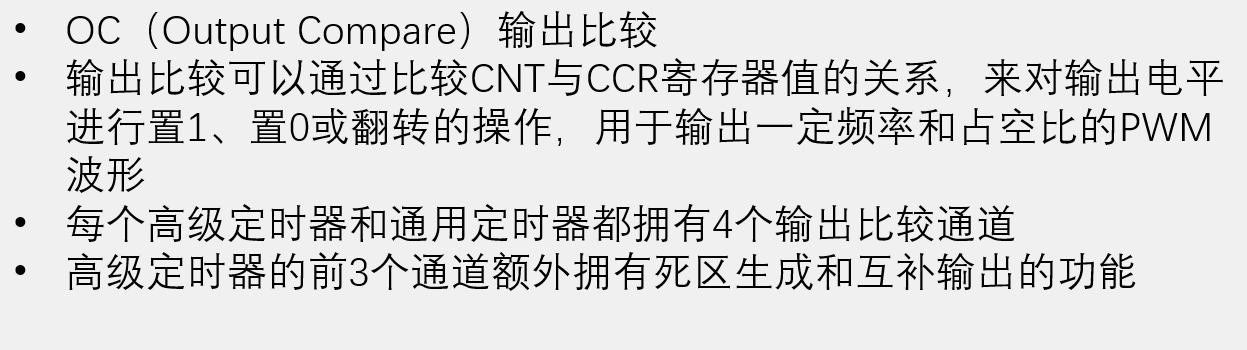

4.3输出比较

CCR:捕获比较寄存器

两个重要参数:频率和占空比。频率大,但性能开销大。

CNT>CCR1或CNT=CCR1时,改变OCIREF(参考信号)的值,经过TIM_CCER选择(是否翻转高低电平)之后,输出使能电路判断之后决定是否继续向外输出。

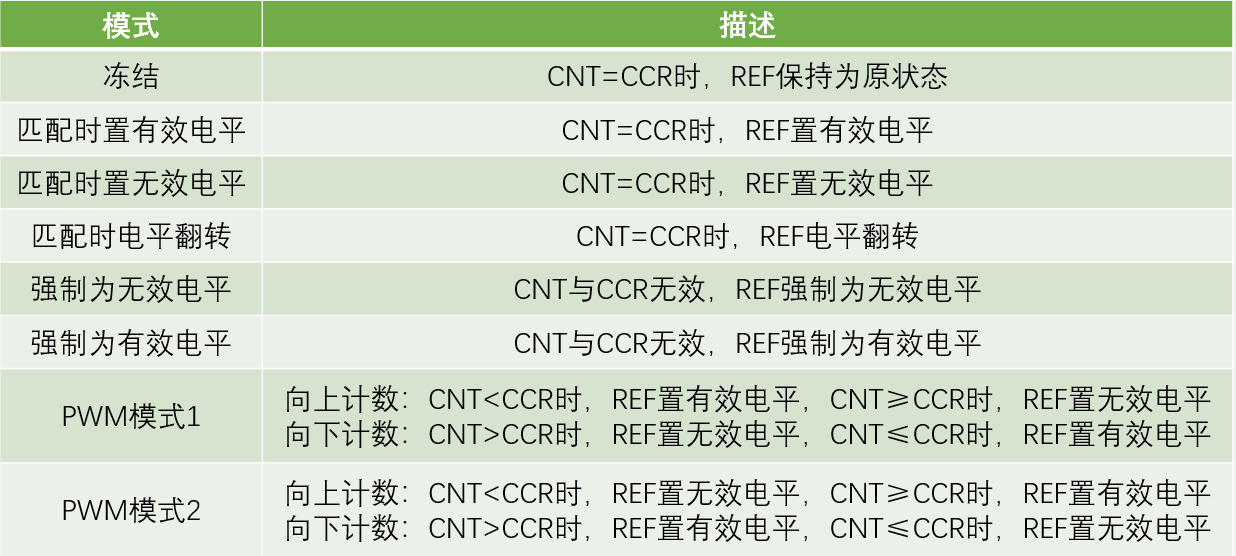

输出比较的八种模式如下图:

pwm模式一和模式二的区别在于REF电平是否翻转

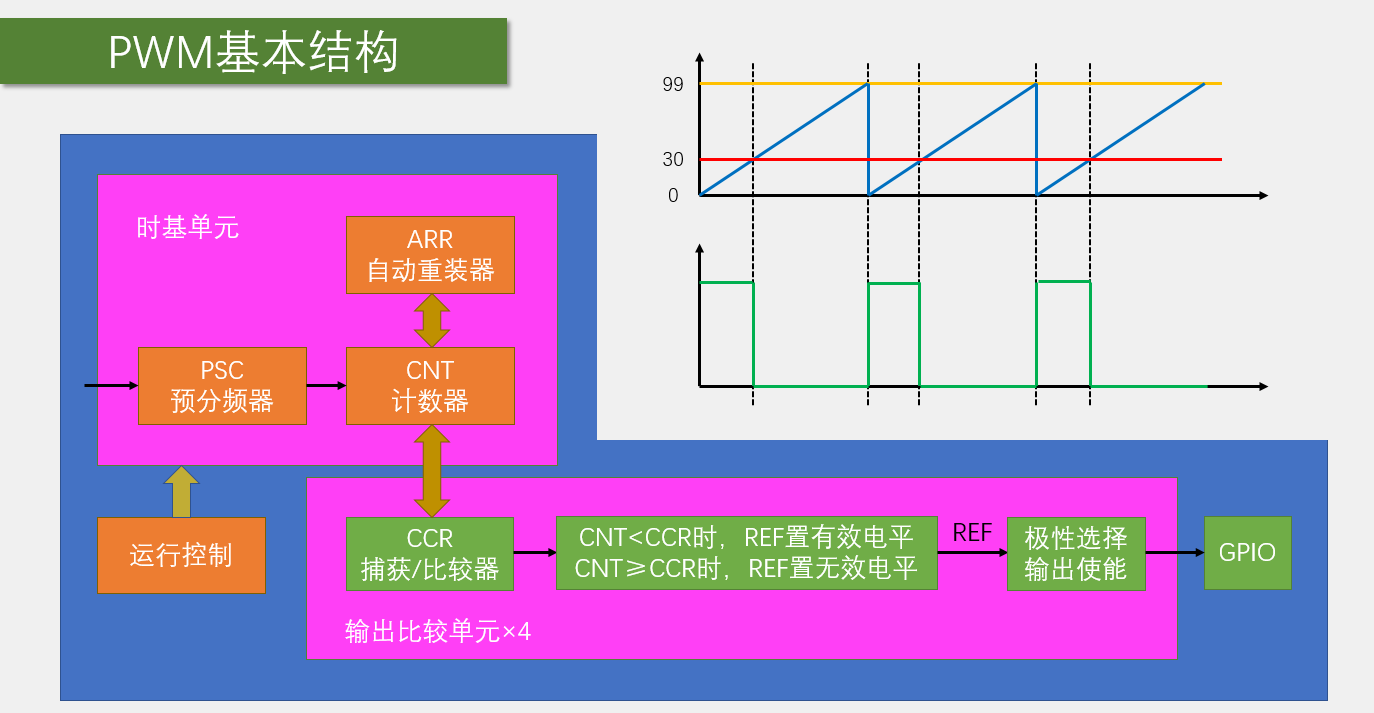

输出pwm波的基本结构:

四路输出比较单元。PWM模式一分析:蓝线ARR,黄线CNT,红线CCR,当CNT<CCR时,REF置高电平,当CNT≥CCR时置低电平。

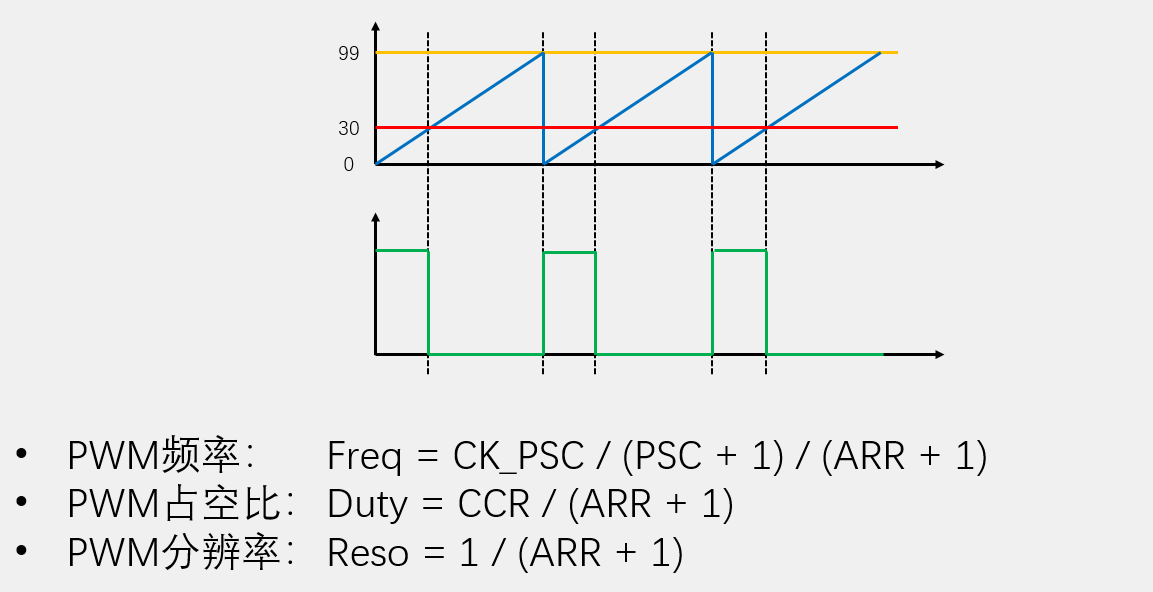

频率,占空比和分辨率的计算:

频率=计数器更新频率,在上图等于30时就已经跳变为低电平,故0~29时为高电平。

占空比=高电平的时间/总的时间,一个计数周期为从零递增到ARR设定值的时间。在纵轴上表示为CCR/(ARR+1).

频率=1/周期,由于自增到ARR后,CNT便重新开始计数,设定时间为0~ARR,故频率为1/(ARR+1)。

4.4捕获

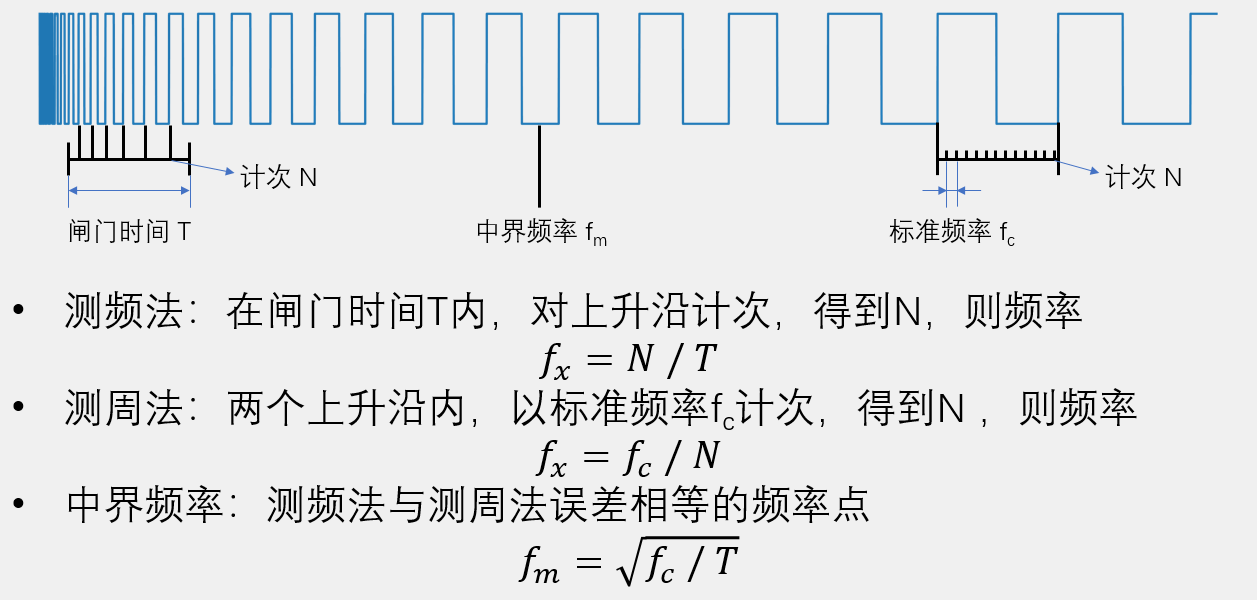

频率测量:

在三个定时器前接霍尔传感器,由于异或门的存在,可以驱动三相电机。

在三个定时器前接霍尔传感器,由于异或门的存在,可以驱动三相电机。

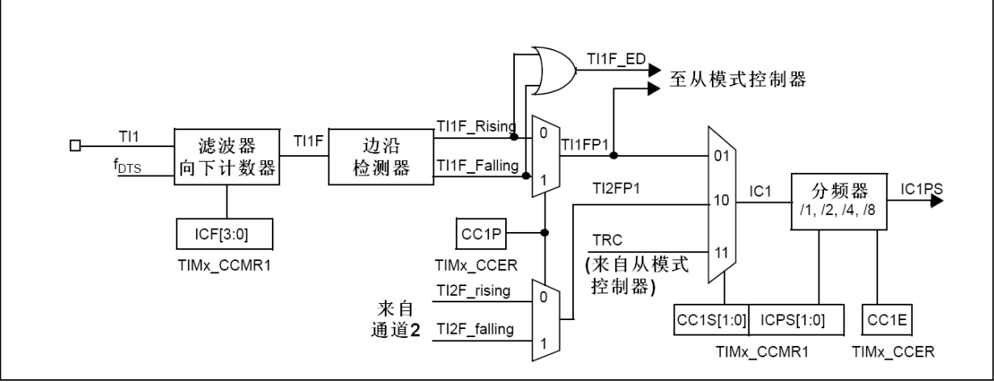

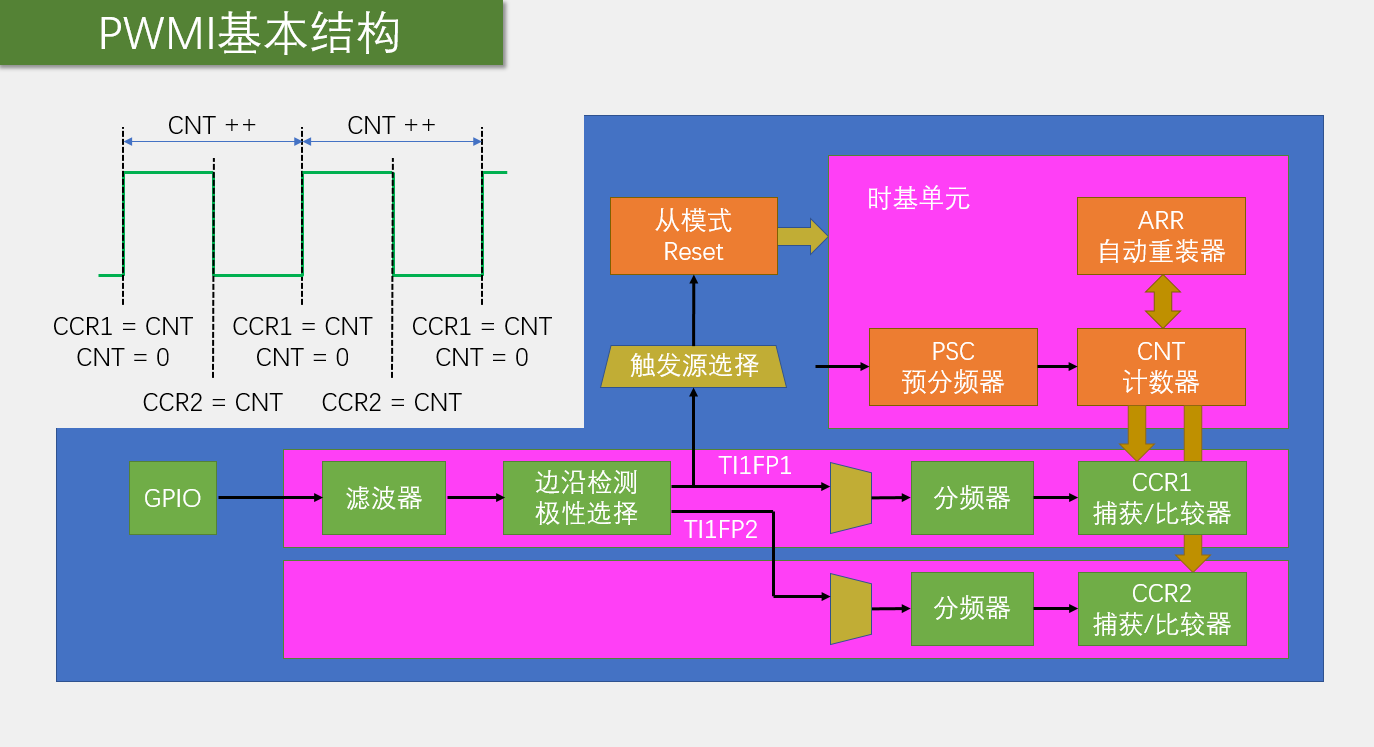

边沿检测器:选择高低电平触发方式。一个引脚可以映射到两个捕获单元,分别对频率和占空比进行捕获。

输入捕获通道一:

ICF位控制滤波器参数:

连续N个都为低电平,输出才为低电平。

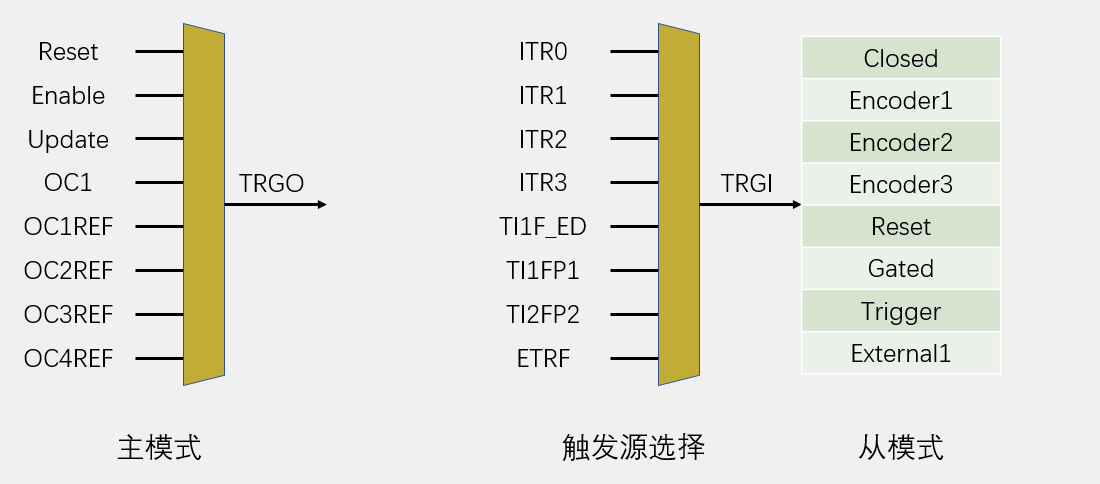

TI1FP1触发CNT自动清零:

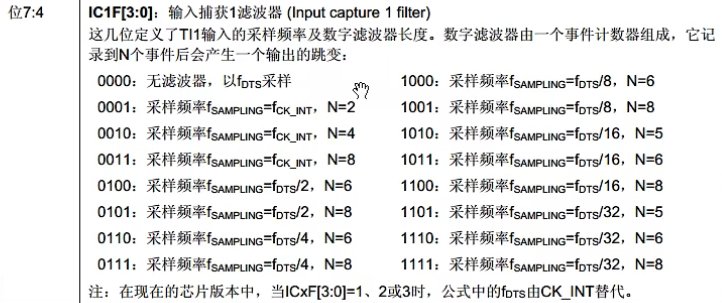

触发源选择进入TRGI,在从模式列表中可选择一项触发。

先转运CNT的值进入CCR,再触发从模式将CNT清零。(CNT上升沿开始自增直到下一个上升沿)

一个通道只能测频率或占空比,不能同时测量。

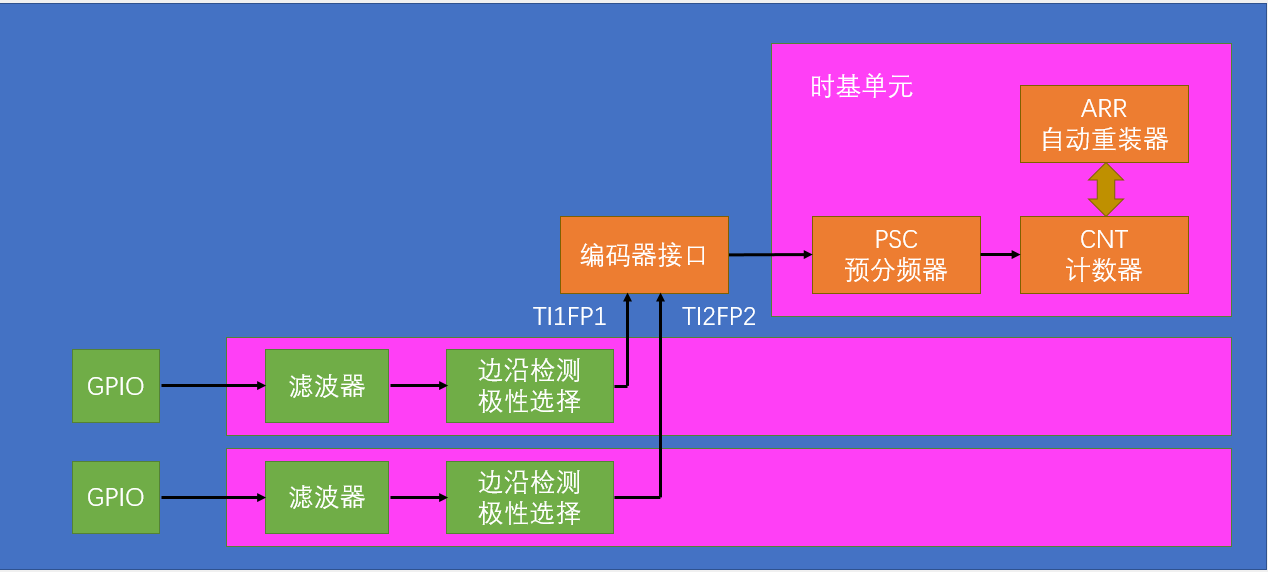

4.5编码器接口

自增自减由编码器接口控制。机性选择选择要不要加一个非门反转。

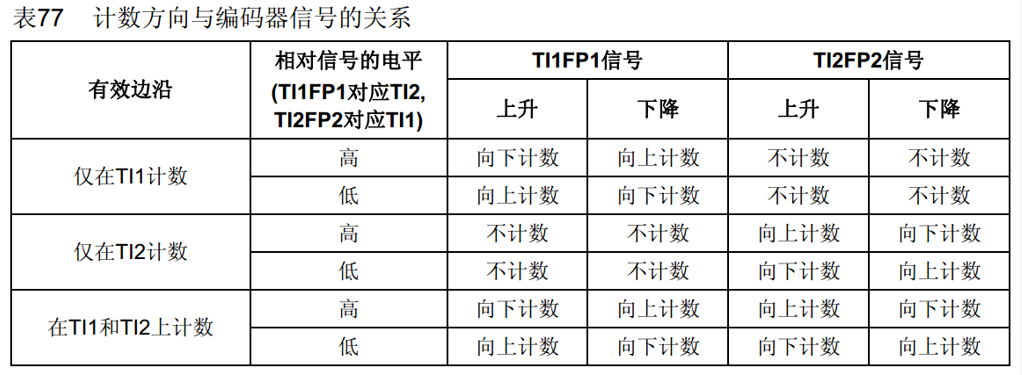

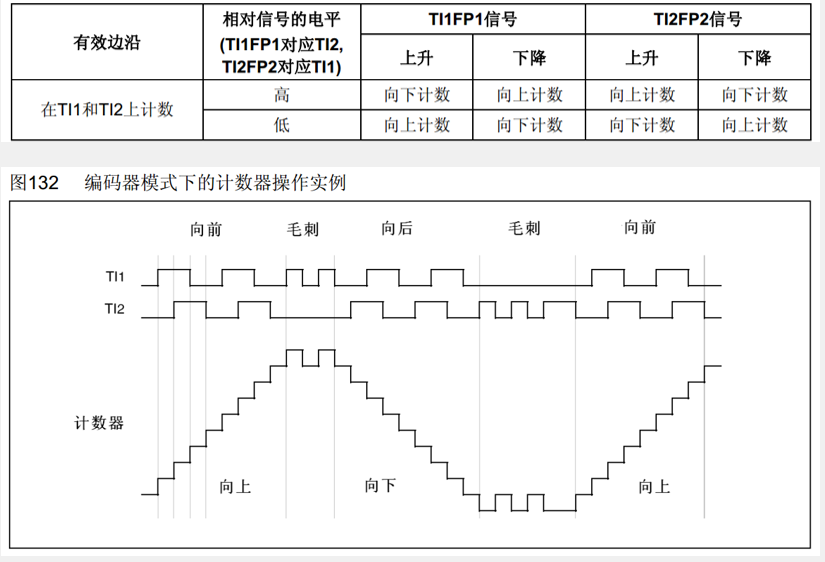

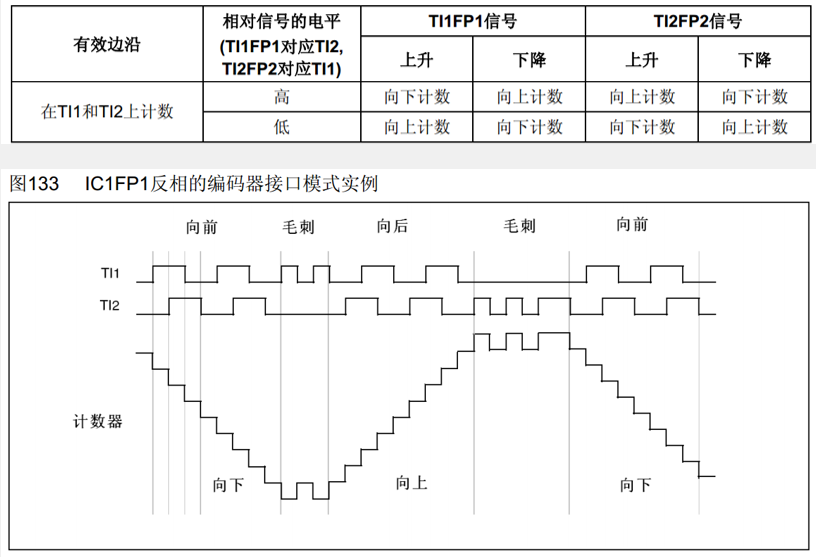

上升沿或下降沿触发计数。依据A,B相的上升沿和高低电平来查表得到计数方式,例:

A↑B相低电平,若在TI1和TI2上都计数,则向上计数。

不反相计数模式如上图。

反相即是在极性选择部分加一个非门,此时TI1的电平应该是翻转的。

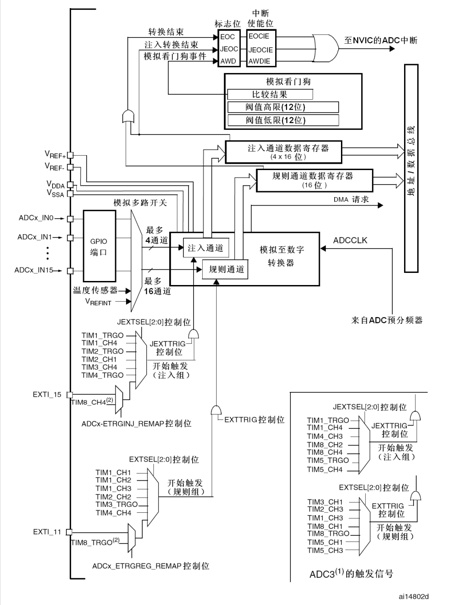

5.ADC和DAC

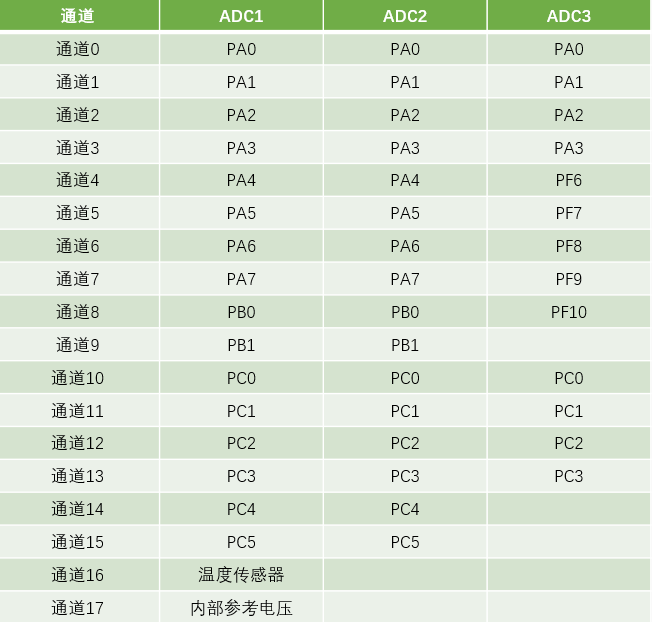

12位_ADC_,stm32f103c8t6_一共_有_三_个ADC,每_个ADC_最多_有_18_个_通道

5.1原理

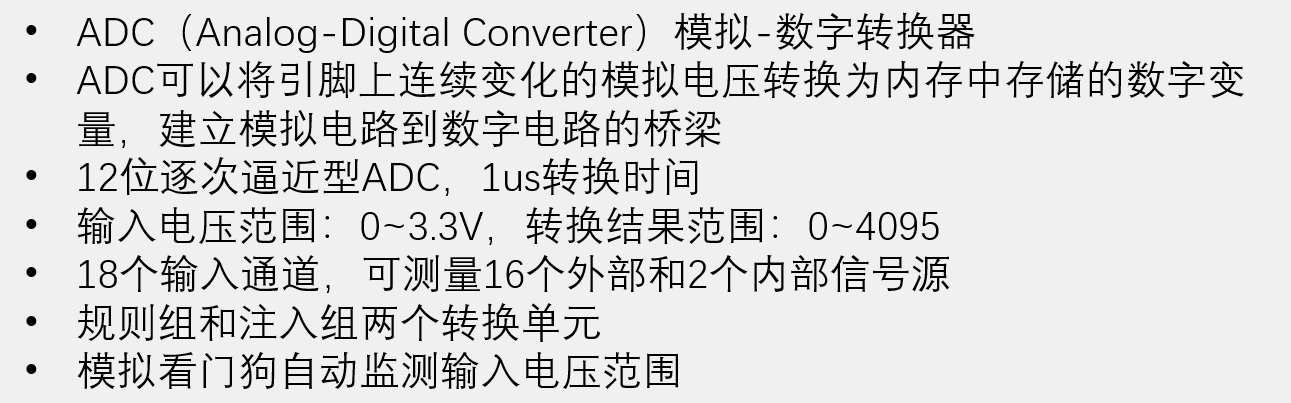

逐次逼近型八位ADC0809芯片:

由通道开关选择的电压值进入到比较器中,DAC转换器可将数字信号转换为模拟的电压值,比较器将通道选择开关进入的电压值和DAC两端的电压用二分法进行对比,直到开关进入的电压和DAC两端的电压值相等,再输出这个比较值。

对于八位ADC,从高位到低位最多循环判断八次就能得到参考电压。

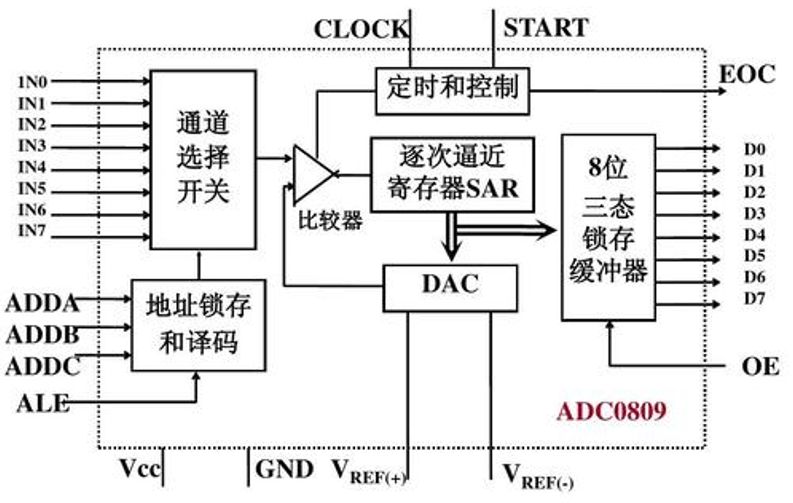

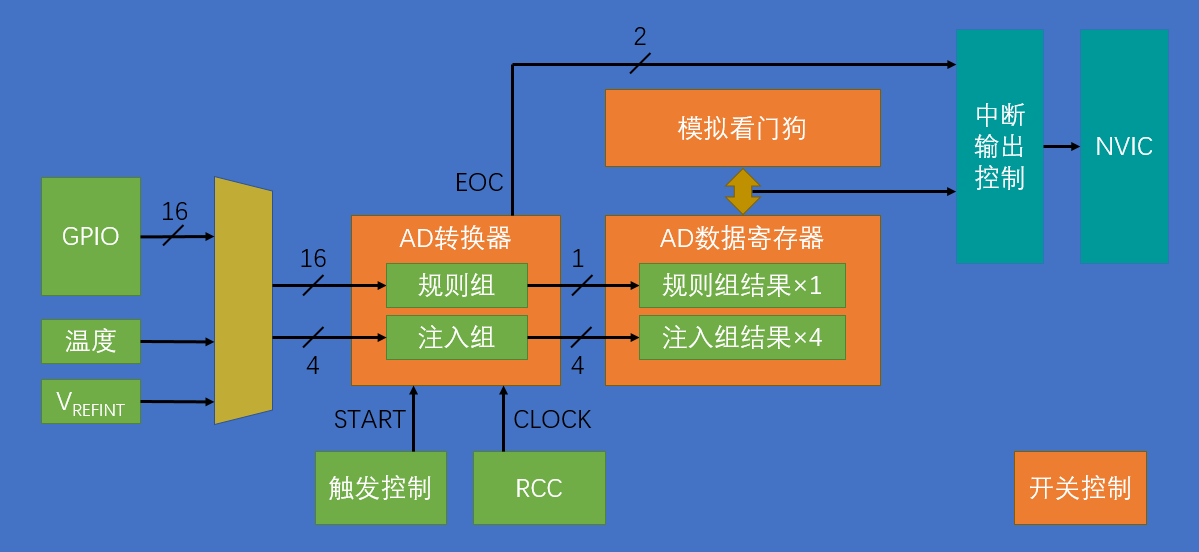

STM32ADC构造:

由定时器TRGO外部硬件触发,端口通过四通道进入和电源电压相比较,注入通道通道多,规则组通道少。规则组转运多数据时需借助DMA。

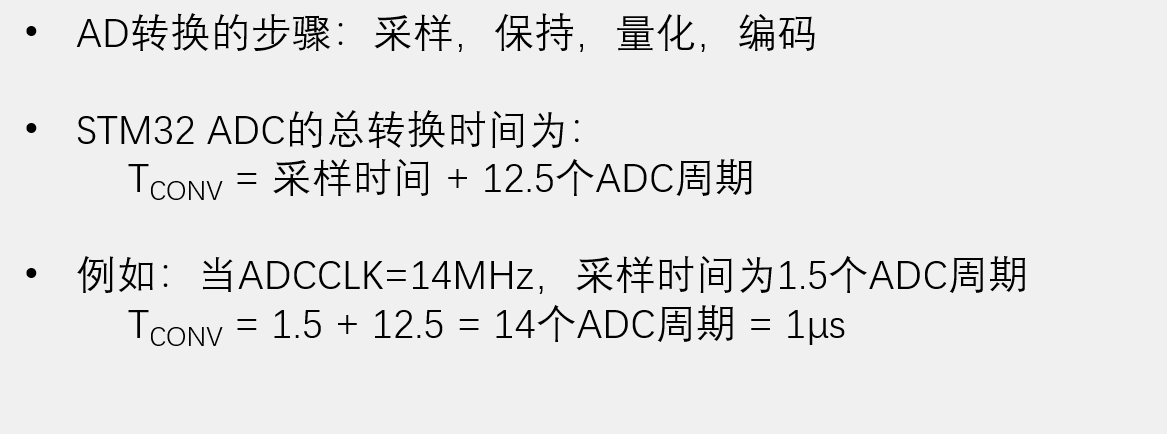

5.2转换过程

当数据溢出超过阈值时,模拟看门狗会向nvic申请中断。

GPIO引脚定义如下:

ADC2和ADC3无温度传感器和内部参考信号。

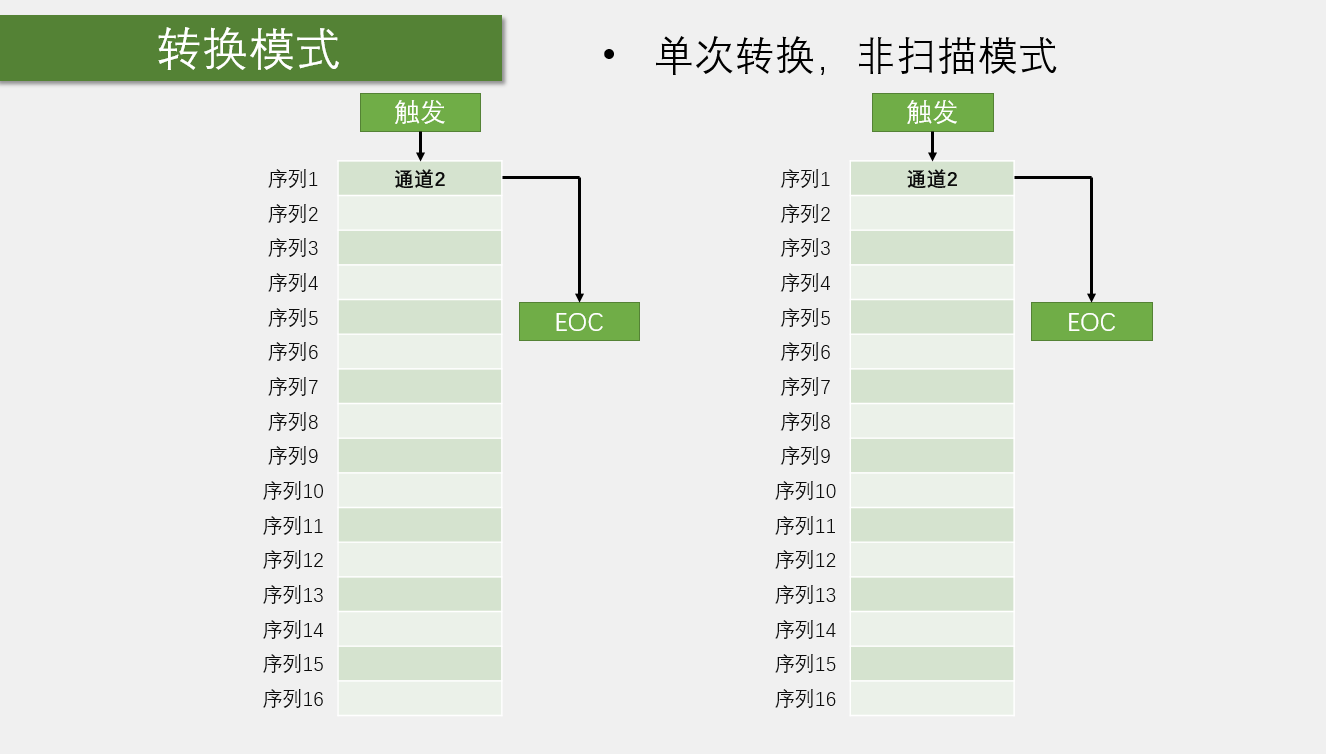

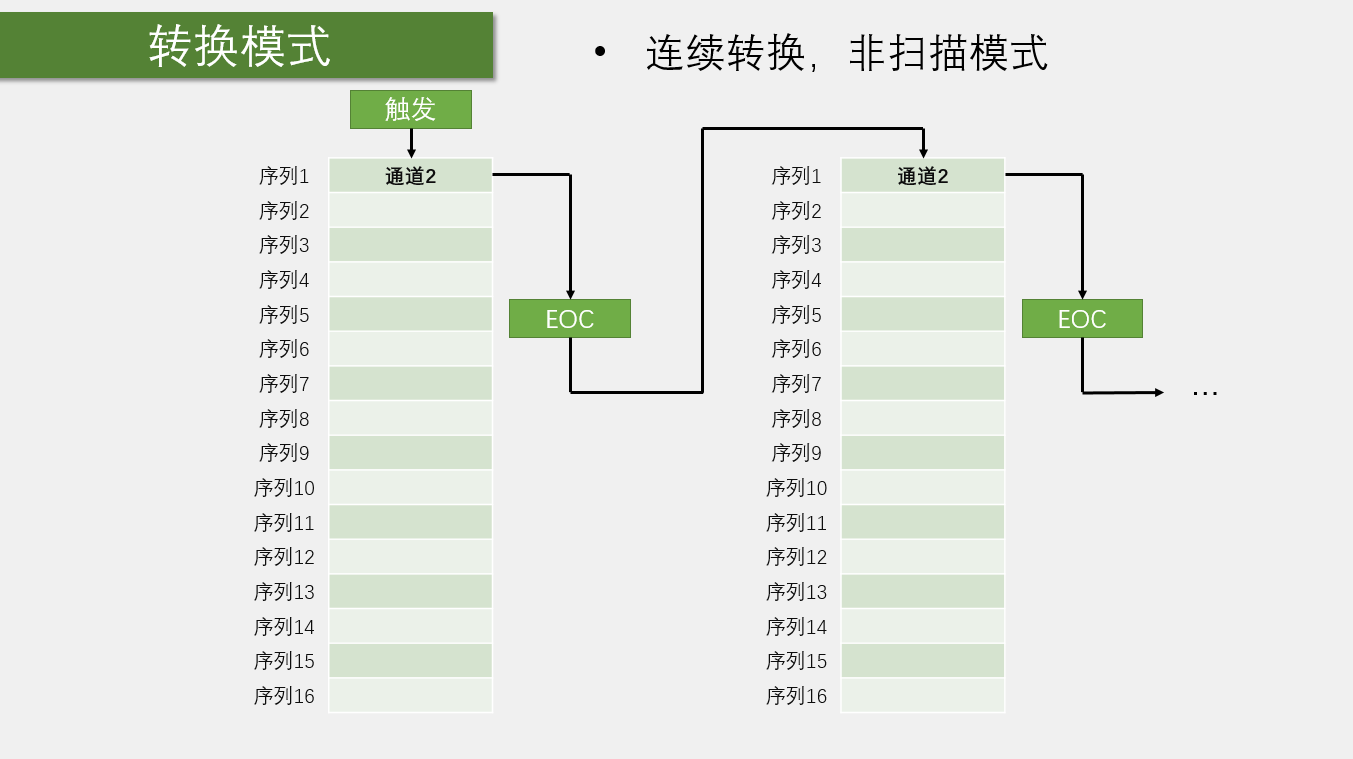

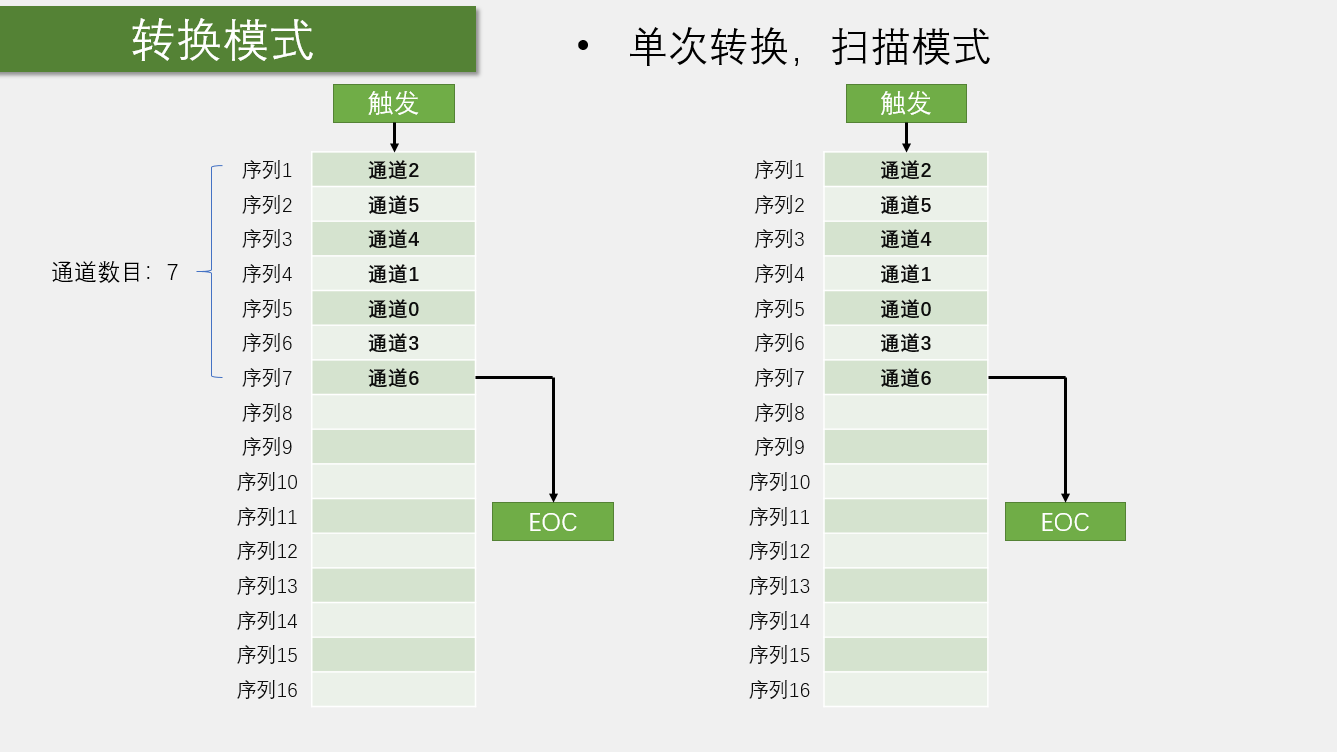

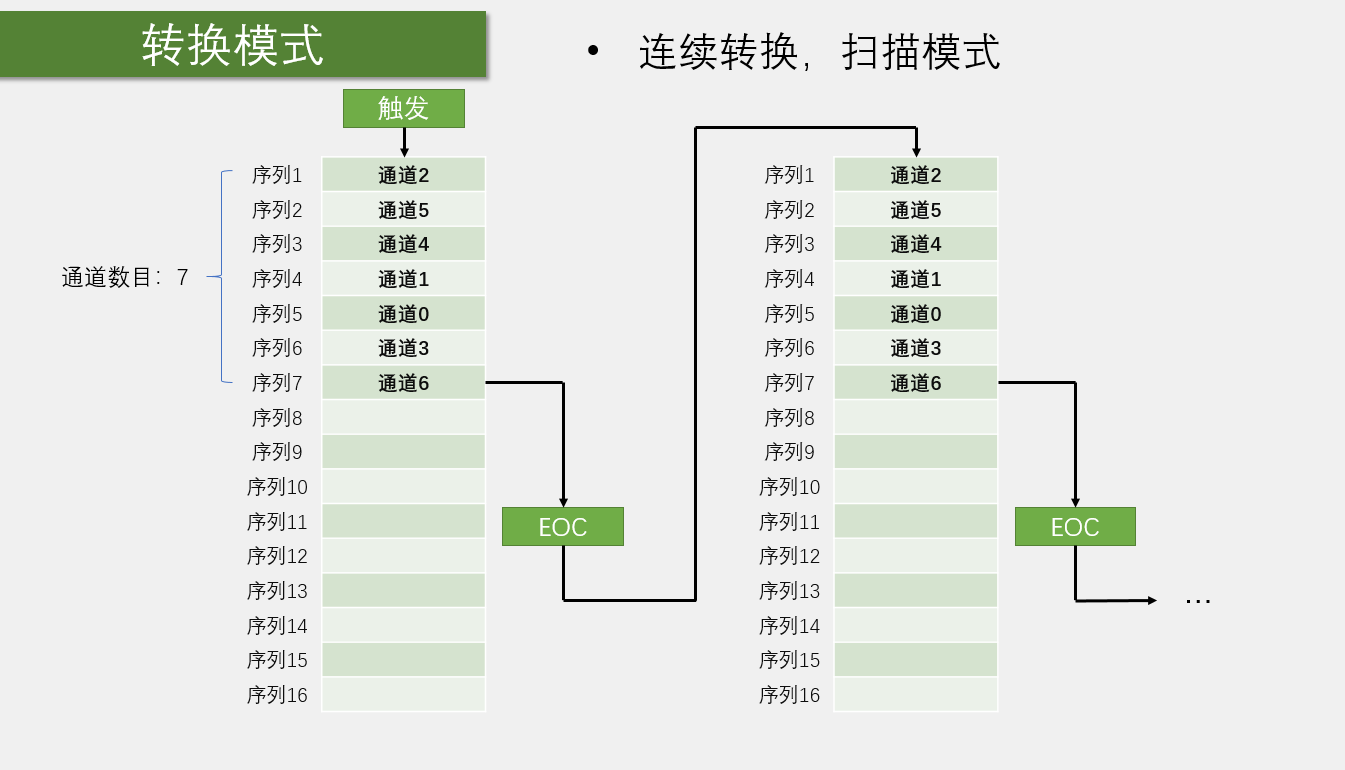

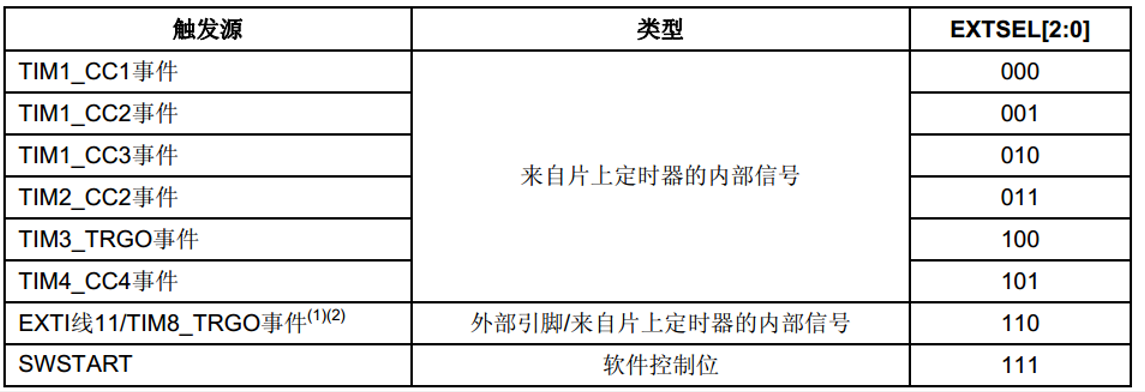

转换模式:

在序列一处选择要进行转换的通道,在转换结果完成的同时给EOC寄存器置1.

菜单列表选择第一个,开始之后不需要停止再手动继续。

寄存器如下:

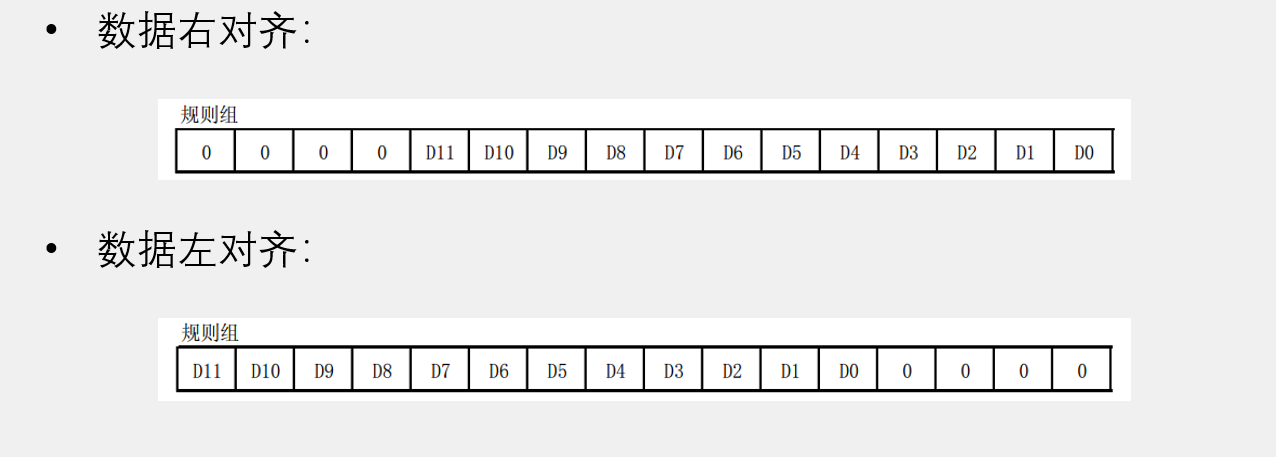

如果不需要这么高分辨率,可以将数据的高八位取出来,即将其左移。

等于说把一个十二位的退化成一个八位的ADC。

6.DMA

7.IIC通讯

7.1物理层

I2C(同步半双工)通讯协议(Inter-Integrated Circuit)是由 Phiilps(飞利浦) 公司开发的,由于它引脚少,硬件实现简单,可扩展性强,不需要 USART、 CAN 等通讯协议的外部收发设备,现在被广泛地使用在系统内多个集成电路(IC)间的通讯。

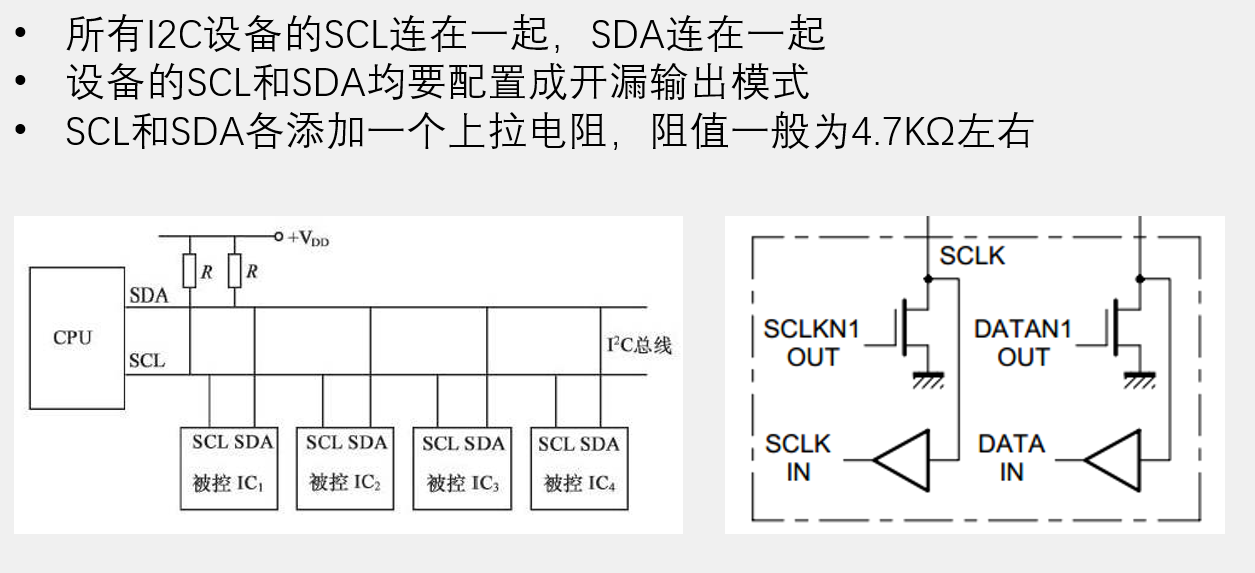

MPU6050固定ID为0x68

为避免被控IC的SDA线和CPU同时输出时电源线短路的问题,统一采用弱上拉电阻配开漏输出的模式。输出低电平时开关MOS导通,处于强下拉的状态,当输出高电平时管脚属于浮空输出的状态,取代了高电平的强上拉输出。为避免这一情况,在VDD接4.7k电阻,处于弱上拉模式。

一个 I2C 总线只使用两条总线线路,一条双向串行数据线(SDA) ,一条串行时钟线(SCL)。数据线即用来表示数据,时钟线用于数据收发同步。

7.2协议层

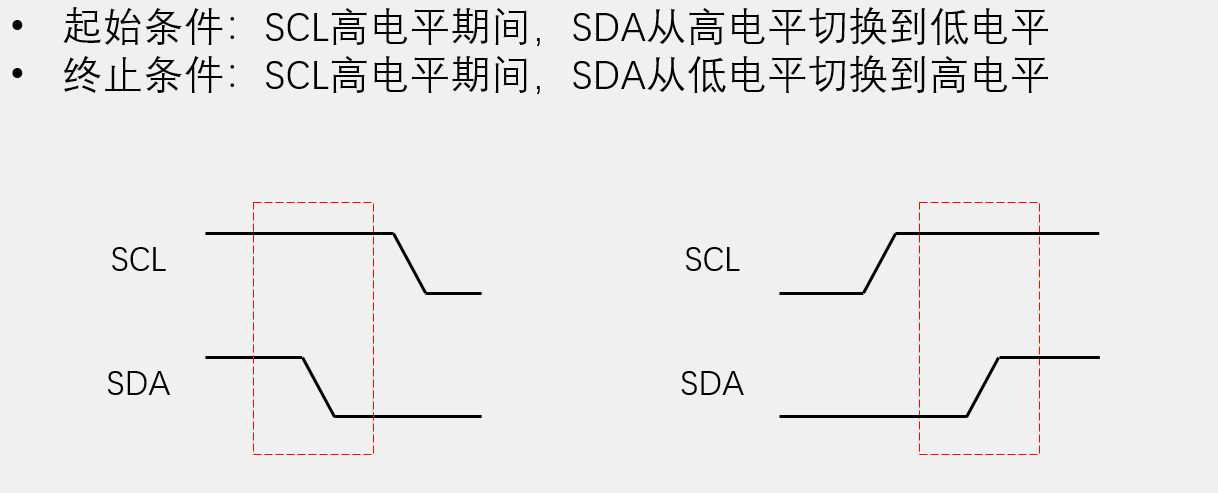

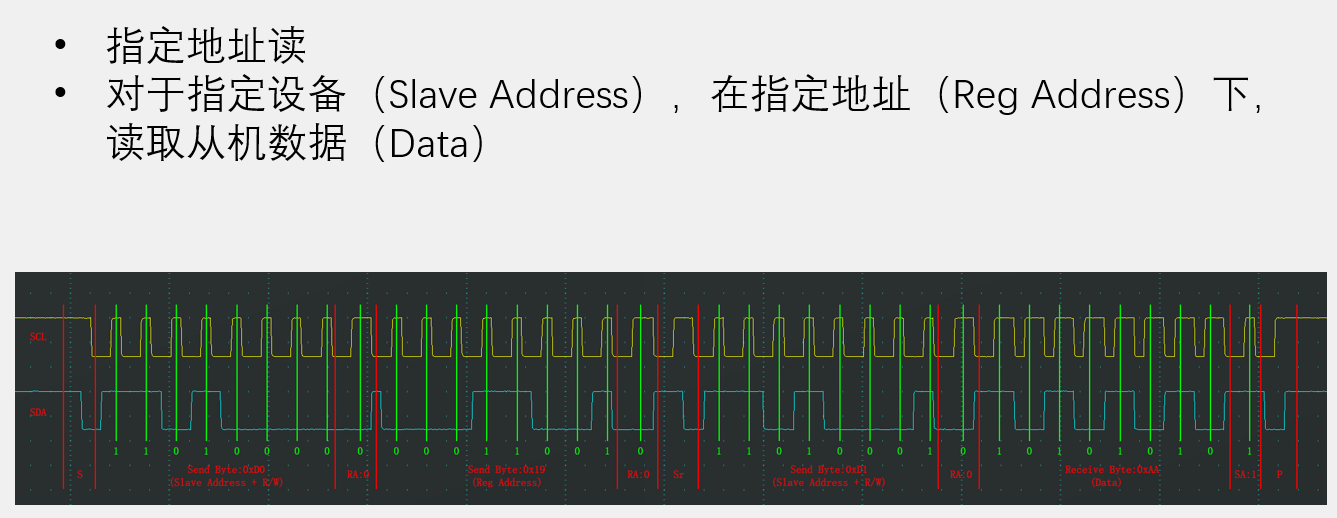

上图是IIC通讯的基本时序单元。从机捕获到SCL高电平,SDA下降沿时,处于复位状态,等待主机召唤。终止条件时SCL和SDA均处于高电平状态。(释放SDA就是拉高SDA)

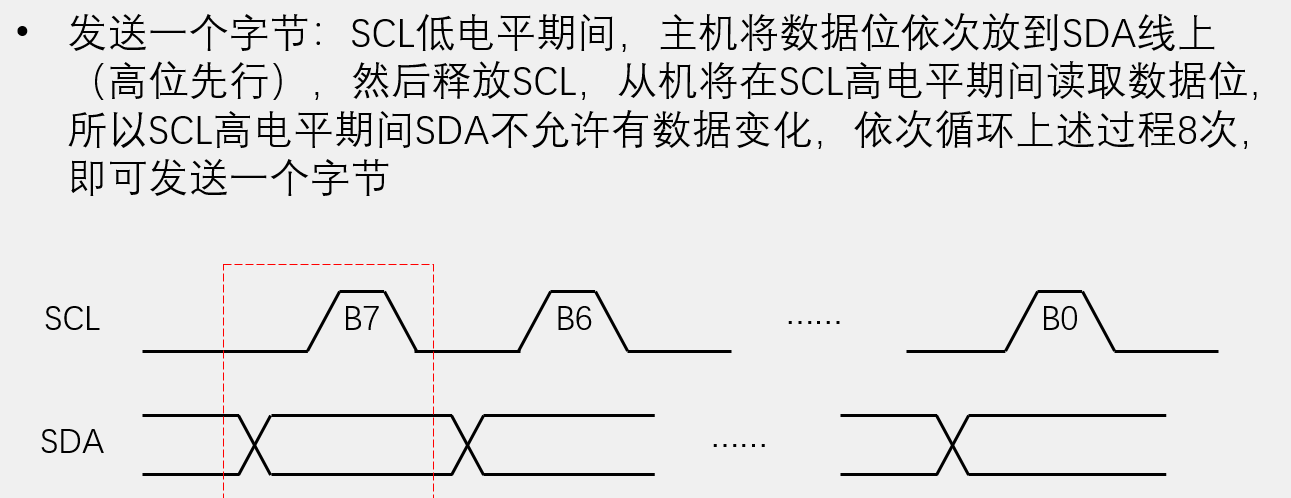

高八位发送。

I2C 的数据和地址传输都带响应。响应包括“应答(ACK)”和“非应答(NACK)”两种信号。作为数据接收端时,当设备(无论主从机)接收到 I2C 传输的一个字节数据或地址后,若希望对方继续发送数据,则需要向对方发送“应答(ACK)”信号,发送方会继续发送下一个数据;若接收端希望结束数据传输,则向对方发送“非应答(NACK)”信号,发送方接收到该信号后会产生一个停止信号,结束信号传输。

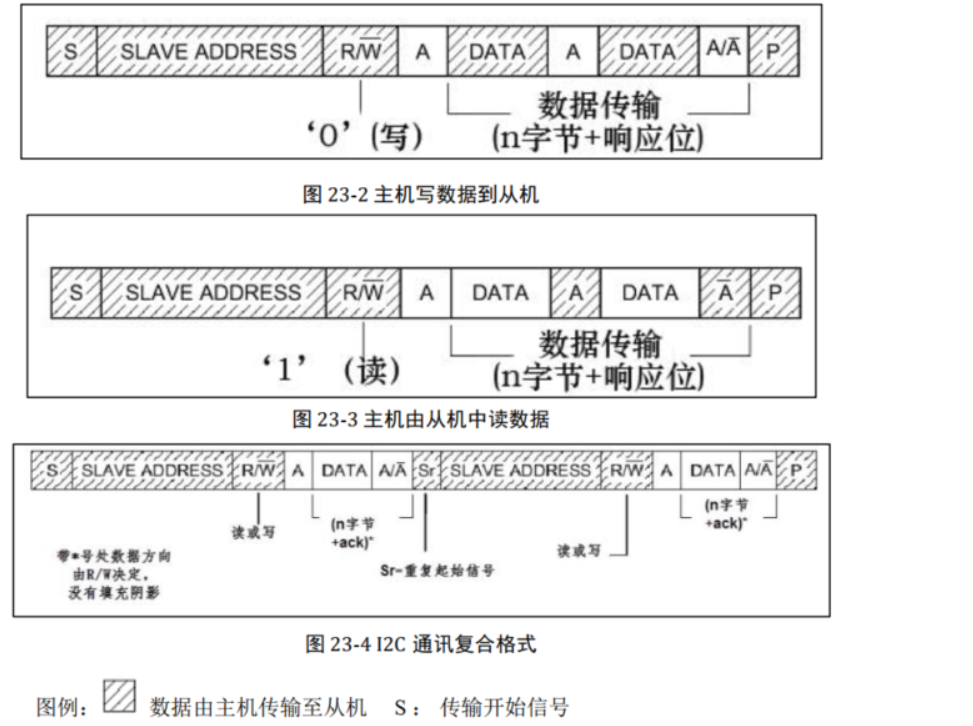

读写顺序,一般是7位地址和10位地址。

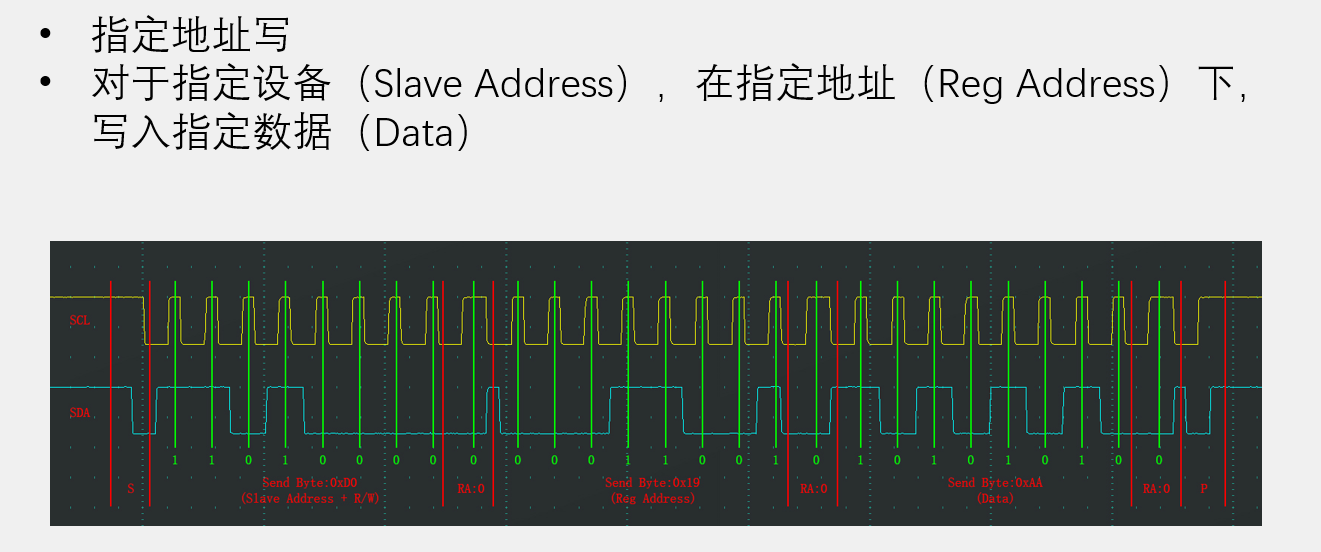

从机地址+读写位,确定哪台设备写入还是读出。send byte:操作地址寄存器。后续是从机应答。

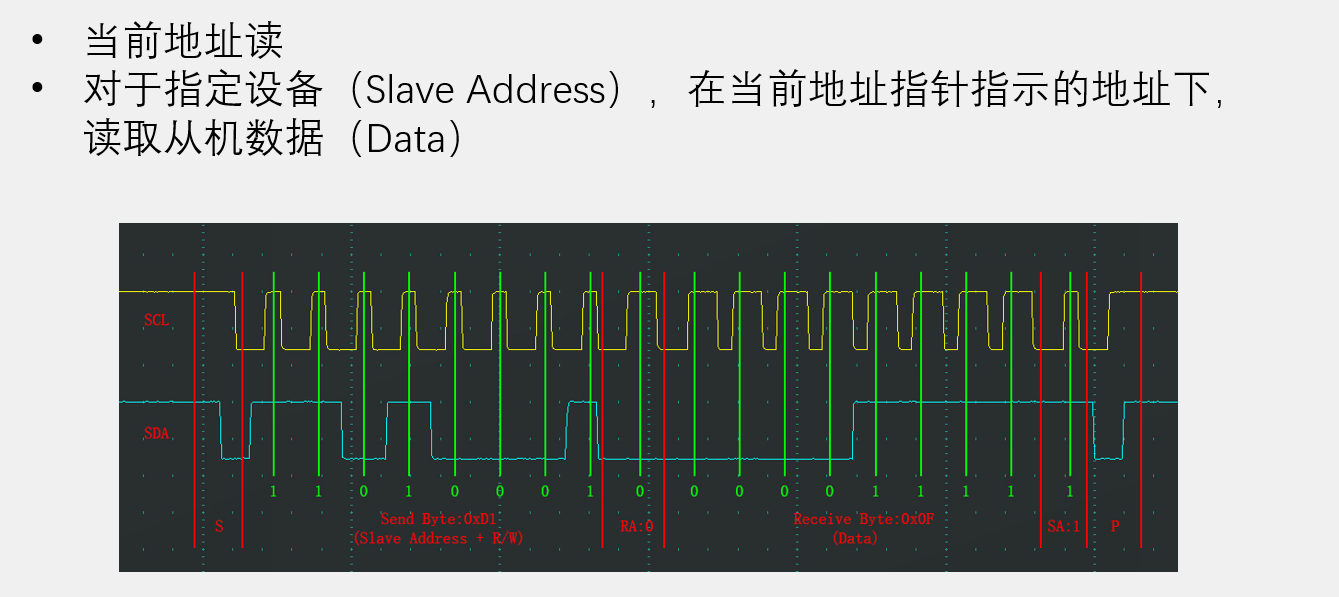

要切换读写方向,只能重置起始位。

7.3MPU6050

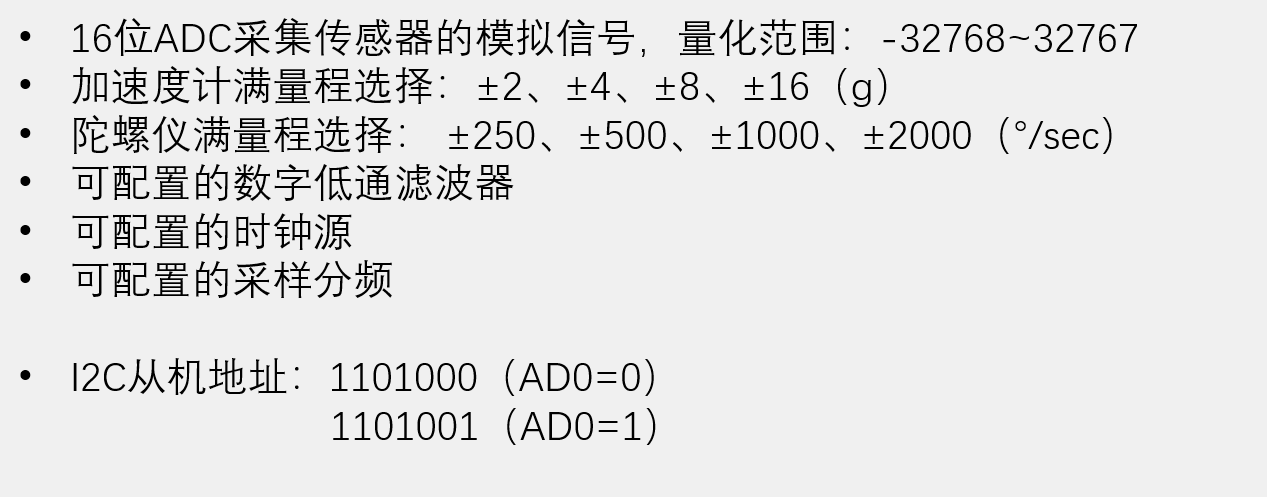

7.3.1基本数据

加速度计测量加速度,陀螺仪测量角度。

所有寄存器商店都默认00,除107默认0x40,117默认0x68(ID号0x68),电源管理寄存器1,默认睡眠模式。

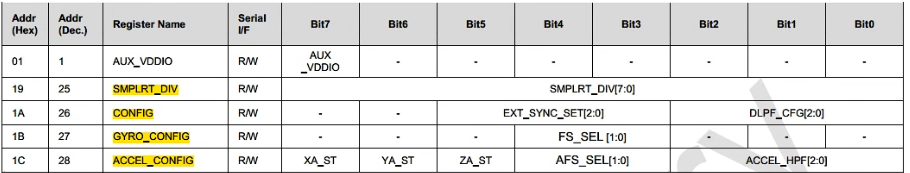

7.3.2寄存器

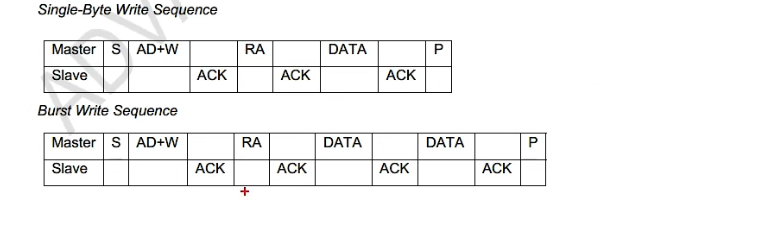

IIC通讯格式:

开始+地址+写+应答+重置+应答+数据段+应答。写同理

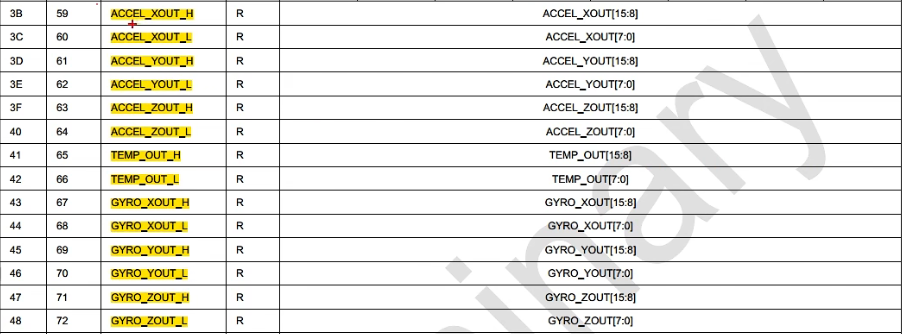

第一列和第二列均为寄存器地址,第一列十六进制,第二列十进制。rw代表可读可写,r代表只读。

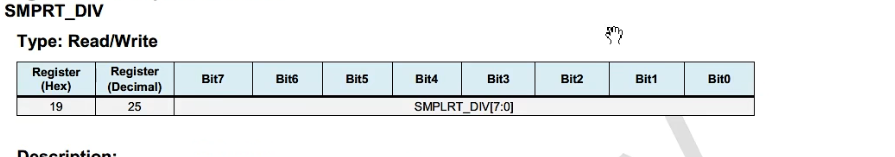

7.3.2.1SMPLRT_DIV:采样分频寄存器

时钟为内部晶振,外部晶振,外部引脚的方波。本文档以陀螺仪晶振为例。不使用外部晶振为8KHz,使用为1kHz

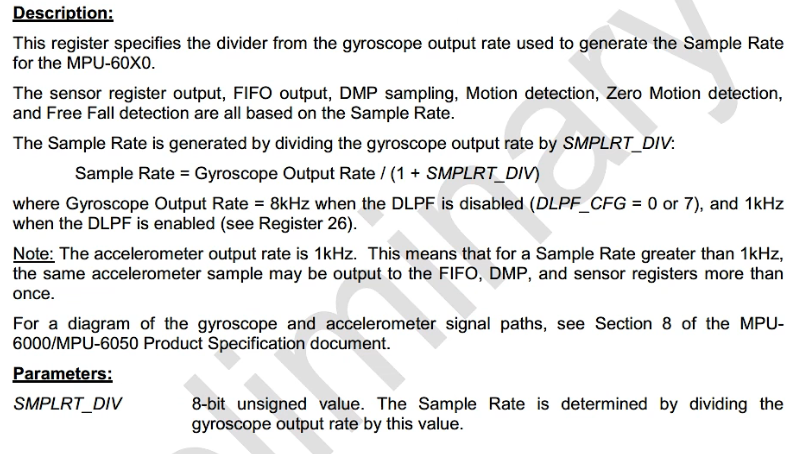

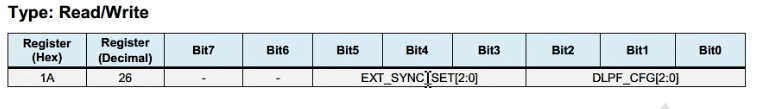

7.3.2.2CONFIG:配置寄存器

外部同步设置和低通滤波器设置,主要考虑低通滤a波器设置部分。

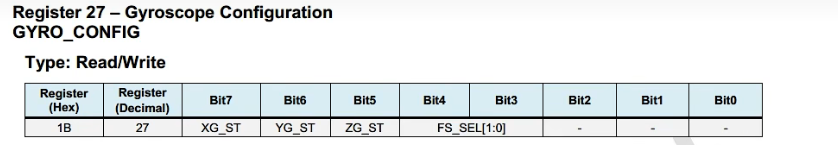

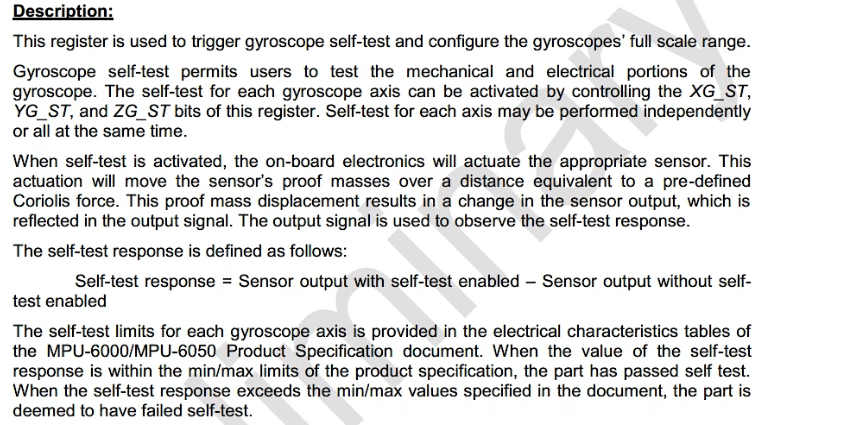

7.3.2.3GYRO_CONFIG:陀螺仪配置寄存器

高三位为陀螺仪的XYZ轴的使能位。中间是满量程选择位。

自测响应=自测使能数据-自测失能数据

下面是自测响应表,上电时,先使能自测数据,再失能自测读取数据,二者相减得到自测响应。

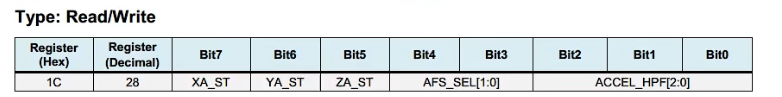

7.3.2.4ACCEL_CONFIG:加速度计配置寄存器

前两位基本相同,后两位为配置高通滤波器。

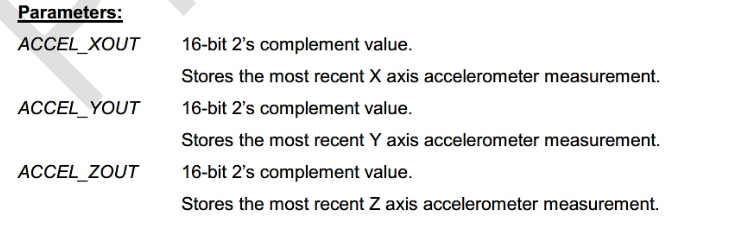

数据寄存器,包括加速度计寄存器,温度计寄存器,陀螺仪寄存器。

其余数据均是一样的操作方法,以一个十六位无符号整型的补码变量存在。

7.4IIC软件读写MPU6050

7.4.1操作时序

IIC通讯共六个时序:

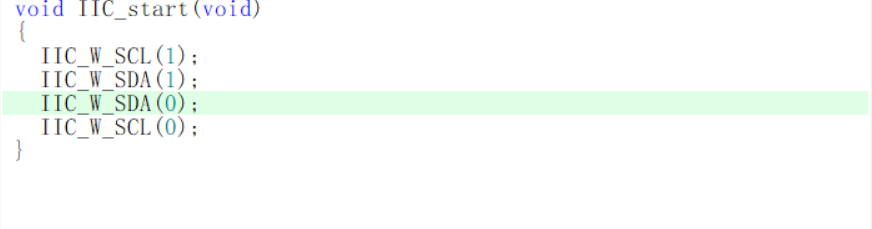

起始:

按照通讯时序的要求,在开始时先把SCL和SDA都拉高。但是在结束的时候,以SCL时钟线为参考,SDA数据并不总是低电平,为重新启动发送时操作成功,需手动把SDA线先拉低到低电平,再操作SCL线。

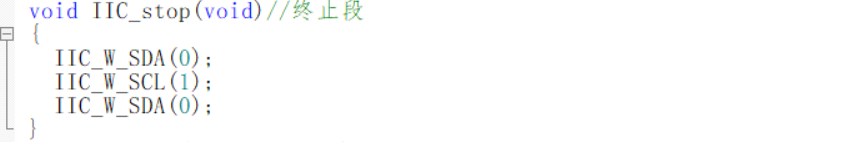

终止:

终止时以时钟线为参考,SDA不总是低电平,需先将SDA拉低,再将其拉高完成终止操作。

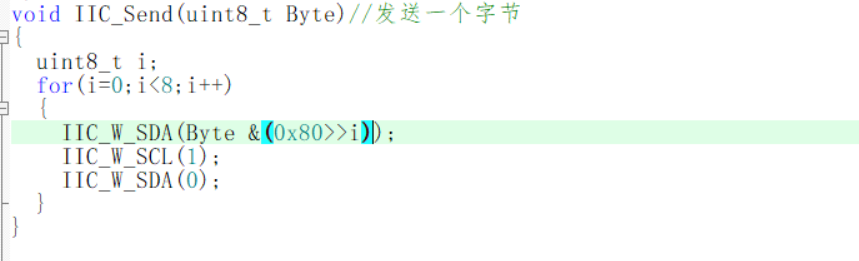

发送八字节数据:

按高八位的顺序持续写入数据,直到八个字节的时钟走完。移位运算加括号保证优先级。

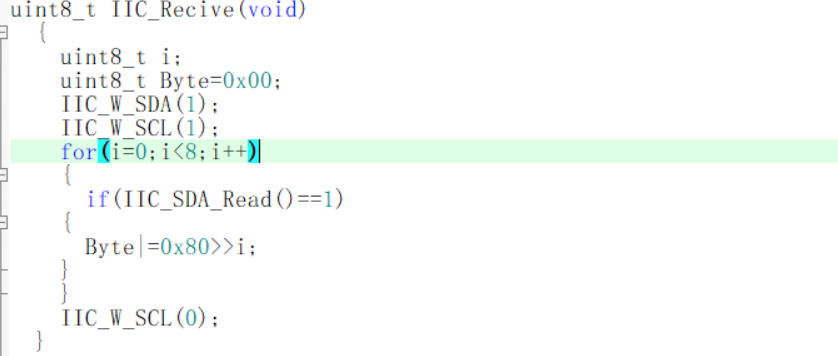

接收八字节数据

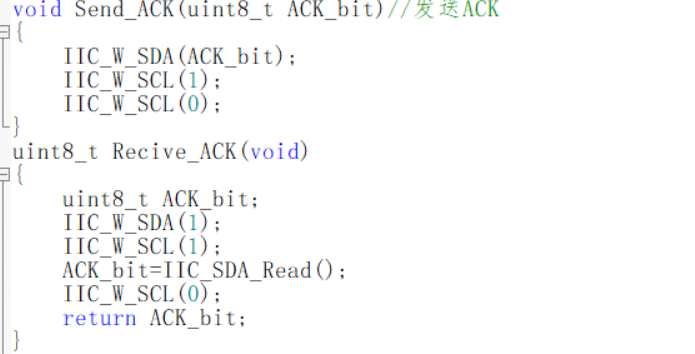

发送接收ACK:

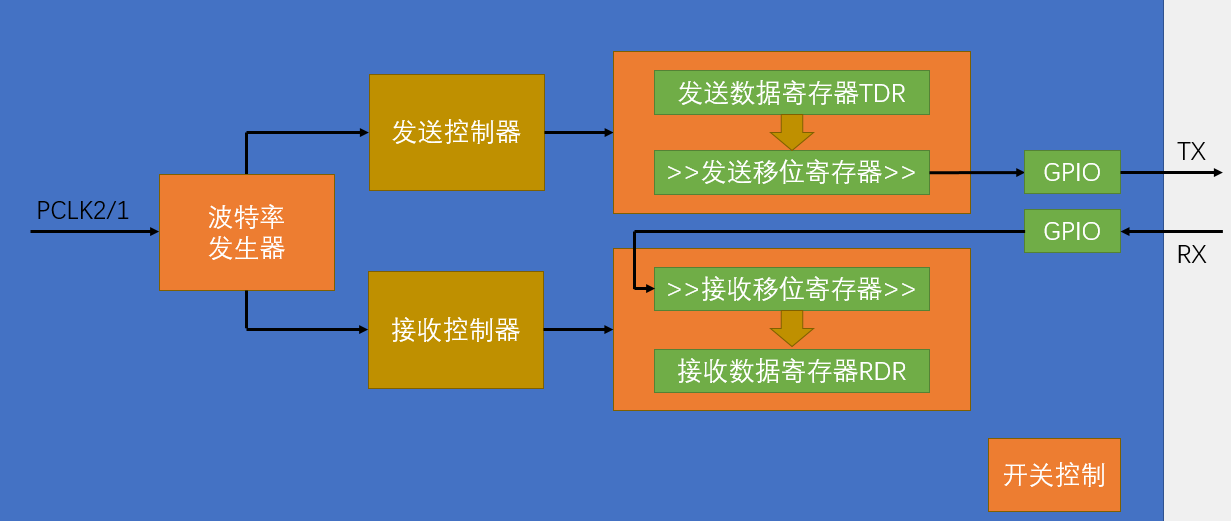

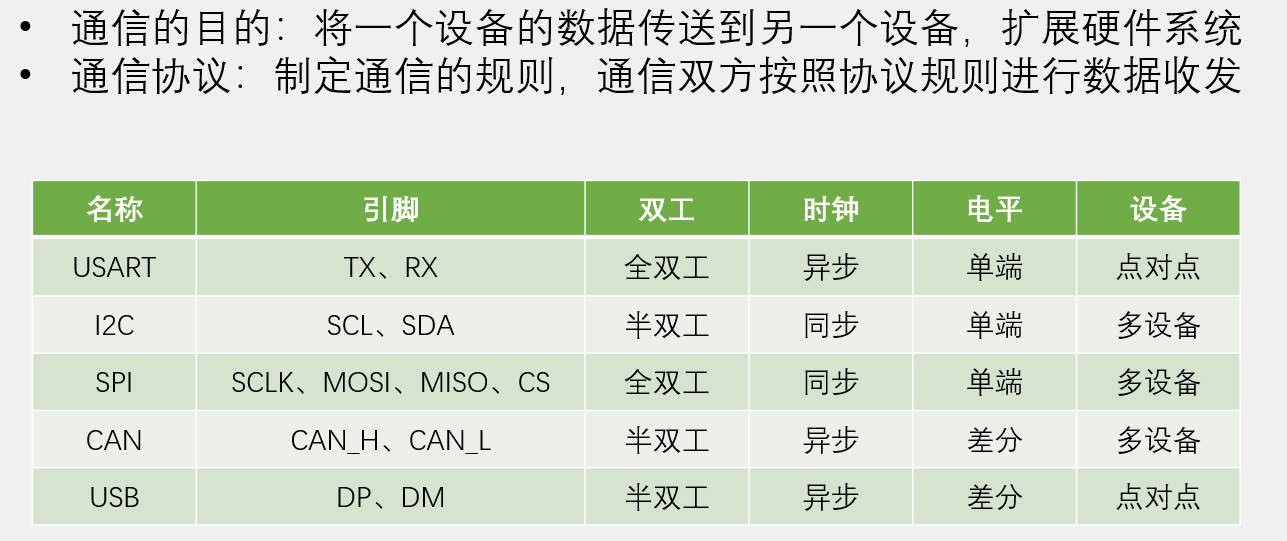

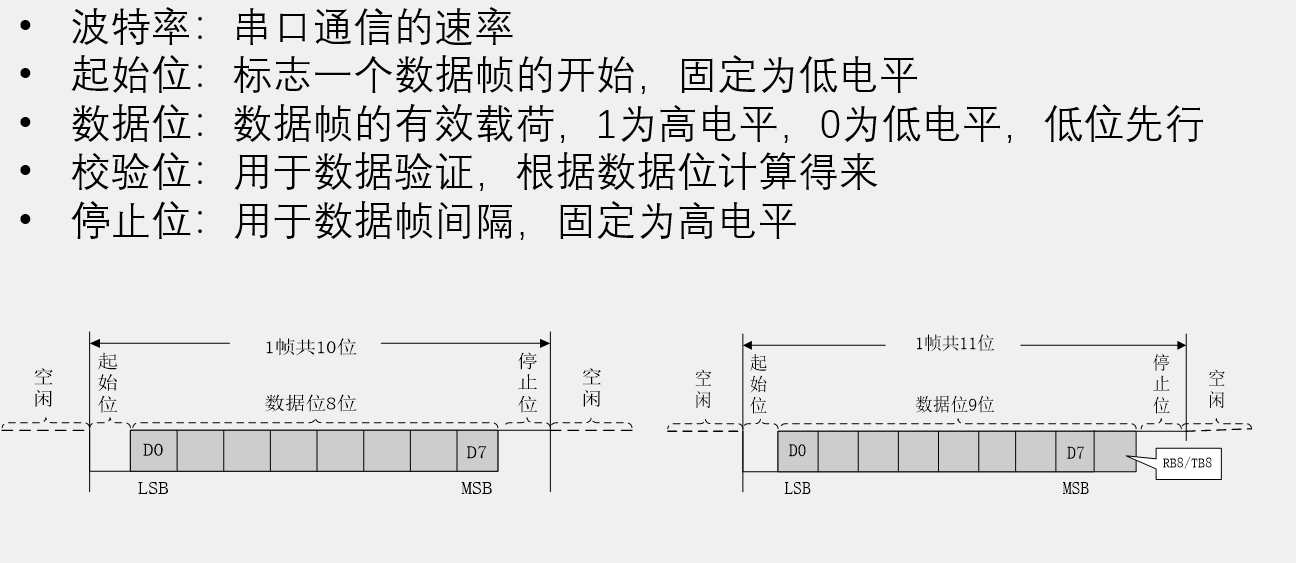

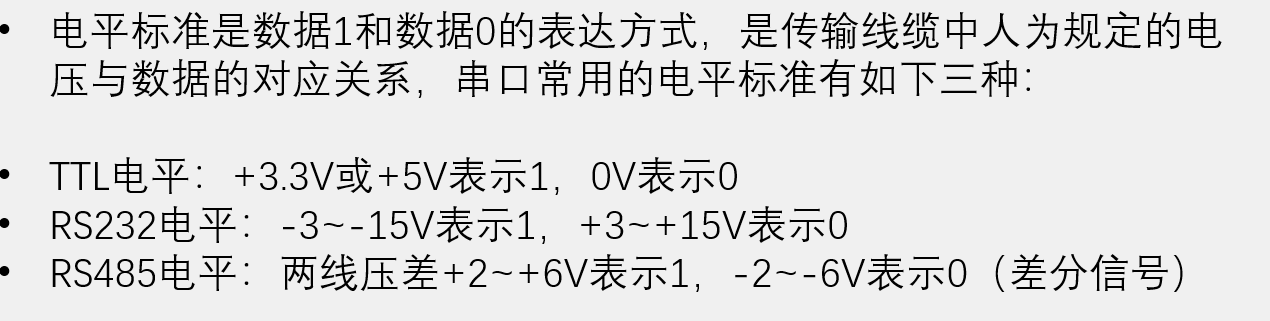

8.USART

8.1USART详解:

双方按照约定的协议进行通讯,一根数据线是半双工,两根数据线全双工。

单端电平单端信号需要共地。

•USART(Universal Synchronous/Asynchronous Receiver/Transmitter)通用同步/异步收发器

•USART是STM32内部集成的硬件外设,可根据数据寄存器的一个字节数据自动生成数据帧时序,从TX引脚发送出去,也可自动接收RX引脚的数据帧时序,拼接为一个字节数据,存放在数据寄存器里

•自带波特率发生器,最高达4.5Mbits/s

•可配置数据位长度(8/9)、停止位长度(0.5/1/1.5/2)

•可选校验位(无校验/奇校验/偶校验)

•支持同步模式、硬件流控制、DMA、智能卡、IrDA、LIN

•STM32F103C8T6USART资源: USART1、 USART2、 USART3

他们都属于串口。因为是异步通讯,故他们的波特率在约定上应当相同。

串口起始是高电平,发送起始位是低电平,发送完之后必须要有停止位。

8.2基本结构和程序: