- 1Shell 实现Docker MySQL5.7安装及SQL脚本运行_docker 安装mysql5.7 并执行脚本 csdn

- 2opencv人脸打马赛克

- 3鸿蒙OS开发问题:【尺寸适配算法】_鸿蒙os开发尺寸适配

- 4传感器驱动系列之HX711称重模块

- 52023年度AI技术盘点:突飞猛进的技术进展与未来挑战_人工智能最新技术发展成果

- 6数据结构九:线性表之链式队列的设计

- 7【后端】Redis命令行批量删除指定前缀key_err wrong number of arguments for 'del' command

- 8java调试技巧_分享5个实用的vs调试技巧

- 9npm install 你很明白吗

- 10SMSBoom:强大的短信自动化工具,让信息管理更高效

Vivado_除法器 IP核 使用详解_vivado除法器ip核

赞

踩

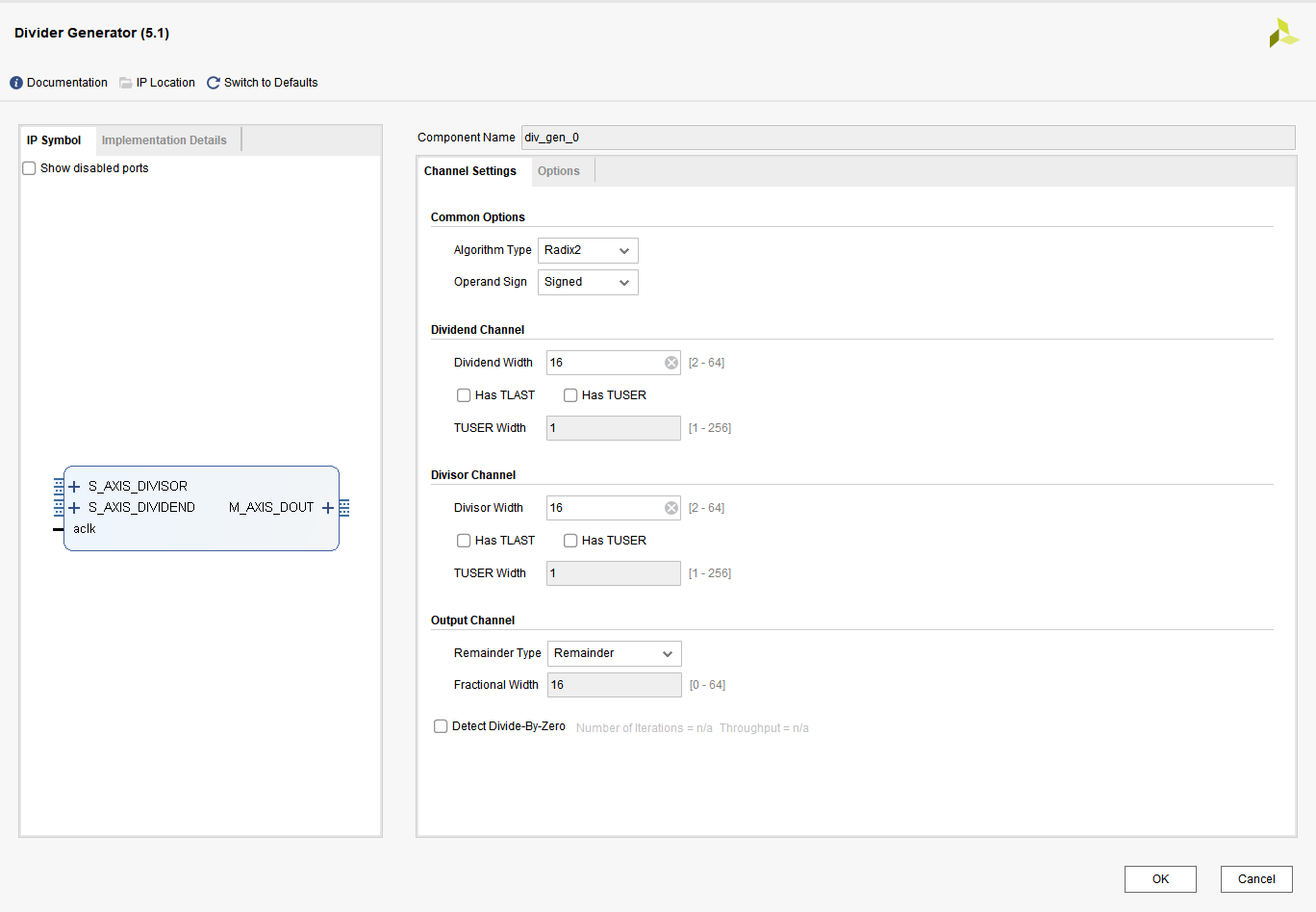

本文介绍使用Vivado中除法器Divider Generator(5.1)的使用方法。

参考资料:pg151

Divider Generator

Channel Settings选项卡

#Common Options:

Algorithm Type:

一共有三种类型,分别是High Radix、LutMult、Radix2。用户可根据除数和被除数数位宽大小和延迟需求选择不同算法类型。

Opeand sign:

在High Radix类型下,仅支持Signed;在LutMult类型下,支持Unsigned和Signed;在Radix2类型下,支持Unsigned和Signed。

#Divivend Channel

Dividend Width: 设置被除数位宽,在不同算法类型下,支持的最大位宽不同。在High Radix类型和Radix2类型下,最大支持64位宽;在LutMult类型下,最大支持17位宽。

TLAST和TUSER端口,IP核不使用此端口信息,但会以与数据路径相同的延迟传输到输出通道。用户可以设置TUSER端口宽度。

#Divisor Channel

Divisor Width: 设置除数位宽,在不同算法类型下,支持的最大位宽不同。在High Radix类型和Radix2类型下,最大支持64位宽;在LutMult类型下,最大支持11位宽。

TLAST和TUSER端口,IP核不使用此端口信息,但会以与数据路径相同的延迟传输到输出通道。用户可以设置TUSER端口宽度。

#Output Channel

Remainder Type:设置余数类型。

设置为Remainder时,商和余数被认为是分开的,因此在连接成m_axis_dout_tdata信号之前是面向字节的。

设置为Fractional时,小数部分被认为是商的扩展,因此这两个字段在填充到下一个字节边界之前被连接起来。

如果勾选Detect Divide_By_Zero,则会多出一个m_axis_dout_tuser端口,以便在执行除0操作时发出信号。

注意:

商(Quotient)的位宽等于被除数(Dividend)的位宽。

整数余数(Remainder)的位宽度等于除数(Divisor )的宽度。

对于Fractional类型输出,余数位宽与被除数和被除数无关。

使用AXI4接口的输入输出端口在对应的数据字段都会拓展对齐到字节边界。

Options选项卡

Clocks Per Division: 确定Radix-2解决方案的吞吐量(输入(或输出)之间的时钟间隔)。此参数的值越低,吞吐量越高,但资源使用量也越大。

#AXI4-Stream Options

Flow Control: Blocking or NonBlocking。

具体区别参考Blocking阻塞模式与NonBlocking非阻塞模式

#Latency Configuration:

Latency Configuration: 支持手动或自动配置延迟。

Latency: 手动指定从输入到输出的延迟。

在不同算法类型下,不同配置有不同的延迟,具体可在PG151手册中查看。

仿真测试

module div_sim; reg aclk; reg s_axis_divisor_tvalid; reg s_axis_dividend_tvalid; reg [15:0] s_axis_divisor_tdata; reg [15:0] s_axis_dividend_tdata; wire m_axis_dout_tvalid; wire [31:0] m_axis_dout_tdata; wire [15:0] quotient; wire [15:0] remainder; assign quotient = m_axis_dout_tdata[31:16]; assign remainder = m_axis_dout_tdata[15:0]; initial begin aclk = 1'b1; forever #10 aclk = ~aclk; end initial begin s_axis_dividend_tdata = 16'd0; s_axis_dividend_tvalid = 1'b0; s_axis_divisor_tvalid = 16'd0; s_axis_divisor_tdata = 1'b0; # 40; s_axis_dividend_tdata = 16'd12345; s_axis_dividend_tvalid = 1'b1; s_axis_divisor_tdata = 16'd100; s_axis_divisor_tvalid = 1'b1; # 60; s_axis_dividend_tdata = -16'd12345; s_axis_dividend_tvalid = 1'b1; s_axis_divisor_tdata = 16'd100; s_axis_divisor_tvalid = 1'b1; # 60; s_axis_dividend_tdata = 16'd12345; s_axis_dividend_tvalid = 1'b1; s_axis_divisor_tdata = -16'd100; s_axis_divisor_tvalid = 1'b1; # 60; s_axis_dividend_tdata = -16'd12345; s_axis_dividend_tvalid = 1'b1; s_axis_divisor_tdata = -16'd100; s_axis_divisor_tvalid = 1'b1; end div_gen_0 inst0 ( .aclk(aclk), // input wire aclk .s_axis_divisor_tvalid(s_axis_divisor_tvalid), // input wire s_axis_divisor_tvalid .s_axis_divisor_tdata(s_axis_divisor_tdata), // input wire [15 : 0] s_axis_divisor_tdata .s_axis_dividend_tvalid(s_axis_dividend_tvalid), // input wire s_axis_dividend_tvalid .s_axis_dividend_tdata(s_axis_dividend_tdata), // input wire [15 : 0] s_axis_dividend_tdata .m_axis_dout_tvalid(m_axis_dout_tvalid), // output wire m_axis_dout_tvalid .m_axis_dout_tdata(m_axis_dout_tdata) // output wire [31 : 0] m_axis_dout_tdata ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

设置算法类型为Radix-2,设置除数和被除数为16位有符号数,输出设置为Remainder类型,延迟手动设置为10。

则输出dout[31:16]为商(Quotient),dout[15:0]为余数(Remainder)。

仿真图结果显示,输入tvalid到输出dout_tvalid的时间差为200ns,即延迟为10。

12345

÷

100

=

123

⋯

45

−

12345

÷

100

=

(

−

123

)

⋯

(

−

45

)

12345

÷

(

−

100

)

=

(

−

123

)

⋯

45

−

12345

÷

(

−

100

)

=

123

⋯

(

−

45

)

输出设置为Fractional类型,设置为Fractional Width为16时,仿真结果和前一次相同。

为了体现两种输出模式的区别,设置为Fractional Width为12。

设置fractional的数据格式为实数,11位小数。

小数余数结果为0.4497、-0.4497、0.4497。