热门标签

热门文章

- 1基于n-gram模型的中文分词_ngram分词

- 2java连接mysql增删改查(01单增删改查)_java连接mysq 增删改查

- 3论文aigc检测率为多少合格?论文ai免费润色_本科毕业论文aigc值多少合格

- 4Python中数据可视化的最新趋势和未来发展

- 5不相交集(The Disjoint Set ADT)_the array representation of a disjoint set contain

- 6Solana 与 DePIN 的双向奔赴,会带来 DePIN 之夏吗?

- 7matlab实现apriori算法源代码实验报告_apriori算法实验报告

- 8计算机毕业设计hadoop+spark知识图谱视频推荐系统 视频分析可视化大屏 视频爬虫 视频大数据分析 大数据毕业设计 机器学习 深度学习 人工智能

- 9对云原生整体解决方案的进一步复盘

- 10Java进阶-SpringCloud设计模式-工厂模式的设计与详解

当前位置: article > 正文

ZYNQ入门——《Zynq-Design-using-Vivado》(3)_vivado怎么添加两个 axi bram 控制器

作者:笔触狂放9 | 2024-05-03 20:27:50

赞

踩

vivado怎么添加两个 axi bram 控制器

目录

2.1 使用Create and Package IP Wizard创建自定义IP:

《lab3》

1.实验目标

通过完成本实验,您将能够:

- 使用Vivado的IP Packager功能创建自定义外设。

- 修改IP的功能。

- 将自定义外设添加到设计中。

- 添加引脚约束。

- 在系统中添加块RAM。

2.实验步骤

2.1 使用Create and Package IP Wizard创建自定义IP:

- 打开Vivado。

- 创建新的IP位置。

- 运行Create and Package IP Wizard。

- 填写IP的详细信息。

- 创建与LED相关的接口。

- 修改生成的HDL代码。

- 运行综合,检查设计是否正确。

2.2 打包IP:

- 点击Package IP选项卡。

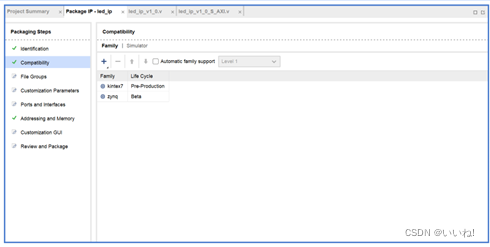

- 配置IP的分类和兼容性。

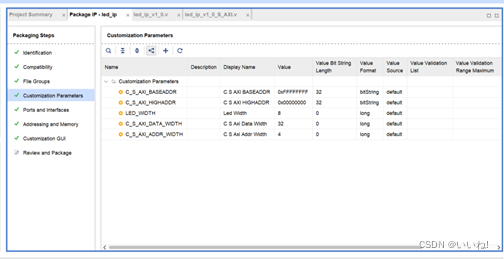

- 合并文件组和定制参数的更改。

2.3 修改项目设置:

- 打开Vivado项目。

- 保存项目为新的工程。

- 配置IP库的位置。

2.4 添加自定义IP、BRAM和约束:

- 在Block Design中添加自定义IP。

- 自定义IP的参数设置和连接。

- 添加LED的外部引脚。

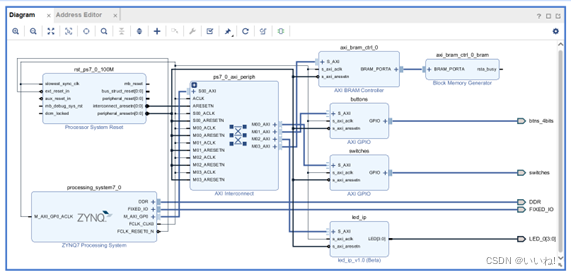

- 添加AXI BRAM控制器和Block Memory Generator。

- 添加引脚约束。

- 验证设计,重新生成设计。

3.问题及解决方法

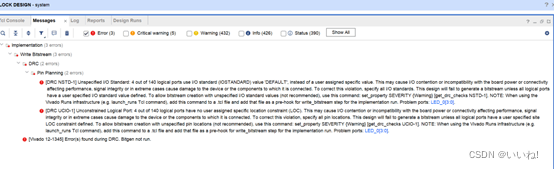

第一次生成比特流时失败了,通过询问发现是led对应的输出名称和xdc中的名称不一致导致的:

图3-1

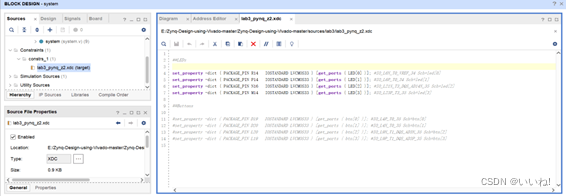

图3-2

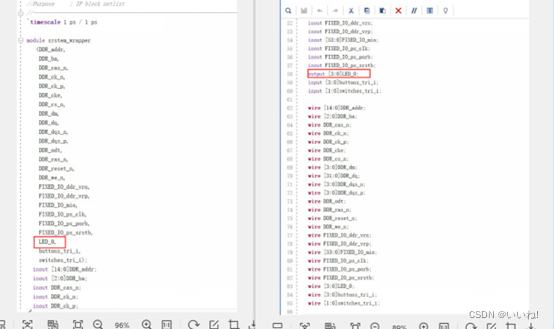

图3-3

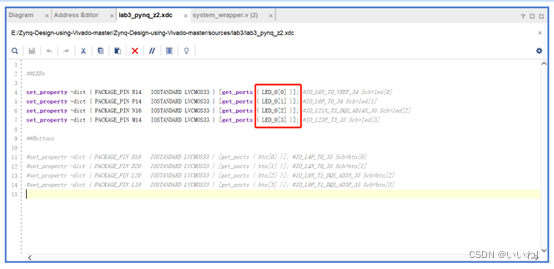

修改成这样后就可以了:

图3-4

4.调试

4.1 调试截

打包IP核:

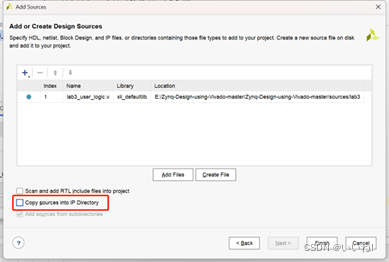

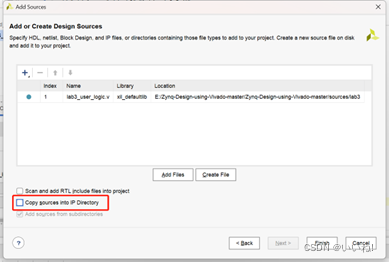

图4.1-1

图4.1-2

图4.1-3

图4.1-4

完成块设计:

图4.1-5

5.总结

通过这个实验,可以学会了如何使用Vivado的IP Packager功能来创建自定义外设,并将其集成到我的设计中。这是一个非常有用的技能,对于嵌入式系统开发和FPGA设计来说至关重要。

在实验中,还可以学会如何创建自定义IP核,如何修改IP核的功能以满足我的需求,以及如何添加引脚约束和块RAM到我的设计中。这些步骤在实际项目中非常有用,因为它们允许我根据项目的要求定制外设,并确保设计的正确性和性能。

我还学到了一个重要的调试教训,即确保IP核的输出名称与xdc文件中的名称一致。这是一个容易被忽略的问题,但它可以导致生成比特流失败。通过检查和调整这些名称,我成功地解决了问题,实现了成功的生成比特流。

这个实验对我的技能和知识有所帮助,我感到非常满意。我期待将这些新学到的技能应用到未来的项目中。再次感谢这个实验提供的机会!

6.附录

附录.1参考资料

[1] https://github.com/xupgit/Zynq-Design-using-Vivado/tree/master

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/笔触狂放9/article/detail/531385

推荐阅读

相关标签