- 1分享四款导航页 个人主页html源码

- 2高教社杯数模竞赛特辑论文篇-2023年C题:商超蔬菜销售数据的统计分析及建模(附获奖论文及R语言和LINGO代码实现)(续)_2023年全国大学生统计建模大赛题目

- 3NLP算法-情绪分析-snowNLP算法库_snownlp是算法吗

- 4hyperledger fabric 实战开发——水产品溯源交易平台(二)_fabric web平台开发

- 5香橙派 AIpro开发板开箱测评(代码开源)

- 6基于拉勾网数据的爬取与分析_拉勾数据研究院是抓取哪里的数据

- 7mac安装暴雪战网卡在45%的解决方法_mac战网安装程序卡在45%

- 8SQLite数据库中JSON 函数和运算符(二十七)_sqlite json

- 9如何利用开源的大模型框架进行实际项目开发_利用开源模型构件大模型

- 10ESP32驱动-MAX98357-I2S数字功放驱动

Vivado中的五种仿真模式比较_vivado 综合前仿真 综合后仿真

赞

踩

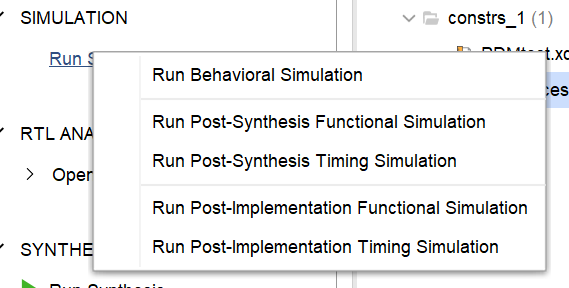

Vivado中的五种仿真模式

在数字电路设计过程中,通常涵盖三个主要阶段:源代码编写、综合处理以及电路的实现,相应地,电路仿真的应用也与这些阶段紧密相关。根据不同设计阶段的需求,仿真可以被划分为RTL行为级仿真、综合后的门级功能仿真以及时序仿真。这样的仿真流程框架不仅适用于FPGA/CPLD的设计,而且也同样适合于集成电路(IC)的设计。

1、run behavioral simulation 行为级仿真,也是通常说的功能仿真

2、post-synthesis function simulation 综合后的功能仿真

3、post-synthesis timing simulation 综合后带时序信息的仿真

4、post-implementation function simulation 布线后的功能仿真

5、post-implementation timing simulation 布局布线后带时序信息的仿真,最接近真实的时序波形**

注: 如果行为仿真下面的四个模式是灰色的无法选中说明你还没有对你的文件进行综合和布局布线还未生成相应的网表和延时信息等待无法进行仿真。

模式比较

1.行为仿真(Behavioral Simulation)

- 目的:行为仿真(功能仿真)主要用于设计的早期阶段,可以用来检查代码中的语法错误以及代码行为的正确性。在这个阶段,关注的是逻辑是否实现了预期的功能,而不是设计在实际硬件中的表现。

- 仿真过程:不考虑时序信息、电路的实际布局或是电路的物理实现细节。它仅仅基于寄存器传输级(RTL)代码来模拟电路逻辑的行为。

- 优缺点:优点在于仿真速度快,可以迅速迭代和验证不同的设计想法。缺点是无法捕捉到因时序、布局或是实现细节导致的问题。

2. 综合后的功能仿真(Post-Synthesis Functional Simulation)

- 目的:在综合过程将RTL代码转换为门级网表之后进行的功能验证。仿真网表已经是与生产厂家的器件的底层元件模型对应起来了,综合后仿真必须在仿真过程中加入厂家的器件库,对仿真器进行一些必要的配置。

- 仿真过程:使用综合后的网表来模拟电路的功能,可以捕获综合过程可能引入的逻辑错误。

- 优缺点:提供了对综合过程影响的初步评估。虽然考虑了综合变化,但仍不包括时序信息。

3. 综合后带时序信息的仿真(Post-Synthesis Timing Simulation)

- 目的:对于需要进行时序仿真的情况,综合工具可以生成SDF文件,该文件包含了综合后的设计中各个元素的延迟信息。SDF文件用于后续的时序仿真中,以确保设计满足时序要求。

- 仿真过程:考虑了信号传播延迟和其他时序约束,仿真结果更接近真实硬件的行为。

- 优缺点:能够发现由时序约束导致的潜在问题。仿真速度较慢,因为需要模拟更多的时序细节。

4. 布线后的功能和时序仿真

该方式的仿真目标和进行综合之后的仿真相似,实现阶段与布线操作紧密相关,其核心目的是把综合产生的逻辑网表适配到选定的FPGA/CPLD芯片上。实现流程的关键步骤是布局与布线(Place and Route):布局负责将逻辑单元有效地映射到FPGA的内部硬件结构中,而布线则依据布局结果,使用FPGA内部的连接资源来精确地连结这些元件。时序仿真环节会把布局布线引入的延迟信息重新应用于设计网表上进行仿真,这时候的仿真包括了门级延迟和连线延迟,使得这一阶段的仿真结果最为精确,能够有效地映射出芯片在实际运行中的工作表现。