- 1Java 继承,多态,接口练习_java继承接口程序分析题

- 2chroma 向量库使用;查询、更新与插入_chroma如何更新库

- 3转行想做 Python Web 开发,需要掌握哪些技能呢?_python web工程师要学vue吗

- 4【活动预告】2024 全球机器学习技术大会|大模型训练故障自愈技术与实践分享_dlrover训练故障自愈:大幅提升大模型ai训练的算力效率

- 5macOS配置Maven和环境变量_mac配置maven环境变量

- 6HBuilderX开发工具介绍

- 7Stable Diffusion再次升级!SDXL1.0大模型的发布让SD的使用体验感更上一层楼!_stable diffusion sdxl 1.0

- 82021年危险化学品经营单位安全管理人员考试题库及危险化学品经营单位安全管理人员找解析_某建材商店地下涂料仓库内存放大量三无产品聚氨酯涂料

- 9macOS 安装redis

- 10Java高阶数据结构-----并查集(详解)_java并查集库

【小技巧】vivado编译时,提示149characters错误_vivado是干什么的

赞

踩

目录

1.1 Vivado简介

Vivado是Xilinx公司推出的一款EDA(电子设计自动化)工具,用于设计和验证高性能的集成电路和系统。Vivado集成了设计套件,包括Block Design、Verilog HDL语言、Xilinx的IP Integrator、High-Level Synthesis工具,以及其他的设计工具和仿真工具。

Vivado支持多种数据输入方式,包括Block Design、Verilog、VHDL、SystemC和SystemVerilog等设计语言。它内嵌了综合器、布局布线器、仿真器等工具,可以完成从设计输入、综合适配仿真到下载到FPGA器件的完整FPGA设计流程。

Vivado还支持高级的调试和分析功能,例如设计检查、设计修复、运行时分析和调试等。它还可以进行时序分析和约束条件分析,以确保设计的时序正确性和可实现性。

在使用Vivado进行FPGA设计时,需要先创建一个工程,然后在工程中添加设计文件。设计文件可以是RTL设计文件、约束文件等。在完成设计输入后,Vivado会对设计进行综合和适配,生成可下载到FPGA器件的比特流文件。

Vivado还支持HLS(High-Level Synthesis)工具,可以将C、C++和SystemC等高级语言直接转换为RTL级别的设计。这大大简化了FPGA设计的流程,提高了设计的效率。

总之,Vivado是一款功能强大的EDA工具,可以用于设计和验证高性能的集成电路和系统。它支持多种设计输入方式,内嵌了综合器、布局布线器、仿真器等工具,可以完成从设计输入到下载到FPGA器件的完整FPGA设计流程。同时,Vivado还支持高级的调试和分析功能,可以大大提高设计的效率和质量。

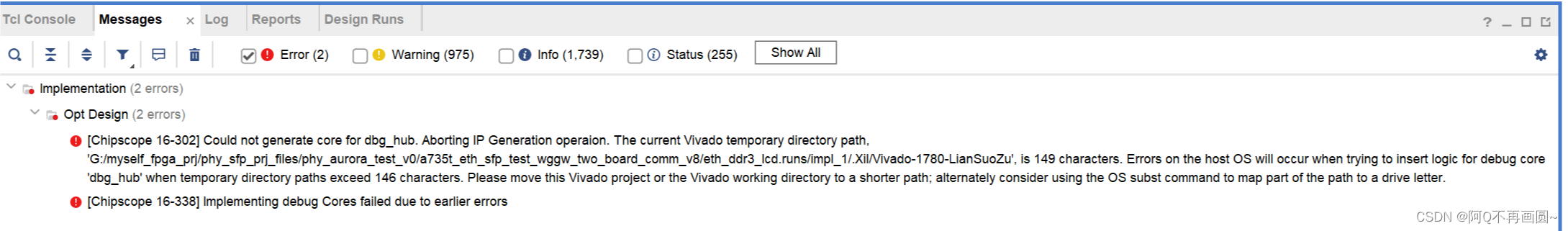

1.2 149characters错误

Vivado是一个复杂的EDA(电子设计自动化)工具,用于设计和验证高性能的集成电路和系统。在Vivado编译过程中,如果出现文件夹路径149字符错误,这通常是由于以下原因导致的:

- 文件夹路径长度超过149个字符:Vivado限制了文件夹路径的长度,以避免过长的路径名对文件系统造成问题。如果您的文件夹路径超过了149个字符,Vivado将无法访问和编译该文件夹中的文件。

- 无效的文件夹路径:另一个可能的原因是您提供的文件夹路径无效或不存在。请确保您提供的路径是正确的,并且具有适当的访问权限。

如下图所示:

1.3 149characters错误解决办法

要解决这个问题,可以采取以下步骤:

- 缩短文件夹路径:如果您的文件夹路径过长,请尝试将文件夹移动到一个更接近项目文件夹的父级目录,以缩短路径长度。另外,您还可以考虑重命名文件夹,以使其更短。

- 检查文件夹路径的正确性:确认您提供的路径是正确的,并且具有适当的访问权限。请注意,Vivado通常会提示您关于权限问题的错误消息。

- 重新启动Vivado:有时候,重新启动Vivado可以解决一些临时的问题。

如果上述步骤无法解决问题,您可以尝试以下方法:

- 创建新的文件夹:如果您的原始文件夹路径无效或过长,您可以考虑在有效的地方创建一个新的文件夹,并将项目文件移动到新文件夹中。

- 联系技术支持:如果您无法解决问题,可以联系Xilinx的技术支持团队,以获取进一步的帮助。

总之,Vivado编译时出现文件夹路径149字符错误是由于文件夹路径长度超过限制或无效路径导致的。通过缩短路径长度、检查路径正确性和重新启动Vivado等方法。