- 1C#中GDI+图形图像技术(Graphics类、Pen类、Brush类)

- 2自定义view的三种方式

- 3深入解析分布式数据库的 SQL 引擎优化_sql引擎

- 4【2024华为OD机试C卷】387、密码输入检测 | 机试真题+思路参考+代码解析(C语言、C++、Java、Py、JS) (最新抽中C卷)(本题100%)_密码输入检测华为od真题

- 5flink启动后web访问问题_flink启动后web页面打不开

- 6【k8s】K8S中的IP地址(Node IP、Pod IP、Cluster IP、External IP、Internal-IP)

- 7docker配置redis主从复制

- 8解决动画函数点击按钮后可能出现的Bug---动画越来越快的问题(方案)_animejs 点击按钮动画加快

- 9Python 微信群聊自动回复_python微信群聊自动回复

- 10(仿牛客社区项目)Java开发笔记8.4:项目总结及常见面试题_仿牛客论坛项目面试题

7 series FPGAs GTX资源及工作原理_prbs checker

赞

踩

目录

5、TX Buffer(Phase Adjust Fifo)... 9

第一章 GTX概述

“GT”是Gigabyte Transceiver的缩写,意思是G比特收发器;“X”指具体的型号。GTX支持500Mb/s~12.5Gb/s的数据速率。

图 1 GTX数据传输

如图1,txdata和rxdata是来自用户逻辑的并行数据;GTX模块主要功能是实现串并转换、并串转换,在模拟电路中使用单bit传输。光模块是将电信号转为光信号,使信号通过光纤进行传输。

第二章 GTX结构

1、GTX资源封装

不同FPGA芯片有不同数量的GT资源,以XC7K325T-2FFG900I芯片为例,封装方式是“FFG900”,该芯片有四个GTX BANK(或称GTX Quad),每个BANK有四个CHANNAL。

可以根据封装方式,查阅UG476文档345~467页,查看GT资源及封装情况。

图 2 XC7K325T-2FFG900I GTX资源封装情况

如图2,每个BANK包含1个GTXE2_COMMON(例化QPLL)和4个GTXE2_CHANNEL(例化TX、RX、CPLL)。

图 3 BANK资源

如图3,每个CHANNEL都包含1个Transmitter(TX)、1个Receiver(RX)和1个CPLL。

2、项目示例

图 4 ADC2HTXT板原理图GTX资源

如图4,下面以ADC2HTXT板为例进行GTX资源分析。该板板载XC7K325T-2FFG900I 芯片,在4个BANK中只使用了BANK115;且在BANK115的4个CHANNAL中,只使用了CHANNAL X0Y0。

在BANK115中,“MGTXTXP0_115、MGTXTXN0_115”是TX,“MGTXRXP0_115、MGTXRXN0_115”是RX。“MGTREFCLK0P_115、MGTREFCLK0N_115”是参考时钟REFCLK0,“MGTREFCLK1P_115、MGTREFCLK1N_115”是参考时钟REFCLK1;在IP设置中可选择其中一路作为参考时钟。

第三章 Transmitter(TX)

图 5 GTX Transceiver TX Block Diagram

1、PMA与PCS

如图5,TX由两个子层组成,分别是PCS(Physical Coding Sublayer)和PMA(Physical Media Attachment)。PCS属于逻辑层;PMA属于物理层。

2、TX Interface

1)端口位宽

TX Interface是FPGA的发送数据通道。用户逻辑在 TXUSRCLK2上升沿将数据写入TXDATA端口,端口位宽可以配置为2、4或8字节。

图 6 TX端口位宽

如图6,端口的实际位宽取决于TX_DATA_WIDTH和TX_INT_DATAWIDTH属性和TX8B10BEN端口设置。

2)时钟关系

“FPGA TX Interface”包括两个平行时钟:TXUSRCLK和TXUSRCLK2。

TXUSRCLK用于驱动内部的PCS逻辑,它的频率取决于GTXE2_CHANNEL的内部数据位宽(Internal Datapath Width)和TX线速率(Line Rate)。具体的计算公式如下:

TXUSRCLK2是信号进入TX的同步时钟,其频率由TX线速率、TXDATA端口的宽度(TX_DATA_WIDTH)以及是否启用8B/10B编码决定。

图 7 TXUSRCLK 与TXUSRCLK2的频率关系

如图7,TXUSRCLK和TXUSRCLK2有一个基于TX_DATA_WIDTH和TX_INT_DATAWIDTH的固定速率关系。同时,两者必须满足以下条件:

①TXUSRCLK和TXUSRCLK2必须是上升沿对齐,它们之间的偏斜尽可能小。因此,应该用低偏斜的时钟资源来驱动它们。

②尽管两者的频率不一定相同,但是它们必须和TX参考时钟以同一个振荡器作为时钟源。因此TXUSRCLK和TXUSRCLK2的频率一定是倍数关系。

3、TX 8B/10B Encoder

1)功能描述

8B/10B编码有平衡电平,防止连续1/0的功能,利于接收端恢复信号,编码分为D码和K码,最常用的K码是k28.5。它优势在于自带错误检测,当出现8B/10B错误的时候,大概率是链路质量有问题。同时,8B/10B劣势是有20%的额外开销。

除了8B/10B编码以外,还有其他的很多编码方式,比如64B/66B编码,Gearbox就是为这一类编码准备的。

2)Running Disparity

8B/10B编码是DC平衡的,即传输的1和0的长期比率应该正好是50%。为此,编码器总是计算发送1的个数与发送0的个数的差值,并且在最后传输的每个字符的末尾,会产生+1或-1的差异。这个差异叫做running disparity。

4、TX Gearbox

一些高速数据协议使用64B/66B(或64B/67B)编码协议来减少8B/10B的开销;此时,TX Gearbox为64B/66B(或64B/67B)提供header和data的有效结合。例如64B/66B编码中,TX Gearbox功能被启用,输入数据由2bits header和32bits data组成,则header输入TXHEADER端口,而数据输入TXDATA端口,两者被共同送进TX Gearbox进行下一步传输。

5、TX Buffer(Phase Adjust Fifo)

如图5,GTX收发器的内部有两个平行时钟域,分别是PMA的并行时钟域和PCS的并行时钟域(用户时钟USRCLK)。为了正确无误的传输数据,XCLK的速率必须匹配USRCLK的速率,而TX Buffer用于两个时钟域数据的缓冲。

6、TX Buffer Bypass

当不使用TX Buffer时,TX相位校准电路被启用。TX相位校准电路用于调整PISO并行时钟域(TXUSRCLK)和TX XCLK域之间的相位差,将数据从PCS传输到PISO。它还通过不断调整TXUSRCLK来补偿温度和电压的变化来实现TX延迟校准。

7、TX Pattern Generator

该模块用于产生伪随机比特序列(PRBS),该序列常用来测试高速链路的信号完整性,这些序列看似随机,但是是有规律的周期性二进制数列,有良好的随机性和接近白噪声的相关函数,所以伪随机数列可以用来做误码率测量、时延测量、噪声发生器、通信加密和扩频通信等等领域,在GTX中可以用来测试高速串行通道传输的误码率。

图 8 PRBS 模式(部分)

8、TX Polarity Control

如果TXP和TXN差分端口在PCB上被不小心弄反,则可通过该模块对GTX/GTH收发器TX传输的差分数据做极性转换。具体方法是对TXPOLARITY端口进行赋值,‘0’表示不翻转极性;‘1’表示翻转极性。

9、PISO

PISO是Parallel In Serial Out的缩写,意为并行输入串行输出。该模块实现并串转换。

10、TX Pre/Post Emp

该模块实现预加重。预加重(Pre-emphasis):信号传输线表现出来的是低通滤波特性,传输过程中信号的高频成分衰减大,低频成分衰减少。信号频率的高低主要是由信号电平变化的速度决定的,所以信号的高频分量主要出现在信号的上升沿和下降沿处,预加重技术就是增强信号上升沿和下降沿处的幅度。

图 9 预加重原理

11、TX OOB

OOB是Out of Band的缩写,指带外信号。OOB信号是物理层特有的一组信号,它通过在数据线上传输一组特定格式的信号实现。OOB信号有3个,分别是COMRESET、COMINIT和COMWAKE,其中COMRESET与COMINIT信号组成形式一样,只不过CONRESET由主机发出,而COMINIT由设备发出,它们的作用是在正常的通信链路没有建立之前主机进行SATA设备识别。

12、TX Driver

GTX/GTH收发器的TX Driver是一个高速电流模式差分输出缓冲区。

图 10 TX Configurable Driver

如图10,输出阻抗为50Ω;当需要使用预加重时,可通过TXPRECUESOR、TXPOSTCURSOR端口控制加重值;可通过TXDIFFCTRL端口控制驱动器差分电压摆幅。详见UG476 Table3-30。

第四章 Receiver(RX)

图 11 GTX Transceiver RX Block Diagram

1、PMA与PCS

如图11,RX也由PMA和PCS两子层构成。PMA子层包括接收均衡、时钟数据恢复、并串转换电路等;PCS子层包括8B/10B解码、缓冲区、通道绑定、时钟修正等电路。

2、RX Driver

图 12 RX Driver

如图12,可通过调节接收端负载电压来使阻抗匹配。阻抗匹配(Impedance Matching)主要用于传输线上,以此来达到所有高频的微波信号均能传递至负载点的目的,而且几乎不会有信号反射回来源点,从而提升能源效益。

2、RX EQ

传输介质或信道的带宽是有限的,通过它的信号会受到衰减和失真。根据系统在功率和性能之间的权衡,有两种自适应滤波模式可供GTX/GTH接收机使用,分别是功耗优化和低通道损耗的低功耗模式(LPM)与均衡更低损耗通道的判决反馈均衡模式(DFE)。详见UG476 Page184~186。两者功耗和性能有所不同,其中LPM功耗较低,DFE能提供更精确的滤波器参数,从而可以更好的补偿传输信道损失,因此性能更好。

3、RX CDR

每一个GTXE2_CHANNEL都有时钟数据恢复(CDR)电路,它从数据流中提取出时钟和数据。

图 13 CDR细节

如图13,传入的数据首先要经过接收机均衡阶段,均衡处理后的数据被边缘采样器和数据采样器捕获。数据采样器捕获的数据被馈送到CDR状态机和下游收发器模块。

CDR FSM使用来自边缘采样器和数据采样器的数据来确定传入数据流的相位并控制相位插入器(PIs)。

CPLL或QPLL为相位插入器提供一个基准时钟(如图24)。相位插补器反过来产生精细、均匀间隔的采样相位,使CDR FSM具有精细的相位控制。因此图13中的恢复数据RXDATA和恢复时钟Recovered Clock与本地参考时钟有一定的相位偏移。

4、SIPO

SIPO是Serial In Parallel Out的缩写,意为串行输入并行输出。该模块实现串并转换。

5、RX Polarity Control

如果RXP和RXN差分端口在PCB上被不小心弄反,则可通过该模块对GTX/GTH收发器RX传输的差分数据做极性转换。具体方法是对RXPOLARITY端口进行赋值,‘0’表示不翻转极性;‘1’表示翻转极性。

5、Comma Detect and Align

串行数据在被并行化之前,需要找到一个合适的特征边界,这个特征边界或者字符边界是由TX发送端发送的一个可识别序列,通常称为Comma。

图 14 数据对齐原理

如图14,接收模块会在接收数据流中搜索Comma,当它找到一个Comma时,将其移动到字边界,并以此为边界对后面的数据进行并行化,以便接收到的并行字与传输的并行字匹配。

6、PRBS Checker

GTX/GTH接收器包括一个内置的PRBS检查器;检查器有四种模式可供选择,用来测试信道的信号完整性。

图 15 RX Pattern Checker

7、8B/10B Decoder

如果接收到的RX数据采用8B/10B编码,那么它必须被解码。GTX RX在数据路径上包含4个单字节的8B/10B解码器模块。

图 16 8B/10B Decoder Bit and Byte Order

如图16,以RX_DATA_WIDTH=40为例,8B/10B解码需要先接收a0位,但GTX/GTH收发器总是先接收最右边的位。因此,8B/10B解码器在解码前自动反转接收数据的位序。

8、RX Buffer

如图11,RX端也有RX Buffer用于解决两个不同时钟域下(恢复时钟XCLK和用户时钟RXUSRCLK)的相位差问题。为了正确接收数据,PMA并行速率必须足够接近RXUSRCLK速率,而RX Buffer用于两个时钟域数据的缓冲。RX Buffer还可用于时钟矫正和通道绑定。

9、RX Buffer Bypass

图 17 Using RX Phase Alignment

如图17,当不使用RX Buffer时,RX相位校准电路被启用。RX相位校准电路用于调整SIPO并行时钟域和RX XCLK域之间的相位差,以实现从SIPO到PCS的可靠数据传输。它还通过不断调整RXUSRCLK来补偿温度和电压的变化来实现RX延迟校准。

当RX恢复时钟被用于源RXUSRCLK和RXUSRCLK2时(详见第五章第1节中RXOUTCLK时钟选择介绍),RX Buffer可以被绕过以减少延迟;但此时,时钟校正和通道绑定是不可用的。

10、RX Gearbox

RX Gearbox实现对64B/66B(或64B/67B)的header和data有效分离。

图 18 RX Gearbox

如图18,RXDATAVALID是RXDATA的有效信号;RXHEADERVALID是RXHEADER的有效信号。RXSTARTOFSEQ表示当前RXDATA输出计数器为0。RXGEARBOXSLIP实现与FPGA逻辑的对齐。将该信号拉高1个RXUSRCLK2周期,来改变从Gearbox出来的数据的对齐时序;且在开始新一次对齐调整操作时,RXGEARBOXSLIP必须被拉低至少一个周期后再拉高。

11、RX Interface

1)端口位宽

RX Interface是FPGA的接收数据通道。应用程序通过从RXUSRCLK2上升沿的RXDATA端口读取数据,端口宽度可以配置为2、4或8字节。

图 19 RX端口位宽

如图19,端口的实际位宽取决于RX_DATA_WIDTH和RX_INT_DATAWIDTH属性和RX8B10BEN端口设置。

2)时钟关系

“FPGA RX Interface”包括两个平行时钟:RXUSRCLK和RXUSRCLK2。

RXUSRCLK用于驱动内部的PCS逻辑,它的频率取决于GTXE2_CHANNEL的内部数据位宽(Internal Datapath Width)和RX线速率(Line Rate)。具体的计算公式如下:

RXUSRCLK2是信号进入RX的同步时钟,其频率由RX线速率、RXDATA端口的宽度(RX_DATA_WIDTH)以及是否启用8B/10B编码决定。

图 20 RXUSRCLK 与RXUSRCLK2的频率关系

如图20,RXUSRCLK和RXUSRCLK2有一个基于RX_DATA_WIDTH和RX_INT_DATAWIDTH的固定速率关系。同时,两者必须满足以下条件:

①RXUSRCLK和RXUSRCLK2必须是上升沿对齐,它们之间的偏斜尽可能小。因此,应该用低偏斜的时钟资源来驱动它们。

②尽管两者的频率不一定相同,但是它们必须和RX参考时钟以同一个振荡器作为时钟源。因此RXUSRCLK和RXUSRCLK2的频率一定是倍数关系。

第五章 时钟资源

图 21 GTX Transceiver Quad Configuration

如图21:

①每个Quad包含一个QPLL(or LC tank,LC谐振回路)和四个CPLL(or ring oscillator,环形振荡器);

②QPLL由GTXE2_COMMON实现,用于整个Quad;CPLL由GTXE2_CHANNEL实现,只可用于当前CHANNEL。

③7系列GTX Transceiver同时支持QPLL或CPLL作为时钟源。CPLL支持的线速率为1.6G~3.3G,而QPLL支持的线速率高达12.5G,因此在高速率的要求下,需使用QPLL而不是CPLL。

1、CPLL

1.1 CPLL端口说明

图 22 CPLL Reference Clock Selection Multiplexer

CPLL由原语GTXE2_CHANNEL实现,其时钟端口如下表所示。

表 1 GTXE2_CHANNEL Clocking Ports

| 信号名称 | 位宽 | I/O | 信号描述 |

| CPLLREFCLKSEL[2:0] | 3 | I | 参考时钟选择端;当只有一个时钟源连接到CPLL的多路选择器时,该输入应设为3’b001。 000:保留 001:选择GTREFCLK0 010:选择GTREFCLK1 011:选择GTNORTHREFCLK0 100:选择GTNORTHREFCLK1 101:选择GTSOUTHREFCLK0 110:选择GTSOUTHREFCLK0 111:选择GTGREFCLK |

| GTGREFCLK | 1 | I | 内部产生的参考时钟,仅用于内部测试 |

| GTNORTHREFCLK0 | 1 | I | 北面的时钟(Quad下方) |

| GTNORTHREFCLK1 | 1 | I | 北面的时钟(Quad下方) |

| GTREFCLK0 | 1 | I | IBUFDS_GTE2 驱动的外部时钟 |

| GTREFCLK1 | 1 | I | IBUFDS_GTE2 驱动的外部时钟 |

| GTSOUTHREFCLK0 | 1 | I | 南面的时钟(Quad上方) |

| GTSOUTHREFCLK1 | 1 | I | 南面的时钟(Quad上方) |

| QPLLCLK | 1 | I | 来自QPLL时钟输出 |

| QPLLREFCLK | 1 | I | 来自QPLL参考时钟输出 |

| RXSYSCLKSEL[1:0] | 1 | I | 选择驱动RX数据的参考时钟: RXSYSCLKSEL[0] = 1'b0 (CPLL) 选择驱动RXOUTCLK的参考时钟: RXSYSCLKSEL[1] = 1'b0 (reference clock from GTXE2_CHANNEL) |

如图22所示,GTXE2_CHANNEL内置一个多路选择器,通常情况下只有一个时钟源连接到选择器,CPLLREFCLKSEL[2:0]设为3’b001。

1.2 CPLL细节

图 23 CPLL细节

在GTX中CPLL标称工作范围在1.6 GHz~3.3 GHz;在GTH中CPLL标称工作范围在1.6 GHz~5.16GHz;

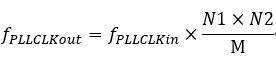

CPLL输出频率计算公式:

线速率计算公式:

图 24 CPLL分频系数设置

如图24,系数M、N、D会根据PLL参考时钟频率、IP核参数设置而确定。

2、QPLL

2.1 QPLL端口说明

图 25 QPLL Reference Clock Selection Multiplexer

QPLL由原语GTXE2_COMMON实现,其时钟端口如下表所示。

表 2 GTXE2_COMMON Clocking Ports

| 信号名称 | 位宽 | I/O | 信号描述 |

| GTGREFCLK | 1 | I | 内部产生的参考时钟,仅用于内部测试 |

| GTNORTHREFCLK0 | 1 | I | 北面时钟(Quad下方) |

| GTNORTHREFCLK1 | 1 | I | 北面时钟(Quad下方) |

| GTREFCLK0 | 1 | I | IBUFDS_GTE2驱动的外部时钟 |

| GTREFCLK1 | 1 | I | IBUFDS_GTE2驱动的外部时钟 |

| GTSOUTHREFCLK0 | 1 | I | 南面时钟(Quad上方) |

| GTSOUTHREFCLK1 | 1 | I | 南面时钟(Quad上方) |

| QPLLOUTCLK | 1 | O | QPLL时钟输出 |

| QPLLOUTREFCLK | 1 | O | QPLL参考时钟输出 |

| QPLLREFCLKSEL[2:0] | 3 | I | 参考时钟选择端;当只有一个时钟源连接到QPLL的多路选择器时,该输入应设为3’b001。 000:保留 001:选择GTREFCLK0 010:选择GTREFCLK1 011:选择GTNORTHREFCLK0 100:选择GTNORTHREFCLK1 101:选择GTSOUTHREFCLK0 110:选择GTSOUTHREFCLK0 111:选择GTGREFCLK |

如图25所示,GTXE2_COMMON内置一个多路选择器,通常情况下只有一个时钟源连接到选择器,QPLLREFCLKSEL[2:0]设为3’b001。

2.2 QPLL细节

在同一个Bank内,QPLL可以被所有Channel共用。当以高于CPLL工作范围的线速率操作信道时,需要使用QPLL。

图 26 QPLL细节

如图26,输入时钟在被送入相频检测器之前被M分频,反馈系数N决定压控振荡器的倍增系数。QPLL输出频率是压控振荡器频率的一半。锁定指示器比较参考时钟和VCO反馈时钟的频率,以确定频率锁定是否已经实现。

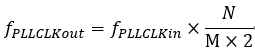

PLL输出频率计算公式:

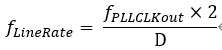

线速率计算公式:

图 27 QPLL分频器设置

如图27,系数M、N、D会根据PLL参考时钟频率、IP核参数设置而确定。

3、TX时钟结构

图 28 TX Serial and Parallel Clock Divider

如图28:

1.QPLLREFCLK是QPLL参考时钟;QPLLCLK是QPLL输出时钟。

2.Phase Interp(PI)是相位插值器。可通过一个TX PI来控制锁相环的输出时钟,而这个输出时钟又可以通过TXPIPPM(TX相位插补器PPM控制器模块)来微调控制。TXPIPPM位于TX PCS,其输入来自FPGA TX Interface,并输出到TX PMA。

3.D1是串行时钟分频器(图23中的D)。该模块将时钟从PLL中分离出来,以获得更低的线速率支持。其分频系数D设置如下:

图 29 TX PLL输出分频器设置

4.D2分频器被TX_INT_DATAWIDTH属性控制。TX_INT_DATAWIDTH = 0时,选择“/2”;TX_INT_DATAWIDTH = 1时,选择“/4”。

5.D3分频器被TX_DATA_WIDTH属性控制。TX_DATA_WIDTH= 16,32或64时,选择“/4”;TX_DATA_WIDTH = 20,40或80时,选择“/5”。

TXOUTCLK用于驱动用户时钟TXUSRCLK和TXUSRCLK2。其源可根据TXOUTCLKSEL进行选择(UG476 Page 151~152):

①TXOUTCLKSEL = 3’b001:不推荐使用TXOUTCLKPCS路径,因为它会导致来自PCS模块的额外延迟。

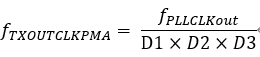

②TXOUTCLKSEL = 3’b010:TXOUTCLKPMA是在TX相位插入器,并被TX PCS块使用。当PLL被一个相关的复位信号复位时,这个时钟被中断。其频率计算公式如下:

③TXOUTCLKSEL = 3’b011或3’b100:TXPLLREFCLK_DIV1或'TXPLLREFCLK_DIV2是CPLL/QPLL的输入参考时钟,取决于TXSYSCLKSEL[1]设置。当TXPLLREFCLK为用户时钟频率的1或2倍时,推荐使用TXPLLREFCLK是作为输出;同时它是TX Buffer Bypass模式所需要的

4、RX时钟结构

图 30 TX Serial and Parallel Clock Divider

如图30:

1.QPLLREFCLK是QPLL参考时钟;QPLLCLK是QPLL输出时钟。

2.CDR是时钟数据恢复电路,内置相位插值器。

3.D1是串行时钟分频器(图23中的D)。该模块将时钟从PLL中分离出来,以获得更低的线速率支持。其分频系数D设置如下:

图 31 RX PLL输出分频器设置

4.D2分频器被RX_INT_DATAWIDTH属性控制。RX_INT_DATAWIDTH = 0时,选择“/2”;RX_INT_DATAWIDTH = 1时,选择“/4”。

5.D3分频器被RX_DATA_WIDTH属性控制。RX_DATA_WIDTH= 16,32或64时,选择“/4”;RX_DATA_WIDTH = 20,40或80时,选择“/5”。

与TX端不同,RX端有CDR电路用于恢复数据和时钟,恢复时钟用于RX PCS,也可以带出至FPGA。RXOUTCLK用于驱动用户时钟RXUSRCLK和RXUSRCLK2,其源可根据RXOUTCLKSEL进行选择(UG476 Page 212):

①RXOUTCLKSEL = 3’b001:不建议使用RXOUTCLKPCS路径,因为它会导致来自PCS模块的额外延迟。

②RXOUTCLKSEL = 3’b010:RXOUTCLKPMA是恢复的时钟,它被PCS所使用,并可以带出到FPGA逻辑。恢复的时钟被没有时钟补偿机制的协议所使用,这些协议要求使用与数据同步的时钟来驱动下游逻辑。当PLL或CDR被一个相关的复位信号复位时,这个时钟被中断。

③RXOUTCLKSEL = 3’b011或3’b100:RXPLLREFCLK_DIV1或RXPLLREFCLK_DIV2是CPLL/QPLL的输入参考时钟,取决于RXSYSCLKSEL[1]设置。对于不需要将恢复的时钟输出到下游逻辑的情况,可以使用RXPLLREFCLK_DIV1或RXPLLREFCLK_DIV2作为系统时钟。但是,通常将TXOUTCLK用作系统时钟。

1)条件设置

①GTX参考时钟频率(QPLL参考)为200MHz,即fPLLCLKin=200MHz;

②线速率为10Gbps,即fLineRate=10Gbps;

③用户数据位宽为32bit且使用8B/10B编码,即TX_INT_DATAWIDTH=1、TX_DATA_WIDTH=40;

2)时钟分析

根据参数设置,IP核会自动计算,确定分频系数M、N、D的值。

图 32 IP内部QPLL_REFCLK_DIV参数

根据图27与图32,得到系数M为2。

图 33 分频系数N设置

图 34 IP内部QPLL_FBDIV、QPLL_FBDIV_RATIO参数

根据图33与图34,得到系数N为100。

图 35 IP内部参数RXOUT_DIV、TXOUT_DIV参数

根据图27与图35,得到系数DTX、DRX为1。

根据计算公式:

第六章 复位和初始化

1、复位流程

FPGA设备上电后,需按照以下步骤进行复位后才能使用,复位步骤如下:

1.初始化TX/RX使用的PLL(QPLL/CPLL);

2.初始化TX/RX数据链路(PMA+PCS)。

PLL和TX/RX的复位是完全独立的,且必须在相关PLL锁定之后才能进行TX/RX复位。

图 36 GTX Transceiver Initialization Overview

GTX收发器用状态机控制初始化进程,它被分为多个复位域,使状态机可以按顺序复位各域。TX状态机复位流程如下(RX与之类似):

1)ASSERT_ALL_RESETS:拉高GTTXRESET,QPLL_RESET拉高一个周期(下降沿触发,实际的复位时间远不止1个周期);

2)WAIT_FOR_PLL_LOCK:等待500ns(等待PLL锁定);

3)RELEASE_PLL_RESET:QPLL复位完成并锁定;

4)WAIT_FOR_TXOUTCLK:拉低GTTXRESET,开始复位TX PMA;等待500ns;

5)RELEASE_MMCM_RESET:等待MMCM锁定(没使用MMCM时,直接进入下一状态);

6)WAIT_FOR_TXOUTCLK:等待500ns;

7)WAIT_RESET_DONE:拉高TXUSERRDY,开始复位TX PCS,等待TXRESETDONE拉高后进入下一状态;

8)DO_PHASE_ALIGNMENT:拉高run_phase_alignment_int,等待PHALIGNMENT_DONE进入下一状态(没使用phase_alignment时,直接进入下一状态)

9)RESET_FSM_DONE:拉高tx_fsm_reset_done_int,完成复位;除非对状态机进行复位,否则状态机一直停留在此状态。

2、复位分类

GTX收发器提供两种复位类型:

Initialization reset:此复位用于整个GTX收发器初始化;GTTXRESET复位TX;GTRXRESET复位RX;

Component reset:当GTX/GTH收发机处于正常工作状态时,这种复位用于特殊情况和特定部分复位。TX component reset包括TXPMARESET和TXPCSRESET;RX component reset包括RXPMARESET、RXDFELPMRESET、EYESCANRESET、RXPCSRESET、RXBUFRESET和RXOOBRESET。

各复位的作用域如下所示:

图 37 TX初始化复位和组件复位区域

图 38 RX初始化复位和组件复位区域