- 1大数据处理算法三:分而治之/hash映射 + hash统计 + 堆/快速/归并排序_大数组hash计算

- 2fpga定点数表示数据的理解_小于1的小数和大于1的小数的定点化

- 3SpringBoot Druid对配置文件中数据库密码加密_druid的配置文件

- 4fork一个github上的project后,同步更新

- 5大模型PEFT(一)之推理实践学习记录_peft精调后推理

- 6Prim算法:最小生成树的构建_prim算法怎么构建最小生成树

- 7KubeBlocks v0.9发布啦!API全面升级、支持Redis Cluster、MySQL主备...更多新功能等你发现!

- 8软件测试方法和技术---简答题题库(极简速记)

- 9mysql8强制用户开启ssl_mysql8.0 使用 x509设置加密连接

- 10如何只提交特定的代码块?使用git add -p

jtag接口原理图_在开始高速接口前,我们来试试IBERT测试吧!

赞

踩

第一次在知乎上发文章,一想到我只是个IP手册翻译大师就犯愁该怎么下笔,既然只会翻译IP手册,那么我就直接来分享一些IP core是怎么用的吧。因为某些原因恰好学习了一些高速接口的IP的使用,所以这个系列也主要讲高速接口方面的东西。

此次实验采用的FPGA平台为Xilinx的评估板KCU116,硬件开发平台采用的是vivado2018.3,IP为IBERT Ultrascale GTY(1.3),详见IP手册PG246

什么是IBERT?

IBERT就是Xilinx提供的集成比特误码率测试仪(Integrated Bit Error Ratio Tester),作为用户来说可以使用这个工具对自己设计的板子中的高速串行收发器进行简单测试,从而判断设计的接口是否有问题。因为这个工具是直接集成到FPGA上,这样一来直接使用这个工具来测试高速接口就方便很多了,它只需要JTAG和测试接口用的连接线就能完成对板子的测试。

当然,在开启高速接口之前得确保接口的传输信号得是正确的,尽管基带信号在信道的传输前进行了一定的信道编码,但是信道质量实在太差的话依旧会造成一定的误码,所以此次实验使用IBERT的主要目的就是要确保信号不受传输过程中的影响,使数据完整无误的从一台设备传到另一台设备。

怎么使用IBERT?

- 新建工程

新建工程就不必多讲了,值得注意的是,本次实验中选用的是KCU116的评估板,在新建工程时注意直接勾选这块评估板就好了,可以在一些免去一些麻烦。

- 配置IP

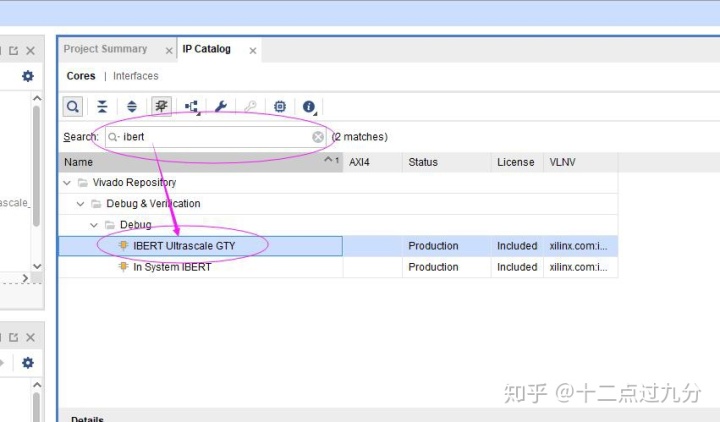

新建好工程之后,在使用IP之前肯定要先找到IP,既然叫“IBERT”,那我们直接在IP Catalog里面直接搜索“ibert”,搜出来的玩意有很多,由于是kcu116,板子上提供的收发器是GTY收发器,所以直接选中图1所示的就好了。(可单击图片查看高清无码画质)

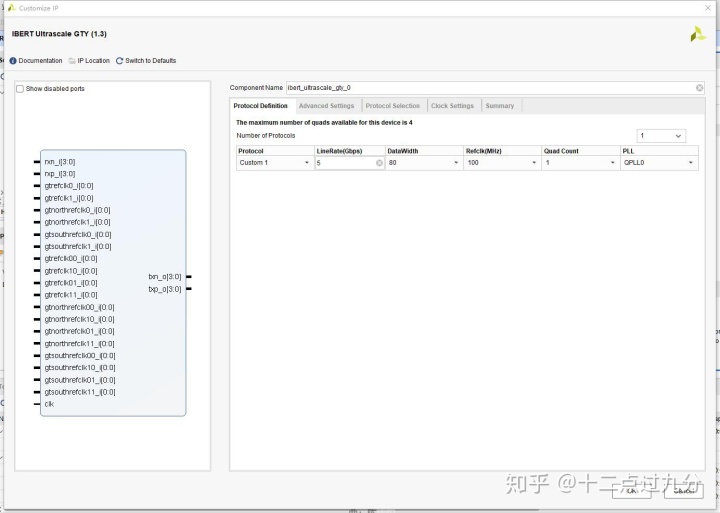

双击进入IP后可以看到如下图2界面,需要设置的内容不多,还是非常友好的,接下来就是一一介绍这些选项是怎么设置的。

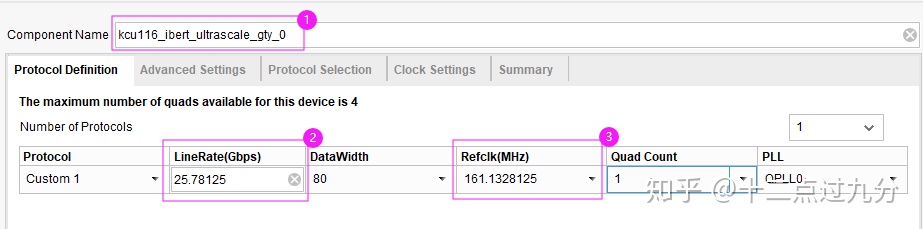

(1)首先是得为这个IP起个名字,比如它叫“kcu116_ibert_ultrascale_gty_0”,当然它叫“abc”也不是不行。

其次是Protocol Definition界面的设置,如下图3所示,主要的是注意LineRate和Refclk两个选项:LineRate,其中GTY收发器对应的速率最高可达32.75 Gbps,也就是在该速率内的选择,但是由于实际需求不同勾选的速率不同,像是把GTY收发器用作25G以太网接口的话其对应的速率为25.78125Gbps(其计算方法可详见以太网接口);Refclk就是GTY收发器所需要的参考时钟了,像是10G以太网对应156.25MHz参考钟,25G以太网对应161.1328125MHz参考钟,这里就选择25G对应的161.1328125MHz。

该页的其他选项诸如protocol的数量,即不同LineRate数量就不同,比如我想在一块板子上既测试10G以太网接口又测试25G以太网接口,可以选择数量2;Quad Count设置项,每一Quad对应4个GTY收发器,根据测试数量决定,这里选1;

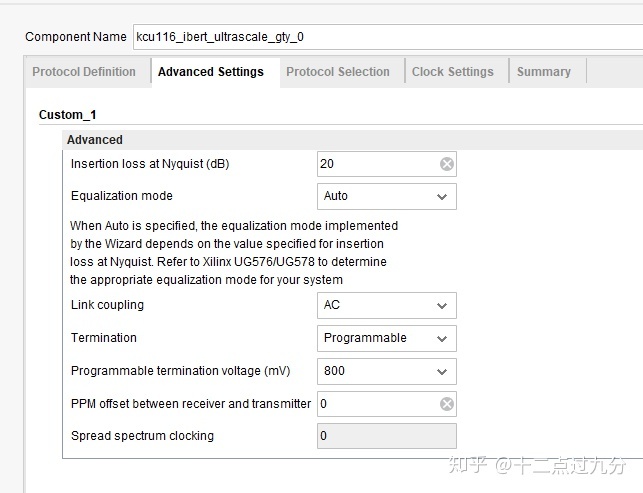

(2)Advanced Settings这个界面主要设置收发器接收端的均衡等内容,保持默认就好了,如下图4所示;

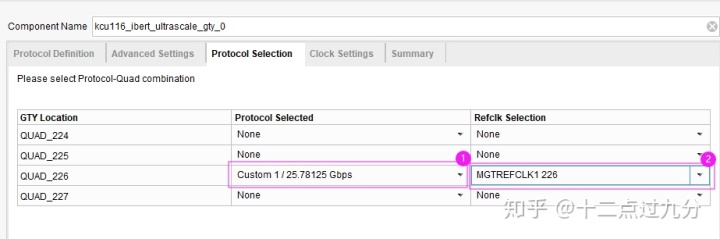

(3)Protocol Selection这个页面主要选择要测试的GTY收发器所在位置,因为此次测试为25G以太网接口,根据KCU116的原理图可知板子的四个万兆口所在bank为226,连接的参考时钟为MGTREFCLK1 226,故按照下图勾选,当然也可以随便勾选一组,之后再按照自己的电路图再修改管脚约束;

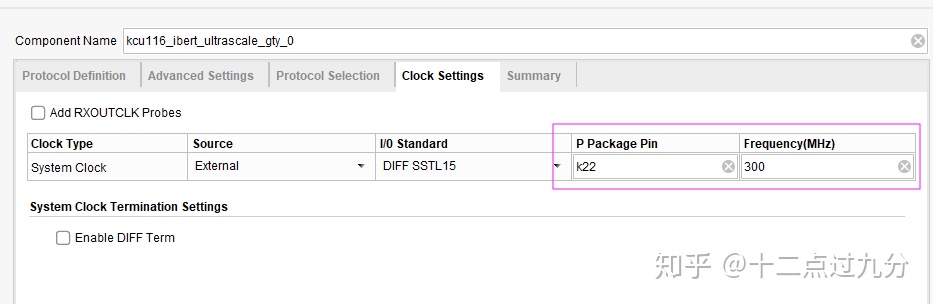

(4)这个选项就是勾选系统时钟,此次使用的是KCU116的板子,其采用的是300M的时钟作为系统时钟,差分钟的p端连的是K22,故可按照下图6所示连接,当然也可以按照自己电路设计进行选择。

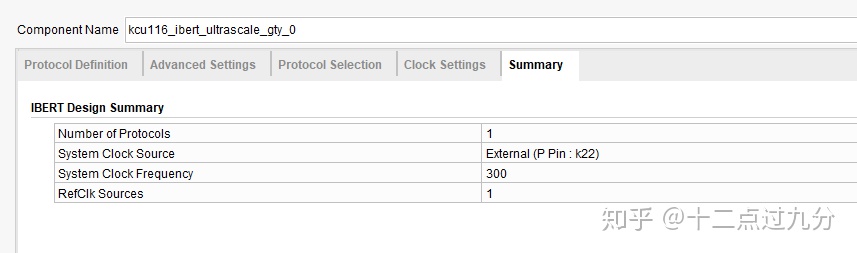

(5)到此IBERT IP核的配置基本结束,在xilinx的板子中由于板子的不同,对应的IP也有所不同,但是大体设置基本一样,总之对于该IP的设置还是十分简单易懂的。

- open IP example design

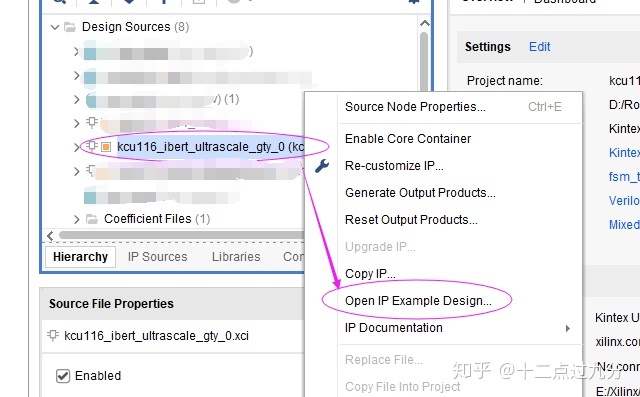

在完成好IP的设置之后,可以在工程下看到综合好的IP模块,单击右键点击open IP example design即可获得基于该IP生成的示例工程,具体操作如下图8所示。

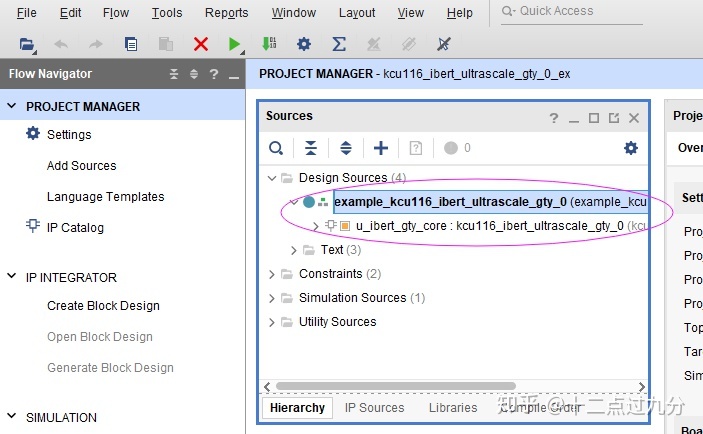

vivado自动生成的示例工程如下图9所示,可以简单观察其基本结构,可以发现该工程把所有的线都连上了并且约束也写好了,故可以直接对其综合和布局布线生成bit。到这一步为止,基本上IBERT测试工程就全部准备好了,接下来只要下载到板子上进行测试就行了。

- 进行测试

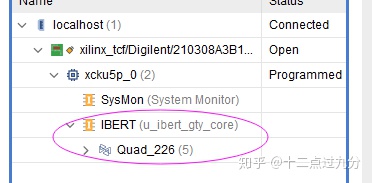

将上述生成好的bit和ltx下载到板子上后可以发现多了下图10这个玩意,这个就是IBERT测试工具;

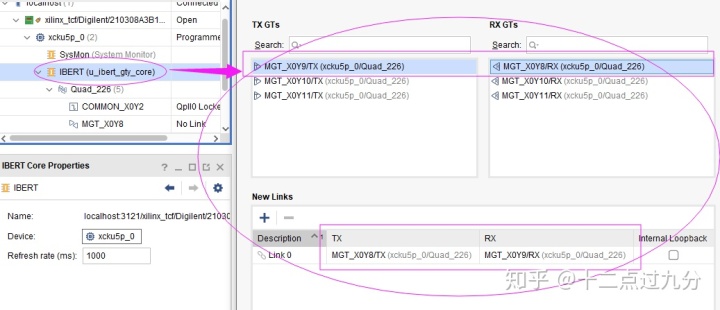

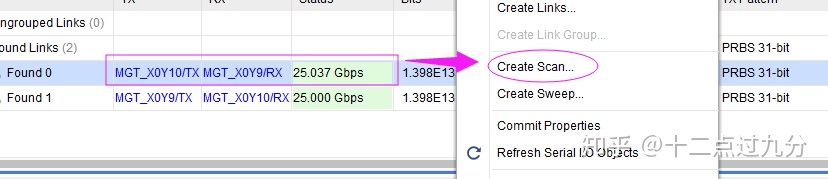

有了这个工具之后,可以在IBERT上右键找到create links,一个GTY收发器包含一个发送端Tx和一个接收端Rx,故有四组Tx、Rx。如果测试是选择一个GTY收发器自发自收可以选择单个收发器的Tx和Rx直接连接;如果选择GTY两两相互收发,可以两个GTY收发器的Tx和Rx端交叉连接等等。这里选择两个收发器相互收发,所以选择如下图11连接。

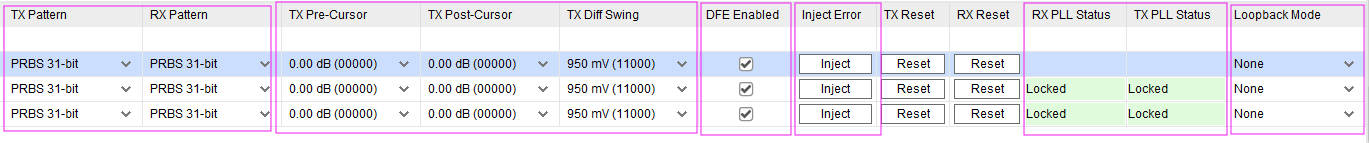

选择了两个收发器连接之后,可在vivado下端看到下图12所示的界面。

可以简单分为粉色框出的部分,在前文讲过,IBERT主要是用来测试收发器的信道质量的,对于传输质量不好容易产生码间串扰或是其他影响的信道可以通过这些设置来一定的改善。需要注意的是:

(1)Rx和Tx的PLL Status,如果显示locked即表示可以进行测试,如果显示其他则说明对应的参考时钟设置或参考时钟的管脚约束有问题,可以重新设置;

(2)Loopback Mode主要有四种模式,分为近端、远端的PCS和近端、远端PMA回环,如果选择其中一种回环方式则其在对应的位置回环了,如果选择none,则Tx端的码流将会输出,根据自行外部连接线在输入到Rx端去,这里采用外部连接故选择none,选择外部连接一定要注意连接线是否合适;

(3)Tx 的Pre-cursor、Post-cursor和Diff Swing就是收发器的Tx发送端的预加重等可以改善信号传输质量的一下参数,可以修改这些参数获取最优质量,而DFE Enable是收发器的Rx接收端的均衡器的使能信号,勾选有利补偿信号在信道传输中的损失;

(4)Tx和Rx pattern是测试时的伪随机码,接收端可以校验发送端发送的数据是否正确的来计算误码率,故需要Tx和Rx的伪随机码一致,这里可以选择PRBS 31-bit;

(5)Inject Error可以在测试过程中机型注入错误,可以模拟真实情况下有可能遇到的各种影响;

(6)在以上的每种操作后记得要reset下。

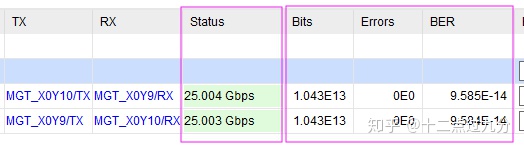

当设置好上述的参数或者其他设置之后就可以观察收发情况,情况如下图13所示,可以看到KCU116的收发器情况良好,但是如果是自己设计的一些高速板可能状况就不大好了,但也可以设置一些参数稍加改善。

- 眼图

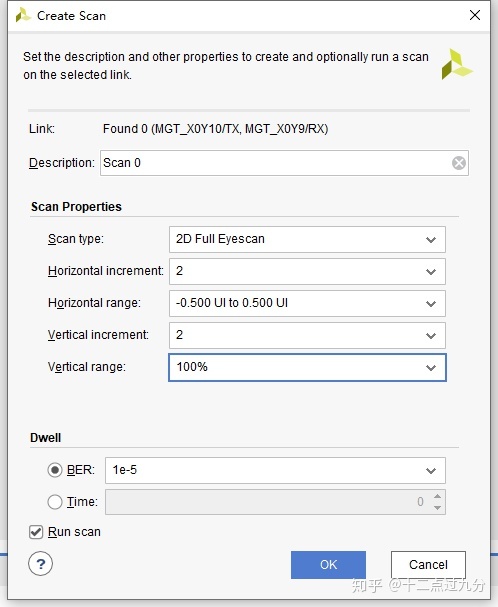

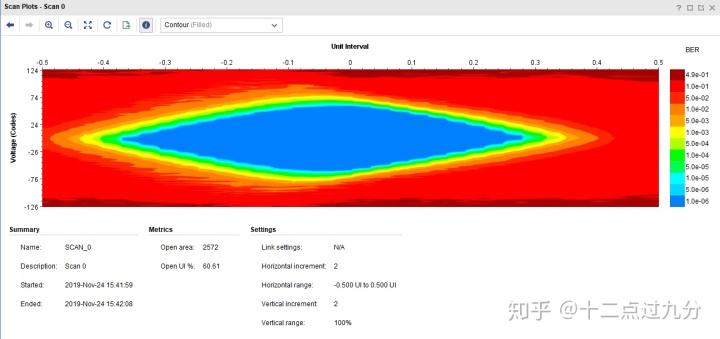

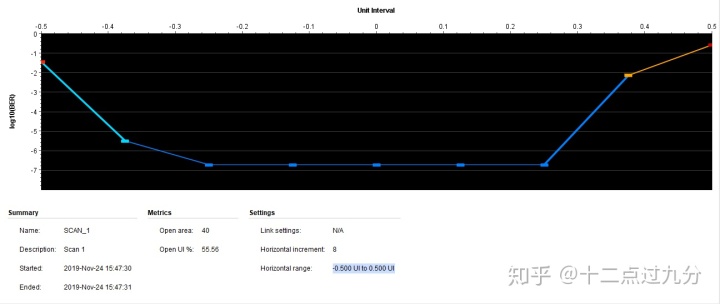

除了以上的使用方式外,还可以观察收发器的眼图情况,如下图14、图15所示,可以设置范围、误码率阈值等。

简单设置后,就可以得到眼图了,如下图16所示,观察眼图无非就是看该图长得是否像眼睛以及张开的面积是否大,如果张开的面积越大说明信道质量越好,这样一来就很轻松地可以判断设计的高速接口的质量了。

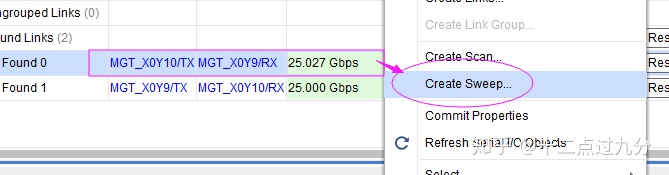

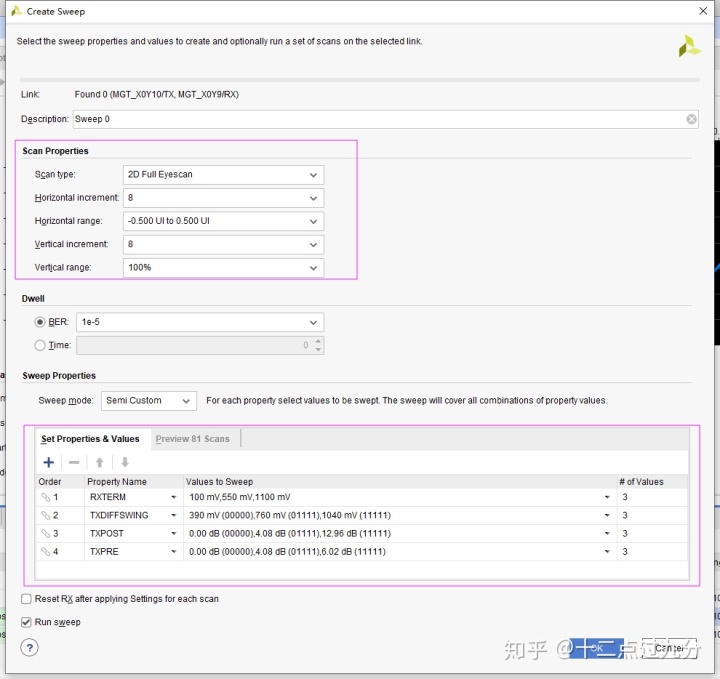

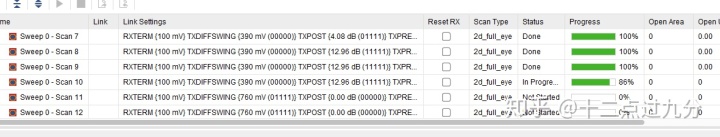

除了这样单次查看眼图判断信道质量,还可以设置多组不同的预加重参数生成眼图的方式,这样就可以获取最佳预加重参数,这样一来在此后的接口设计当中就可以使用到这样的一组参数,以此提供信号传输的质量。具体如图17、18、19所示

从这么多组参数排列组合得到眼图中选取眼睛张开面积最大的那张图所对应的参数就是最优参数了,当然有的是时间的话可以将所有情况都排列组合一遍。

- 浴缸曲线

除了观察眼图之外还可以观察浴缸曲线,只要把图15的扫描类型换成1D Bathtub就可以得到下图20所示。

- 其他

如果你恰巧财力雄厚,还可以买两块KCU116的板子,这样一来,在两个收发器连接中也可以选择使用两块板子的GTY收发器对连。我经过两块板子对连发现,只要两块板子的码流速率和码型一致就可以连接测试,这样一来就使用这个工具去测试一些误码仪的功能(这个我实际测试发现是可行的)。

其他的想到之后再做补充了~

写在最后:

接下来有时间有机会简单介绍一下怎么使用一些高速接口,像是10G/25G以太网、PCIE等接口的IP的使用,当然行文介绍也会像这篇文章一样尽可能简单,易于上手!

当然,作为一个刚开始学习FPGA的新手,我也只能从我这个新手的角度出发去学习这些工具或者IP的使用,可能在很多地方还是认识不足或是学习不充分,会存在错误,欢迎批评指正~