热门标签

热门文章

- 1为什么输入法显示中文打不出中文_电脑的输入法有时候打不出中文为什么?

- 2入门指南:使用Spark MLlib进行数据处理和机器学习_spark mllib 教程

- 3Mac切换到root用户(su命令行),以及退出。_mac退出root

- 4uniapp自定义富文本编辑器+内容渲染回显功能(多端可用)_uniapp 富文本

- 5【嵌入式】Libmodbus源码分析(五)-TCP相关函数分析_libmodbus5

- 6网络安全应急响应(归纳)_安全事件id 应急响应

- 7git stash 的用法_got stash list

- 8最新Node.js安装及配置详细教程_nodejs

- 9CSV:简单格式下隐藏的那些坑_csv文件的编码格式有什么影响

- 10nuxt初学之创建nuxt项目_nuxt创建步骤

当前位置: article > 正文

AD9361_FPGA的PL端纯逻辑(verilog)配置AD9361(六)_实现2FSK信号的数字调制_通过fgpa配置9361

作者:小舞很执着 | 2024-07-29 22:02:32

赞

踩

通过fgpa配置9361

本博客的工程源码文件下载:百度网盘 (点击蓝色“百度网盘”文字即可下载)提取码:mww7

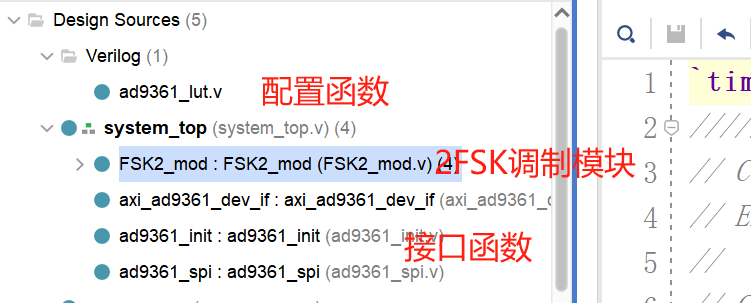

1.工程组成

本次博客利用AD9361实现2FSK数字调制,并进行了测试,整个工程包括AD9361接口程序、配置程序和2FSK调制程序,工程结构如下图所示:

2.2FSK调制

对于FSK信号,不管是2FSK、4FSK还是8FSK,均采用IQ正交调制方法,框图和前面博客QPSK调制框图基本一致,这里就不在画了,重点是设计频差时注意和码速率之间的关系(在工程中进行了标注),才能保证在解调时能够正确完成。

3.2FSK测试

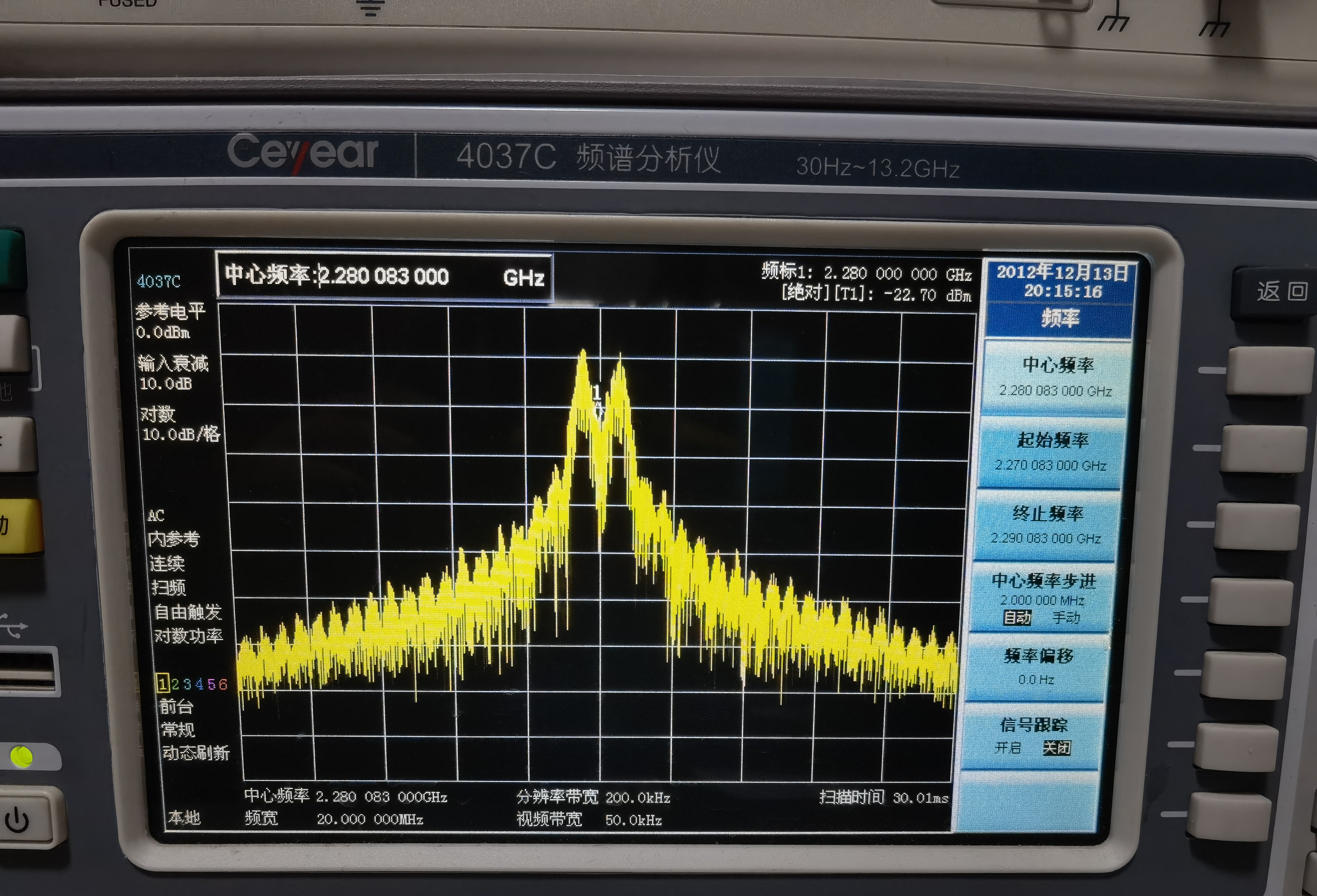

2FSK信号可以直接利用频谱仪观测频点是不是和设计的一致,通过最大保持测量偏差是不是符合设计要求。

频谱仪动态观测2FSK频谱图如下:

最大保持如下:

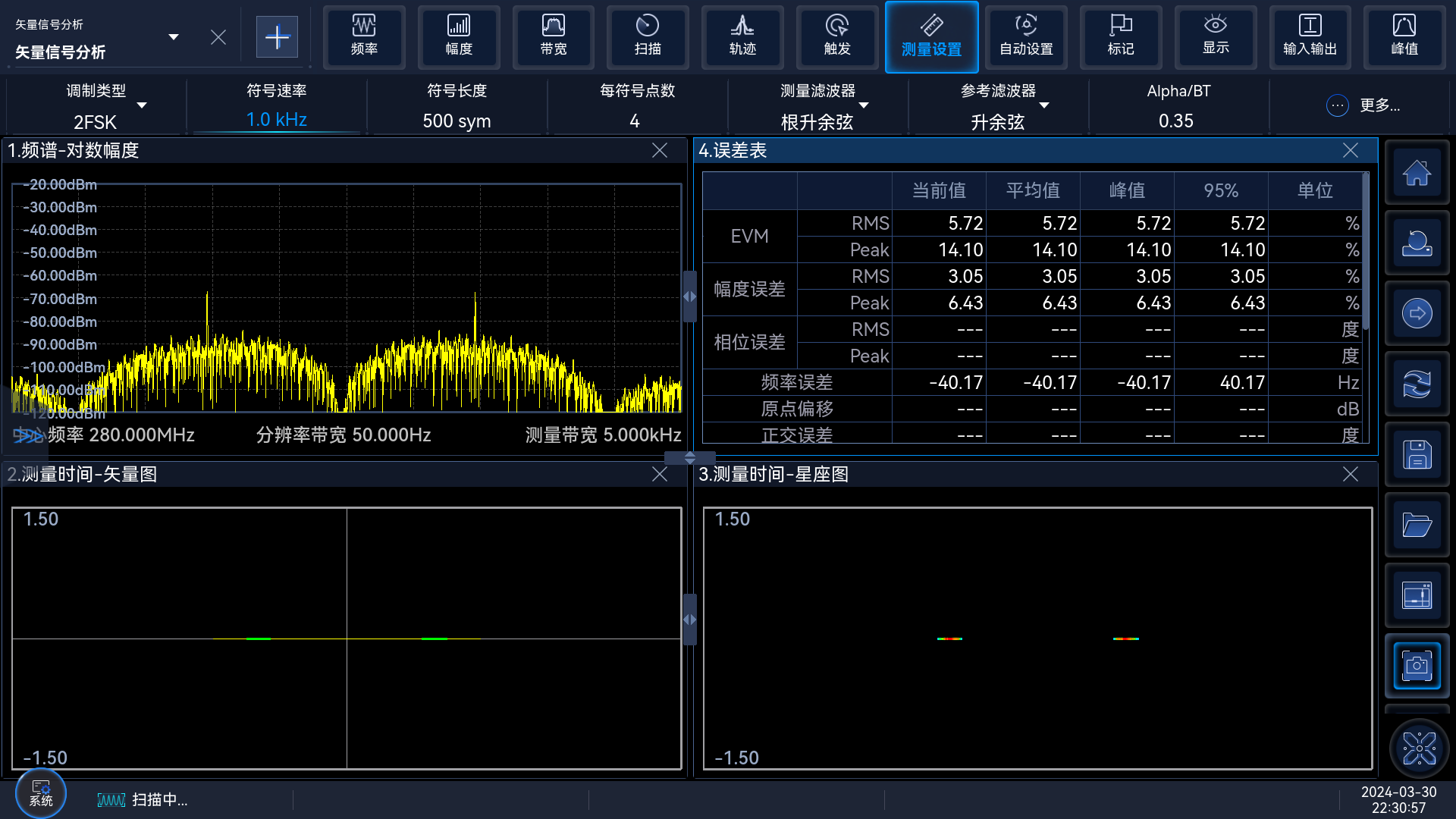

从频谱图上测量的结果符合设计要求,最后通过逻辑信号分析仪看下星坐图

从分析结果看符合要求,星座图清楚。

4.总结

对于数字信号调制,都采用IQ正交调制,包括MSK、QAM等其他调制均是如此,利用前面博客所写的接口函数和转换软件,将重点只关注调制信号本身设计,不用再考虑AD9361接口问题,将更多的经历关注到信号设计本身,对于AD9361的配置按照之前的博客配置非常简单。

5.参考博客

ZedBoard+AD9361_FPGA的PL端纯逻辑(verilog)配置控制9361(一)_初始化寄存器脚本文件生成_fpga控制ad9361-CSDN博客

ZedBoard+AD9361_FPGA的PL端纯逻辑(verilog)配置控制9361(二)_将寄存器脚本文件转换成Verilog函数_ad9361 .cfg转.v-CSDN博客

AD9361_FPGA的PL端纯逻辑(verilog)配置AD9361(五)_实现QPSK信号的数字调制_ad9361如何识别调制方式-CSDN博客

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小舞很执着/article/detail/900800

推荐阅读

相关标签