- 1java学习笔记:集合之一些练习题_java map

- 2图像分割与GAN网络_gan图像分割

- 3openmv串口发送数据_OpenMV串口发送图片

- 4删除数据库的外键_删除外键

- 5echarts树图的节点自定义图片,以及子节点挤在一起该怎么处理..._echarts树状图设置点的图形

- 6【超详细】HIVE 日期函数(当前日期、时间戳转换、前一天日期等)_hive當前時間

- 7Nginx详解(一篇让你深入认识Nginx)_ngix

- 8tryhackme

- 9穿越 java | 快速入门篇 - 第1节 计算机基础知识_java 开发涉及精简指令复杂指令

- 10如何在Wpf程序中使用MaterialDesign,实现mvvm,及封装常用的确认对话框、信息输入对话框、进度等待框_wpf material design

数字IC笔试千题解--单选题篇(二)_芯片中断引脚送出的中断信号一般采用脉冲信号

赞

踩

前言

出笔试题汇总,是为了总结秋招可能遇到的问题,做题不是目的,在做题的过程中发现自己的漏洞,巩固基础才是目的。

所有题目结果和解释由笔者给出,答案主观性较强,若有错误欢迎评论区指出,资料整理来自于“数字IC打工人”等数字IC相关公众号,牛客网等网站真题、网络笔试真题及面经抄录。

保持更新(2023.9.25)文章内含 单选题270道、多选题106道、填空题16道、判断题17道、简答题72道、逻辑推理题3道、C语言 python 脚本编程题8道。

在本文中笔者提供的所有代码,都写成了API,可直接copy到软件编译、运行、给出结果。

题目较多,即使有前人解析和强大的ChatGPT,也难免出错,若发现错误,欢迎评论区讨论。

另外夹带一点私货~: 这一刻,我感觉一定要给.....

数字IC笔试千题解总字数已到达15w+,网页码字卡顿情况严重,故将其分割成多个部分以方便维护,链接如下:

数字IC笔试千题解--单选题篇(一)

数字IC笔试千题解--单选题篇(二)

数字IC笔试千题解--多选题篇(三)

数字IC笔试千题解--填空题篇(四)

数字IC笔试千题解--判断题篇(五)

数字IC笔试千题解--简答题篇(六)

数字IC笔试千题解--逻辑推理篇(七)

数字IC笔试千题解--编程&&脚本篇(八)

单选题

201.为了保证代码以及验证活动的质量,通常要统计什么( )

A、仿真覆盖率及故障覆盖率

B、功能覆盖率及行覆盖率

C、代码覆盖率及功能覆盖率

D、逻辑覆盖率及反转覆盖率

答案:C。

202.高频时钟域的数据(每时钟周期都变化)传递给低频时钟域时,哪种同步方式正确?( )

A、使用握手信号进行同步

B、使用异步FIFO

C、使用同步FIFO

D、使用打2拍进行同步

答案:B。快时钟数据每周期都变化,就没法通过脉冲展宽让慢时钟抓到所有数据了,所以使用异步FIFO缓存数据。

203.己知一套串行编码规则如下,编码后的信号与前一个时钟编码前的电平相同表示为1,与前一个时钟编码前的电平不同表示为0.且不允许出现编码后连续6个时钟为相同电平(如果出现需要插入1个bit,该bit是将编码后信号进行一次取反)。假定编码后信号初始为低电平,则二进制序列01010011111110010编码后的二进制编码是( )

A、110010000011110110

B、110010000001111010

C、001000001111010100

D、以上都不对

答案:D这道题就按着题目规则来就行。写三个编码,前三个都是0就能选D了。

204.关于Verilog HDL中的数字,请找出以下数字中最大的一个( )。

A、8'b1111_1110

B、3'o276

C、3'd170

D、2'h3E

答案:A。有陷阱,只有A选项是8bit的。

205.下面代码描述的是一个什么样的电路?( )

-

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)

- a<=1'b0;

- else if(b>1'b0)

- a<=b;

- end

A、综合为Latch

B、带同步复位的D触发器

C、带异步复位的D触发器

D、组合逻辑

答案:C。

206.D触发器:Tsetup=3ns,Thold=1ns,Tck2q=1ns,该D触发器最大可运行时钟频率是( )

A、1GHZ

B、500MHZ

C、250MHZ

D、200MHZ

答案:C。让建立时间和保持时间都满足要求,Tcycle >= 4ns。这里Tck2q=1ns刚好等于Thold的大小,如果Thold改成2ns,就隐藏了一个Tlogic最小为1ns的陷阱,这题将会更好。

207.以下不能提高验证环境的可重用性的是( )

A、使用宏定义

B、使用绝对路径索引文件

C、使用factory进行重载

D、使用intertface进行连接

答案:B。使用绝对路径,换个环境就不行了,不利于重用。

208.组合逻辑电路的竞争冒险现象是由于( )引起的

A、电路存在延时

B、电路有多个输出

C、电路未达到最简

D、逻辑门类型不同

答案:A,竞争冒险是由于组合逻辑延时不同,到达逻辑门不同导致的毛刺问题。

209.关于Task与Function语句,以下不正确的是( )

A、在Function中,可以调用Task

B、Function至少有一个输入变量

C、function必须要有返回值

D、Task可以有返回值

答案:D。task不能有返回值。选项A:function可以调用不含延时的task函数。

210.数字电路设计中,下流哪些手段无法消除竞争冒险现象( )

A、增加冗余项消除逻辑冒险

B、降低时钟频率

C、增加选通信号,避开毛刺

D、加滤波电容,消除毛刺

答案:B。竞争冒险是组合逻辑的概念,和时钟无关。

211.关于代码覆盖率,描述正确的是( )

A、代码覆盖率不包括toggle覆盖率

B、代码覆盖率包括line覆盖率

C、代码覆盖率包括功能覆盖率

D、代码覆盖率达到100%,表示验证足够完备,可以停止验证

答案:B,代码覆盖率包括行覆盖率,也即下面所说的path coverage。

代码覆盖率主要包含:

-

行覆盖率(Line Coverage):指被执行到的代码行占总代码行数的比例。

-

分支覆盖率(Branch Coverage):指对于if语句、switch语句等分支结构,所有可能的执行路径被覆盖到的比例。

-

条件覆盖率(Condition Coverage):指所有可能的布尔表达式的取值都被覆盖到的比例。

-

路径覆盖率(Path Coverage):指对于代码中所有可能的路径,是否都被执行到的比例。

-

翻转覆盖率(toogle Coverage):翻转覆盖率衡量的是哪些单比特变量的值为0或1,表明代码中信号的0到1和1到0的翻转情况。

6.有限状态机覆盖率(FSM coverage):有限状态机覆盖率衡量的是状态机中哪些状态和状态转换已经被访问过。表明状态机中各个状态的覆盖情况。

212. UVM中以下描述不正确的是( )

A、connect_phase的执行是自上而下

B、reset_phase在main_phase之前执行

C、可以在build_phase进行objection的raise

D、build_phase的执行是自下而上

答案:A,D。(摘抄试卷是单选,但博主认为此题多选)

选项A错误,connect_phase的执行顺序是从下往上执行的,先执行driver和monitor的connect_phase,再执行agent的connnect_phase。

选项B,reset_phase是在build_phase之后,在main_phase之前执行的。

选项C,raise_objection方法可以在 build_phase 和 run_phase 中使用。

D选项错误,build_phase的执行顺序是从上往下执行的,先执行my_case的build_phase、在执行env、agent等;一层一层往下执行。

213.关于异步复位,描述错误的是( )

A、数字设计经常使用异步复位同步释放

B、异步复位可以节省资源

C、使用异步复位有利于进行时序分析

D、异步复位对毛刺很敏感,抗干扰能力差

答案:C。异步复位对毛刺敏感,尤其跨时钟域时需要对异步复位信号进行同步,不利于时序分析。

214.关于动态数组和队列,描述错误的是( )

A、动态数组需要调用delete函数释放空间

B、队列在扩大时,sv会自动分配空间

C、动态数组和动态队列实例化使用new[]

D、队列相关函数包括pop_front()、push_back()

答案:C。没有动态队列这种说法,队列不用new函数,用自带的pop_front和push_back函数。

215.有一个FIFO设计,输入时钟100MHz,输出时钟70MHz,输入数据模式固定,其中1000个时钟中有700个时钟写传输连续数据。为了避免FIFO下溢/上溢,FIFO最小深度是多少( )

A、360

B、1170

C、420

D、270

答案:C。读写速率一致,FIFO不会溢出。假设背靠背传输连续写入了1400个数据,此时读出了980个数据,FIFO最小深度为420。

216.芯片中有关GPIO的叙述,不正确的是( )

A、GPIO般只具有0态和1态,不具有高阻状态

B、GPIO的引脚一般是多功能复用的

C、GPIO作为输入接口时具有缓冲功能

D、GPIO作为输出接口时具有锁存功能

答案:A。

GPIO在某些情况下可以设置为高阻状态,如在输入模式下设置为输入使能和高阻。

217.下面关于AHB协议描述错误的是( )

A、Burst传输不能跨越1KB地址边界

B、HRESP[1:0]有OKAY、ERROR、SPLIT和RETRY

C、Burst传输包括single传输、定长传输和不定长传输

D、读写操作的地址相位只会维持1拍时钟

答案:D。如果总线在等待握手,地址还会继续维持,

218.下面哪个不属于跨时钟域数据传递的基本方法( )

A、信号通路上插入isolation

B、使用FIFO

C、使用多级触发器缓冲

D、使用握手协议

答案:A。选项A中提到的isolation在跨时钟域数据传递中通常用于解决异步复位/时钟等问题。当一个模块工作在一个时钟域中,而另一个模块工作在另一个时钟域中,而两个时钟域之间没有公共时钟信号时,会出现异步信号传输的问题。这时,可以在信号通路上插入isolation电路,用于隔离两个时钟域之间的信号,保证传输的正确性。

219.以下为文件后缀为某代工厂提供的库文件,合法的电压,环境温度范围内,以下哪种情况内部信号速度最快( )

A、SS_-40°C

B、FF_-40°C

C、SS_125°C

D、FF_125°C

答案:B,Fast corner。

220.以下Verilog运算符优先级由高到低正确的是( )

A、&,|,&&,^,!

B、^,!,&,|,&&

C、!,|,&,&&,^

D、!,&,^,|,&&

答案:D。

221.下面哪个phase属于task phase( )

A、connect phase

B、build phase

C、report_phase

D、reset phase

答案:D。

222.以下不能对多bit的数据总线的时钟异步处理的是( )

A、Gray-code

B、寄存器同步

C、FIFO

D、Dmux synchronizer

答案:B。寄存器同步不能同步多bit信号。

223.关于’uvm_do_on和’uvm_do_on_with,表述不正确的是( )

A、在使用之前对应的对象需要进行实例化

B、都有三个参数

C、第二个参数可以是virtual sequencer

D、第一个参数必须是transaction指针或者sequence指针

答案:B。

uvm_do_on用于显式地指定使用哪个sequencer发送此transaction。它有两个参数,第一个是transaction的指针,第二个是sequencer的指针。

uvm_do_on_with,它有三个参数,第一个参数是transaction的指针,第二个是sequencer的指针,第三个是约束:

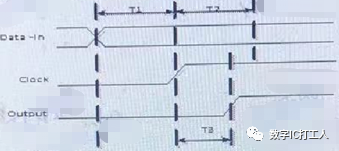

224.Which's setup timing check in right waveform?( )

A. T1

B. T2

C. T3

D. T1+T2

答案:A。setup time为数据到来之前需要保持的时间

225.Which stage of detecting a fault is at least cost to a company? ( )

A. Wafer

B. Packaged chip

C. Board

D. System

答案:D。在流片之前纠错成本最低。

226.Which of the following expressions is true?

A. a=4'df

B. C=3 'd8

C. B=5 'h1

D. d=3 'b2

答案:C。选项A,十进制没有f。选项B,3bit表示不到数字8。D选项,二进制没有2。

227.Which of the followings is not allowed to be in an interface class?( )

A. Pure virtual methods

B. Type declarations

C. Cover groups

D. Parameter declarations

答案:A。接口可以有参数、常量、变量、函数和任务。可以声明接口中元素的类型,也可以将类型作为参数传入。cover group可以在包、模块、程序、接口或类中定义。

228.Which of the following arrays need new constructor in system Verilog?

A. Multidimensional arrays

B. Dynamic arrays

C. Associative arrays

D. Queues

答案:B。动态数组的创建需要使用构造函数new函数。

229.Which one of the following items can't be considered to decrease the power of a design? ( )

A. use high Vt cells

B. increase clock frequency.

C. add clock gating

D. decrease voltage supply.

答案:B。使用高Vt的库,电流会变小,功耗降低。选项C,门控时钟,减小功耗。

230.The time required for an input data to settle________ the triggering edge of clock is known as “Setup Time”. ( )

A. Before

B. During

C. After

D. All of the above

答案:A。setup time定义,在时钟上升沿到来之前,数据需要保持不变的时间。

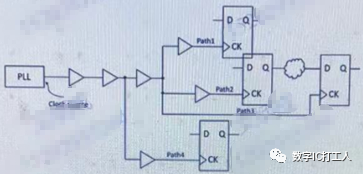

231.Which equation compute the local skew in below circuit? ( )

A. Path1-Path2

B. Path3-Path2

C. Path3-Path1

D. Path4-Path2

答案:B。skew分为global skew和local skew。这里的local skew是指design 中两个相关寄存器 latency 之差的最大值。

参考博客:一网打尽时钟树综合Clock Skew_IC拓荒者的博客-CSDN博客

232.Which of the following is having highest priority at final stage (post routed) of the design?

A. Setup violation

B. Hold violation

C. Skew

D. None

答案:B。hold violation是最难修复的,所以具有最高优先级。

233.Which of the following tools can be used for timing tape out sign-off? ( )

A. Modelsim

B. Primetime

C. Redhawk

D. Design compiler

答案:B。

Modelsim:Mentor公司的RTL仿真工具。

PrimeTime: PrimeTime(PT)是Synopsys的sign-off quality的静态时序分析工具。

Redhawk: Synopsys 集成RedHawk分析融合技术的 IC Compiler II 在设计者的流程中引入了电源完整性分析和修复功能,提供了在物理设计步骤中的签核精度结果。

Design compiler: Synopsys 逻辑综合工具。

234.下列不属于嵌入式设计处理器本身带有的基本接口是( )

A.串口

B. PCIE

C.并口

D.AD/DA

答案:B。嵌入式设计处理器本身带有的基本接口包括串口(UART)、并口(SDIO)和AD/DA等模拟接口,但不包括PCIE接口。

235.已知下左图中施密特触发器为右图中所示电路,电源电压是10V, R1=10KΩ,R2=20KΩ,该多谐振荡器中的电路参数VDD=10V,R=10kΩ,C=0.01uF,则该电路的振荡周期是( )

A. 0.2197ms

B. 0.4297ms

C. 0.1099ms

D. 0.3296ms

答案:不会做,留一手。

236.In Linux system, which of following commands can be used to mount a U-disk to the system()

A. mount /dev/hda /mnt/udisk

B. mount /dev/sdb1 /mnt/udisk

C. mount /dev/fd0 /mnt/udisk

D. umount -n /mnt/udisk

答案:B。

mount命令用于挂载Linux系统外的文件。

hda一般是指IDE接口的硬盘。

第一个硬盘名为/dev/sda,第二块硬盘命名为/dev/sdb,以此类推。sdb1则表示这块硬盘的分区1。

fd表示软盘驱动器。

umount可卸除目前挂在Linux目录中的文件系统。

237.In amplification mode, which of the following is correct for this transistor?()

A. VC>VB>VE

B.VC<VB<VE

C.VB<VC<VE

D. VB>VC>VE

答案:B。

箭头是PN结的方向,由P指向N。

这是一个PNP型晶体管

晶体管发射区掺杂浓度高,基区很薄且掺杂浓度很低。集电区面积大。

晶体管在放大状态时,发射结正向偏置而集电结反向偏置。所以VE>VB>VC。

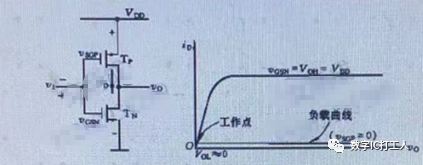

238.The following figure shows the CMOS inverter circuit, which is composed of two enhanced MOSFET, one N-channel structure, the other is P-channel structure. Which of the following conditions is necessary to make the circuit function?()

A. VDD= (VTN-|VTP|)

B. VDD> (VTN+|VTP|)

C. VDD < VTN+|VTP|)

D. VDD= (VTN+|VTP|)

答案:B。电源电压 VDD 大于两个管的开启电压的绝对值之和。

239.The main performance indexes of computer network are? ( )

A. rate

B. bandwidth

C. handling capacity

D. delay

E. use ratio

F. packet loss probability

答案:ABCDEF。

计算机网络的性能指标如下:

-

速率rate

-

带宽bandwidth

-

吞吐量throughput

-

时延delay/latency

-

时延带宽积

-

往返时间Round-Trip Time,RTT

-

利用率

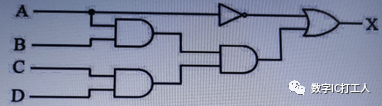

240.如下图的逻辑电路,其逻辑表达式为:( )

A. X=A'B+CD'

B. X=B+A'CD

C. X=A'B+CD

D. X=A'+BCD

答案:卡诺图化简。X =ABCD+A' =BCD+A'。

241.布尔代数(A+C) (A+B+C) 等于( )

A. A+BC

B. A+C

C.AB+BC

D.A+B+C

答案:B。(A+C) (A+B+C) =A+C+AC+AB+BC+AC=A+C

242.十进制数46的格雷码是哪个?( )

A.100011

B.101110

C.111001

D.111110

答案:C。

先写出46(D)的二进制:101110(B)。

二进制转换格雷码机制:格雷码的最高位和二进制的最高位是一样的,格雷码的其他位可以用二进制对应位和相邻高位的异或得到,即

assign gray_value[ i ] = binary_value[ i ] ^ binary_value[ i + 1 ];

格雷码为:111001,选C。

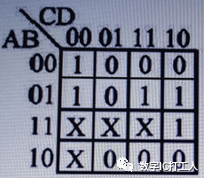

243.X表示任意项,如图所示卡诺图,求化简后的逻辑表达式( )

A. AB+BC

B. BC+C'D'

C. B+C'D

D. AB+B'C'

答案:B。看卡诺图可以直接给出结果:C'D'+BC

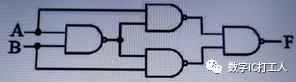

244.如图所示电路为下列哪种组合逻辑电路( )

A.NAND

B.NOR

C.AND

D.XOR

答案:D。

F=(((AB)'A)'((AB)'B)')',分别计算((AB)'A)'=A'+B。((AB)'B)'=B'+A。所以F=((A'+B)(B'+A))'。

(A'+B)(B'+A)=A'B'+AB,再取反,F=(A'B'+AB)',是异或。

245.如图所示逻辑电路,其中FA为全加器,LG为单个逻辑门,若F=0时,输出为X3X2X1X0+Y3Y2Y1Y0;F=1时,输出为X3X2X1X0-Y3Y2Y1Y0,则LG应为:( )

A.OR

B.NOR

C.NAND

D.XOR

答案:D。特殊值法,只看最低位。

F=0时,Z0=X0+F+B=X0+Y0。即F=0时,B=Y0

F =1时,Z0=X0+F+B=X0+1+B=X0-Y0。即F=1时,B=-Y0-1。

当LG为异或门时,满足第一条也满足第二条。

第二条有:Z0=X0+F+B=Z0=X0+1+Y0'=X0+1+1-Y0=X0-Y0。这里1+1进位。

246.如图所示逻辑电路,A/B/C/D四个输入共有几种组合会让Y输出为1?( )

A.6

B.7

C.8

D.9

答案:A。

这种题需要把Y表达式用最小项写出来,然后看有几个最小项,就用几种组合令Y为1。

Y=AB异或(C+D)'=AB异或C'D'。

A异或B=A'B+AB'。

所以Y=AB异或C'D'=(AB)'C'D'+AB(C+D)=(A'+B')C'D'+ABC+ABD=A'C'D'+B'C'D'+ABC+ABD。

Y=A'(B+B')C'D'+(A+A')B'C'D'+ABC(D+D')+AB(C+C')D

=A'BC'D'+A'B'C'D'+AB'C'D'+ABCD+ABCD'+ABC'D。

六种,选A。

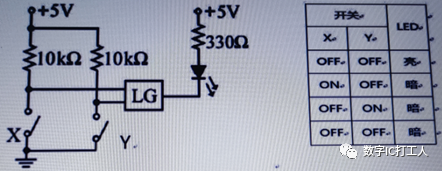

247.如图所示电路,LG为哪种逻辑门电路,才可以得到如表的实验结果?( )

A.AND

B.NOR

C.NAND

D.XOR

答案:C。

题目有误,第一行和最后一行都是OFF。假设最后一行为ON ON 暗。

那真值表就是:

| 1 | 1 | 0 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 1 | 1 |

与非门,选C。

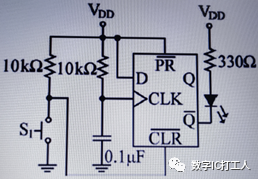

248.如图所示电路,其中D触发器的PR、CLR为0有效,若VDD开启前电容已完全放电,则下列叙述正确的是( )

A.电源开启后,LED亮,按下S1放开后,LED暗,之后再按下S1时,LED没有变化

B.电源开启后,LED亮,按下S1放开后,LED开始闪烁,再次按下S1则停止闪烁,LED灭,重复以上动作

C.电源开启后,LED暗,按住S1按钮时,LED亮,放开S1则LED灭,重复以上动作

D.电源开启后,LED暗,按住S1按钮时,LED闪烁,放开S1则LED灭,之后再按S1时,LED没有变化

答案:电源开启,CLK收到上升沿,把D端送到Q端,Q'为0,LED为亮。按下S1,异步复位,Q'为高,LED灭。之后再按S1就没用了,因为没有CLK时钟沿把D端数据送到Q端。

PRN是异步置位,可以将输出Q置为输入D(输出Q立马变成输入D)

CLRN(CLR)是异步复位,将输出Q置0。

249.有一个4位计数器,可计数范围为0~9,若输入时钟频率为1MHz,请问最高位的输出频率与正脉冲的宽度为多少?( )

A.输出频率100kHz,正脉冲宽度为2us

B.输出频率100kHz,正脉冲宽度为5us

C.输出频率500kHz,正脉冲宽度为2us

D.输出频率500kHz,正脉冲宽度为8us

答案:A。输出频率是1MHz的1/10=100kHz。正脉冲宽度为2个周期,2us.

250.Single Choice: Given the following FIFO and rules, how deep does the FIFO need to be to prevent underflow or overflow?

RULES:

clk_A=25MHz;

clk_B=100MHz;

en_B is periodically asserted: period is 4us, dutycycle is 25%

Pick ONE option

A. 100 entries

B. 75 entries

C. FIFO will overflow anyway

D. 10 entries

答案:B。en_B是一个占空比25%的信号,这样读写速率刚好相同,FIFO不会溢出。clk_A周期为40ns,clk_B周期为10ns。en_B周期为4000ns,其中有1000ns为高,3000ns为低。假设A为写时钟,B为读时钟。在en_B为低的3000ns里,A狂写,3000/40=75,之后1000ns,读的速度比写的快。选B。

251.当一个乘法器需要10个cycle才能完成计算任务,对其需要设置multicycle,setup会设置为10,hold设置为()

A、9

B、不需要设置

C、10

D、1

答案: A。在多周期设置中,Setup的周期是X,设置Hold周期为X-1。multicycle path:当FF之间的组合逻辑delay大于一个时钟cycle时,这条combinational path能被称为multicycle path;多数的design中,一个N multicycle setup应该与一个N-1 multicycle hold相对应,以保证hold check维持在同一时钟,否则极容易slack violated。

252.亚稳态状态是必须避免的,亚稳态现象可以导致如下后果( )

A.降低系统可靠性

B.其它都是

C.功耗损失

D.引起芯片失败

答案:B。

253.假设输入信号X位宽为10bit,InputA位宽为5bit,InputB位宽为14bit,实现Y=X*Input A+ Input B功能,并要求不损失精度,那么输出信号Y位宽应不小于( )

A.16bit

B.29bit

C.15 bit

D.24bit

答案:A。可以直接代特殊值,全一带入。10'b11_1111_1111*5'b1_1111+14'b11_1111_1111_1111

254.在SystemVerilog中,下列哪个数组在使用中会用到new操作( )

A.多维数组

B.动态数组

C.联合数组

D.压缩数组

答案: 动态数组(dynamic array)是在SystemVerilog中使用new操作的唯一数组类型。它的大小可以在运行时进行调整,可以根据需要增加或删除元素。使用动态数组时,可以使用new操作动态地分配数组的内存空间,并使用delete操作释放内存空间。

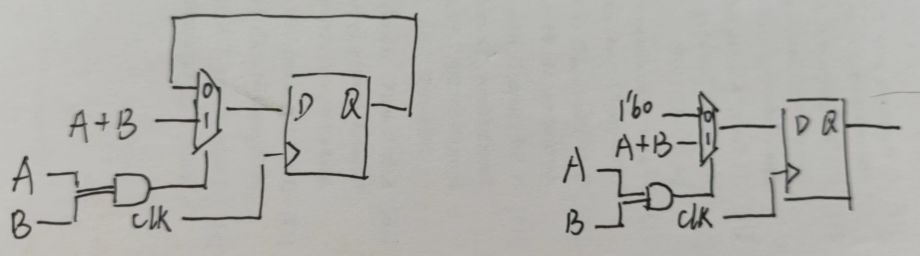

255.从综合出电路的看第一段代码比第二段代码优化的地方是

第一段代码:

-

- always @(posedge ck clk or negedge rst_n) begin

- if(~rst_n)

- D <= 1b0;

- else if(A & B)

- D <= A+B;

- end

第二段代码:

-

- always @(posedge clk or negedge rst_n)begin

- if(~rst_n)

- D <= 1'b0;

- else if(A & B)

- D <= A+B;

- else

- D <= 1'b0;

- end

A第一段代码比第二段代码简练,方便综合;

B.第一段代码比第二段代码省功耗;

C.第一段代码比第二段代码的电路简单;

D.第一段代码比第二段代码易于理解和实现;

答案:C。左边为第一段代码综合出来的电路,会比右边第二段代码综合出来的电路简洁一些,少一个1'b0的逻辑输入。不影响功耗。

256.以下不能抑制异步电路问题的是

A寄存三拍

B.双向握手

C.格雷码转换

D.缓存输出

答案:D。

257.亚稳态对电路影响极大,下面哪种做法对降低亚稳态发生概率是无效的

A增加异步处理的打拍级数

B使用专用亚稳态寄存器进行替换异步处理逻辑

C.提高异步处理电路的工作时钟

D.缩短异步处理打拍逻辑之间的delay

答案:C。提高时钟频率会让亚稳态更容易发生。

258.bufif0 # (5:7:9, 8:10:12, 15:18:21)b1 (lo1.1o2, dir).其中第一个5:7:9表示什么

A min typ max

B. rise fall turn-off

答案:A。

-

当给定三个延时值:

-

第一个延时值用于转变为1的情况(上升沿延时)

-

第二个延时值用于转变为0的情况(下降沿延时)

-

第三个延时值用于转变为高阻态的情况。

参考博客:Verilog 延时模型_verilog延时模块_lu-ming.xyz的博客-CSDN博客

259.在时钟上升沿时采样别start有效开始,两个时钟周期后,信号“a”连续或者间断地出现3次为高电平,紧接着信号“stop”在下一个时钟周期为高电平,转换成断言描述。以下哪个是正确的( )

A. property p0:

@(posedge clk) $rose (start)1 ##2 (a[=>3]) ##1 stop

endpropery

a0 assert property(p0).

B. property p0:

@(posedge clk) $rose(start)|-> ## 2 (a[*3]) ##1 stop.

endproperty

a0 assert property(p0):

C property p0:

@(posedge clk) $rose(star)|-> ##2 (a[=>3]) ##1 stop;

endproperty

a0: assert property(p0),

D. property p0:

@(posedge clk) $rose(start) |-> ##2 (a[=3]) ##1 stop,

endproperty

a0: assert property(p0);

答案:

260.对于FPGA内部的RAM而言,以下哪个说法是错误的?

A配置成伪双端口RAM时,两个端口均有各自独立的读写控制信号

B.配置成伪双端口RAM时,两个端口,可以使用不同的时钟

C.配置成单端口RAM时,仅有一个时钟,用于读操作和写操作

D.配置成单端口RAM时,仅有一组访问地址,用于读操作或写操作

答案:A。

伪双口 RAM 有两个时钟(clka & clkb)、一组输入输出数据线(dina & doutb)、两组地址线(addra & addrb),两个使能端(ena & enb)、一个写使能端(wea)。一个端口只读(Port a),另一个端口只写(Port b)。整体上,读、写可以同时进行。

真双口 RAM 有两个时钟(clka & clkb)、两组输入输出数据线(dina & douta & dinb & doutb)、两组地址线(addra & addrb),两个使能端(ena & enb)、两个写使能端(wea & web)。两个端口都可以进行读写操作(Port a 和 Port b 可以一起读或者一起写或者一个读一个写)。整体上,读、写可以同时进行。

261.关于静态时序分析(STA)哪项说法是错误的?

A. 不需要仿真向量

B. 不能验证设计的功能

C. 分析速度快

D. 可以分析同步路径和异步路径

答案:D。STA不能分析异步。通常异步下set false path。

262.关于下面约束,说法正确的是() constraint ST{ (a==0)-> (b==0) }

A如果a! =0,则b! =0

B如果b!=0,则a!=0

C.如果b==0,则a==0

D.如果a==0, 则b==0

答案:D。

对于给定的约束 ST { (a==0) -> (b==0) },它表示如果变量 a 的值等于 0,则变量 b 的值必须等于 0。换句话说,约束要求当 a 取 0 时,b 必须同时取 0。这个约束通常用于描述一些必要的条件关系,例如在某些情况下某些变量必须保持同步或满足特定的关系。

263.有关中断,以下说法不正确的是?

A.芯片中断引脚送出的中断信号一般采用脉冲信号

B.中断读清方式是指在CPU完成对中断指示寄存器的读操作后将中断指示寄存器清零。

C.中断存在边缘触发方式和电平触发方式

D.1根中断管脚可以过度多个芯片内部中断

答案:A。采用脉冲或者电平。

选项B,中断读清方式是指一种中断处理方式,其流程是先读取中断标志寄存器中的中断标志位,然后根据中断标志位来判断哪个中断被触发,执行相应的中断处理程序。处理完毕后,需要清除中断标志位,以便下一次中断请求的到来。这种方式可以有效避免中断重复触发的问题,提高系统的可靠性。

选项D ,一个中断管脚可以连接到多个芯片内部中断。这种情况下,当管脚上产生中断请求信号时,多个芯片都会被触发,产生中断请求。这个时候需要使用一种方式来区分这些中断请求,通常使用优先级编码器或者级联的方式来实现。

264.以下低功耗措施中,哪种不是降低电路翻转率的方法?

A重新安排“if-else”表达式,可将毛刺或快变化信号移至逻辑锥体的前部

B.采用Gray码或One-hot码作为状态机编码

C.在不进行算术运算的时候,使这些模块的输入保持不变,不让新的操作数进来.

D.减少电路中的glitch

答案:A。应该放在逻辑椎体的后部。

265.以下SV程序的运行结果为() :

-

- class Test;

- bit [31:0] addr;

- function void display_addr;

- $display("%h", addr);

- endfunction

- endclass:Test

- initial begin

- Test t1;

- t1 = new();

- t1.display_addr();

- end

A以上选项均不对

B.1.0

C. X

D.0.0

答案:D。SV new函数初始化默认赋值0.

266.以下信号命名中不符合Verilog语法的是: ( )

A. 1_2CorrectName

B. CNTO

C. _R1_D2

D. COunT

答案:A,变量不允许数字打头。

267.关于三段式状态机的描述,下列说法正确的是( )

A.输出必须是寄存器输出

B.描述状态转移条件和转移规律的逻辑是时序逻辑

C.描述状态转移时,可以不指定default态。

D.描述状态迁移的逻辑为时序逻辑

答案:A。

选项B,是组合逻辑。

选项C,需要指定default防止综合出latch。

选项D,组合逻辑。

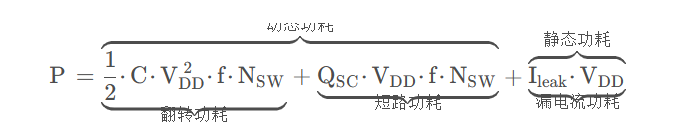

268.有关功耗,以下说法不正确的是?

A.设计层次越高,功耗优化所能达到的效果越好。

B.电压越大,工作频率越高,其动态功耗越高

C.低功耗设计的目标就是采用各种优化技术和方法,在各个设计目标之间找到最佳

D.芯片单位面积的动态功耗和静态功耗的随着工艺的发展呈下降趋势

答案:D。随着工艺的发展,芯片单位面积的静态功耗通常会下降,而动态功耗则会上升。这是因为随着工艺的发展,晶体管的尺寸不断缩小,导致静态功耗下降,但是晶体管的开关速度变快,频率也更高,导致动态功耗上升。

269.下列不属于动态数组内建函数的是( )

A. delete()

B. size()

C. new[]

D. length()

答案:D。delete删除动态数组,size返回动态数组长度,new给动态数组赋空间。

270.isolation cell是下面哪种低功耗技术必需的

A. Power Gating

B. Clock Gating

C. Mutli_Vdd

D. AVS

答案:A。isolation cell是Power Gating低功耗技术中必需的一种。Power Gating是通过控制芯片的电源来实现低功耗的技术,当某些部件不需要工作时,将其电源关闭,以达到降低功耗的目的。isolation cell作为一种关键的组成部分,负责在需要关闭电源时与该部件进行隔离,并确保其内部状态不会丢失。

271.reg signed [0:4]c ; c=8'sh8f; 赋值后c的值是多少?

A. 15

B. 17

C. -15

答案:A。将十六进制数 8f 转换为二进制为 1000_1111。'sh 是一个 SystemVerilog 中的数值表示方式,用于表示一个有符号数的十六进制值。其中's'表示有符号数(signed),'h'表示十六进制(hexadecimal)。

272.在Verilog中,"assign din[31:0]=32'hFF00_ABC4;assign dout[31:0]=(din<<2)>>4. dou的值是多少?

A 32'h00FF00AB

B.32'hFFFF00AB

C 32'h0x3FC02AF1

D.32'h0FC02AF1

答案:D。左移两位,再右移四位。

273.假设输入信号X位宽为12bit,InA位宽为6bit,InB位宽为17bit,实现Y=X*InA+InB功能,并要求不损失精度,那么输出信号Y位宽应不小于(所有数据均为有符号数) ( )

A. 12bit

B. 17bit

C. 19bit

D.18bit

答案:D。不考虑符号位进行计算,然后再加上符号位。

274.在Verilog设计中,下列说法不正确的是 ()

A.如果setup时间不满足,可以尝试降低时钟频率解决

B.在边沿敏感时序逻辑代码中,应使用非阻塞赋值(<=)

C.要求always块产生组合逻辑时使用阻塞赋值(=)

D.模运算符"%"是不可综合的

答案:D。取模运算可以综合。

275.下列verilog语句,哪个不能综合

-

- A.

- wire [3:0] in;

- reg out;

- always @(*) begin

- casez (in)

- 4'b1???:out=1'b1;

- 4'b01??:out=11b0;

- 4'b00??:out=1'bl;

- default: out = 1' b0;

- endcase

- end

- B.

- wire [7:0] a, b;

- reg [7:0]c;

- integer i;

- always@ (*) begin

- for (i=0; i<8; i=i+1) begin

- c[i]= a[i] &(|b[7: 7-i]);

- end

- end

- C.

- wire[31:0] in;

- wire [1 :0] sel;

- wire [ 7 :0] out;

- assign out = in[8*sel+:8] ;

- D.

- wire [7:0] in_1,in_2;

- reg [7:0] out;

- integer i;

- always@ (posedge clk) begin

- for (i=0; i<8; i=i+1) begin

- out[i]<=in_1[i]^in_2[i];

- end

- end

答案:C不可综合,下标索引不可为变量。

276.执行下面语句后,a,b的值为:

-

- reg[7:0]a, b;

- initial begin

- a=100;

- b=200;

- #10ns;

- a=10;

- #10ns;

- b<=a;

- end

- initial begin

- #20ns;

- b<=50;

- end

A. a=10,b=8 'hx;

B. a=10,b=50;

C. a=10,b=无法确定;

D. a=10,b=10;

答案:D。仿真出来的结果, 不知道为啥。

277.如果A和B是两个3bit的变量:A=3'b1×0 B=3'b1×0那么1)A==B 2)A===B的结果分别是?

A.1,0

B.x,1

C.0,x

D.0,1

答案:B。

参考博客:Verilog 逻辑与(&&)、按位与(&)、逻辑或(||)、按位或(|)、等于(==)、全等(===)的区别_verilog 逻辑与与按位与的区别_不吃葱的酸菜鱼的博客-CSDN博客

278.下面( )不是Verilog循环关键字

A. forever

B. repeat

C. while

D. force

答案:D。force可以在仿真时强制将某个信号变成某个值。

279.下面列出的SystemVerilog数据类型中,4值类型的是

A. int

B. time

C. byte

D. bit

答案:B。

280.7bits的自然二进制码 1011110对应的格雷码为

A. 1100011

B. 1100010

C. 1110001

D. 1011110

答案:C。格雷码公式,二进制最高位是格雷码最高位,然后格雷码某bit由二进制某bit与其高1bit的数的异或得到。

281.在C语言代码中定义了一个全局变量A,在编译器编译之后,A可能会出现在哪个段中?

A. Heap段

B. Bss段

C. Stack段

D. Text段

答案:B。

-

BSS段:BSS段(Block Started by Symbol)在程序开始执行之前,内核将BSS段中的数据初始化为0或NULL,BSS段中的变量默认都是0。BSS段是未初始化的全局变量和静态变量所在的段,例如:static int a; int b; 在BSS段中存储。

-

Data段:Data段存储已初始化的全局变量和静态变量,例如:static int a=1; int b=2; 在Data段中存储。

-

Heap段:Heap段通常用于存放动态分配的内存,例如:通过malloc函数分配的内存块等。

-

Stack段:Stack段通常用于存放局部变量、函数参数、返回值等。

282.验证过程中不能作为测试用例通过准则是

A. RTL代码

B. 协议或标准

C. 验证IP

D. 设计说明

答案:D。设计说明主要包含设计的概念、功能、接口等信息,通常不包含具体实现的细节,因此不能作为测试用例通过的准则。

283.根据下面的约束,哪一个选项是错误的?

-

- rand bit [7:0] a,b,c,d;

- constraint cst_abc {

- a inside {[50:100]};

- b>=a;

- c<a;

- c>10;

- d<=c;

- }

A. c可以取10-30之间的任意值

B. b可以取50-100之间的任意值

C. d可以取0-10之间的任意值

D. a可以取60-66之间的任意值

答案:B。

284.X,Y是两个无符号定点小数,X的位宽6bit,最低4bits是小数部分,最高2bits是整数部分;Y的位宽8bit,最低4bits 是小数部分,最高4bis是整数部分;现在需要计算X乘以Y的结果Z,即Z=X"Y,为了保证之的结果不溢出,Z的整数部分和小数部分至少需要多少个bit?

A. Z的整数部分至少7bits,小数部分至少7bits

B. Z的整数部分至少7bits,小数部分至少8bits

C. Z的整数部分至少6bits,小数部分至少9bits

D. Z的整数部分至少6bits,小数部分至少8bits

答案:D。

285. 在RTL设计阶段,降低功耗的常用设计方法是

A. 降低电路漏电流

B. 门控时钟

C. 多阈值电压

D. 门级电路的功耗优化

答案:B。在RTL设计阶段,能做的就是写门控时钟了。

286. 主板中噪声最大的电平是

A.3.3V

B.1.8V

C.12V

D.5V

答案:C。电压越大,噪声越大。

287.I2C信号线上添加上拉电阻的主要原因是()

A.提升驱动能力

B.提升响应速度

C.OPenDrain总线

D.限制电流

答案:C。接上拉电阻是因为I2C通信需要输出高电平的能力,OD架构没法输出高电平。

288.VIH、VIL、VOH、VOL是数字电路中常用的术语,表示逻辑门输入输出的电压水平,VIL具体指()

A.输出低电平

B.输入高电平

C.输入低电平

D.输出高电平

答案:C。输入低电平,Low-level Input Voltage。