热门标签

热门文章

- 1Markdown 之 UML图的实用画法_markdown uml

- 2头歌实验平台——树和二叉树试验_头歌educoder数据结构基于二叉链表的二叉树左右孩子的交换

- 3云计算探索-剖析虚拟化技术_虚拟化技术云计算虚拟化技术

- 4银河麒麟V10操作系统 创建分区、创建lvm逻辑卷、格式化、挂载_银河麒麟格式化硬盘

- 5牛客网算法教程-中级篇-第一章_牛客网算法题

- 6ESXI常用命令

- 7RuoYi-Vue-Plus (SpringCache、CacheManager、@Cacheable、缓存雪崩、击穿、穿透)

- 8【Go入门】Go语言基础知识

- 9探索生成式AI的未来:Chat与Agent的较量与融合_chatagent

- 10程序员的20大Git面试问题及答案_git面试题

当前位置: article > 正文

单片机的调试接口 JTAG SWD_jtck和jtms

作者:小蓝xlanll | 2024-04-29 00:17:40

赞

踩

jtck和jtms

JTAG-DP 和 SW-DP

DP?debug port

SW serial wire

PA13 JTMS SWDIO ------JTAG 模式选择引脚(JTMS)

PA14 JTCK SWCLK ------JTAG时钟引脚(JTCK)

PA15 JTDI ------JTAG 数据输入引脚(JTDI)

PB3 JTDO ------JTAG数据输出引脚(JTDO)

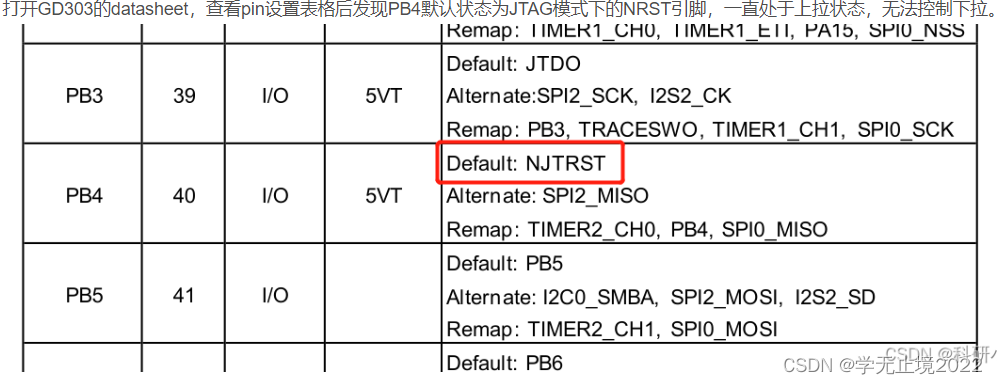

PB4 NJTRST ------JTAG复位引脚(NJTRST,低电平有效)

WD需要两根线,分别是SWDIO和SWCLK;

JTAG需要5根线,分别是JTMS、JTCK、JTDI、JTDO、NJTRST。

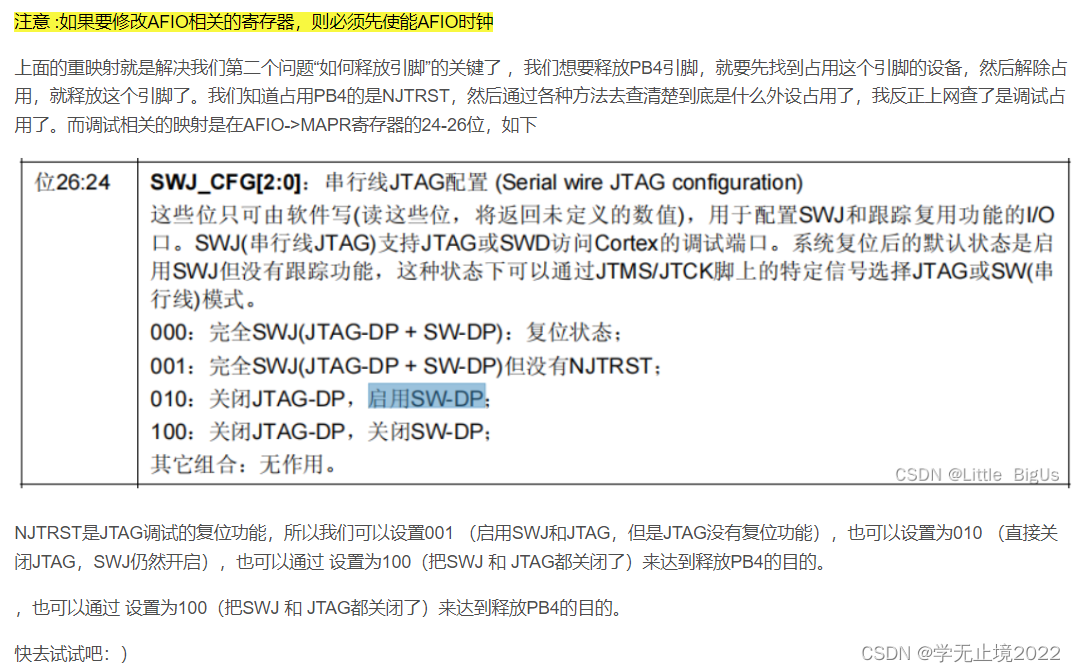

此处介绍用STLINK下载调试程序,在SWD调试方式时,PA15、PB3、PB4可以切换回普通的IO使用,但是要在程序中进行配置,不配置的话默认是不会为IO口的。

gpio_pin_remap_config(GPIO_SWJ_SWDPENABLE_REMAP, ENABLE);

GPIO_SWJ_SWDPENABLE_REMAP ==== JTAG-DP disabled and SW-DP enabled

GPIO_SWJ_DISABLE_REMAP ==== JTAG-DP disabled and SW-DP disabled

SWJ 指 SWDP和JTAGDP

NRST为系统复位引脚,N表示它是低电平复位。

本文内容由网友自发贡献,转载请注明出处:【wpsshop博客】

推荐阅读

相关标签