- 1保存GIT用户和密码,避免每次git push、git pull时都要输入用户名和密码_git保存用户名密码

- 2速盾:cdn真的抗打吗?

- 3COUNT函数的使用_数据库计数函数count怎么用

- 4IPhone手机只需十分钟即可从App Store申请退款,非常简单,附退款理由_苹果商店申请退款条件

- 5堆与二叉树的关系_堆事二叉树

- 62022面试,Java面试项目推荐,15个项目吃透两个offer拿到手软_java面试项目介绍案例

- 72024年(第十届)全国大学生统计建模大赛选题参考(二)_统计建模选题

- 8Q&A特辑 | 以万变钳制黑灰产之变的验证码产品设计逻辑的答案,都在这里_“防伪码”灰产链

- 9数据库时间字段TIMESTAMP和DATETIME区别_达梦 datetime和timestamp的区别

- 10Robust Real-time UAV Replanning Using Guided Gradient-based Optimization and Topological Paths_fast planner论文

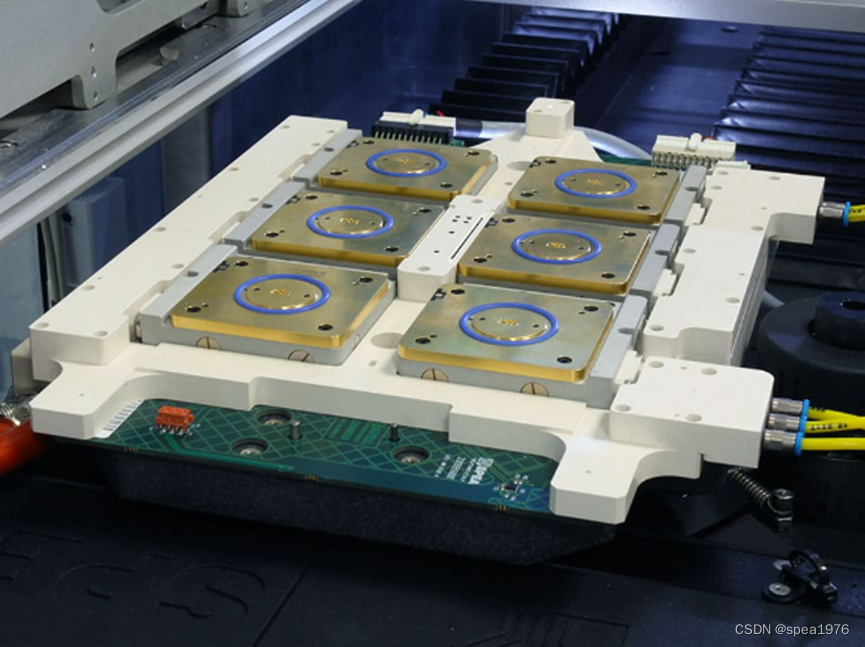

KGD测试设备方案简介

赞

踩

KGD的英文名称是Known Good Die,即合格芯片。SPEA拥有全球顶尖的把半导体测试技术,针对晶圆切割后彻底测试每个单独的裸片,SPEA开发了完整的测试设备和方案,可可满足 KGD 级别的高-低功率器件的静态和动态测试要求。SPEA的KGD测试方案包含参数测试、光学测试、切割晶圆的来往自动处理、器件接触和温度调节等多项内容。

KGD测试设备方案——高效裸片测试进一步提升良率

晶圆级别的裸片上所执行的参数测试并能发现所有缺陷,这是由于裸片接触裸片的界面可能会影响测试性能,无法达到功率元件所需的电压和电流额定值,无法执行所有必要的动态测量以确保器件性能符合数据表规格。

为辅助提升芯片良率,减少组装缺陷,SPEA专门开发了正对KGD的测试单元,这套解决方案可将完整的测试范围、精确度参数测试与大批量制造流程所要求的吞吐量和自动化结合起来,帮助厂家实现将本增效。

KGD测试功能特点

KGD 测试单元不仅可执行完整的直流参数测试,还可执行交流测试、UIS / UILAvalanche、RG / CG 和短路测试等。为执行验证器件开关参数的动态测试,测试设备能够同时用大电流和高电压调节被测器件。为防止因高功率耗散而可能造成的任何危险,测试单元配备了全方位的保护装置,包括过流和过压保护电路、输出继电器命令的电压监控器、开路/短路检查、触针保护。

ISO测试资源参数:

- 12kV/10mA DC

- 10kV/20mA AC

- 带有输出矩阵的高压安全开关可限制放电电流,确保测试仪在各种条件下安全运行

交流测试电源参数

- 最高达 6kV,最高达 3kA

- 短路测试最高达 10kA

- 最高达 8 个独立可编程的栅极驱动器

- 2 至 8个多脉冲

- 10GS/s 采样率数字化仪

直流测试电源参数

- 中等功率 V/I 电源(± 100V,± 2A,可组合高达 16A),带有 8 个驱动器和 8 个完全浮动且独立的数字化仪

- 高达 20kV 的高压发生器

- 高达 4kA 脉冲的大电流发生器,带有自动斜坡发生器,可缩短测试时间

寄生电感小于25nH、精确探测,无电弧

测试仪连接布局、接口和接触器的设计旨在最大限度地缩短被测器件和测试仪器之间的距离,并尽量降低整个信号路径上的杂散电感值。换流过程中电压过冲的可能性被降到最低,因为在任何情况下,可能的过电压值总是低于击穿电压。

测试室采用压缩空气调节大气,经专门设计,以抑制可能损坏器件和测试设备的任何电弧现象。为确保对单个裸片进行精确探测,基于世界一流的视觉对准,执行精细间距探针对准。探针系统在测试前自动对齐每个裸片,以消除其位置的 X、Y 轴和 Theta 旋转的任何变化。

拾取和放置分选设备

基于线性运动技术的集成取放头用于保证快速准确的处理。元件从晶圆(在蓝色胶带或 UV 胶带上)移动到测试室,在那里它们会被接触并进行全面测试。

测试后,合格的裸片可以放置在薄膜框架上,重新构成原始晶圆格式,或者在经过精确的光学检测后,可以将它们封装在卷带上。相同的机器配置可以灵活地用于两种输出选项,无需更改设置。

转塔式处理器

基于转塔的结构以紧凑的尺寸提供了极大的配置灵活性,以执行高速和高精度的测试、检查和精加工。

可以直接从薄膜框架晶圆上处理切割裸片,在重组后的晶圆上输出或在磁带上完成,使该解决方案成为 KGD 测试的理想选择。该处理器包括多个电气测试站(最多 10 个),具有热调节选项,可在特定温度下进行测试。

KGD测试系统-光学和几何测试:

在电气测试之前对器件的六个侧面进行光学检查,以验证组件的存在和位置,通过 ID 代码跟踪器件,并筛选出存在尺寸、外观或模具缺陷的元件。

在测试阶段也进行顶部和底部的视觉检查,以检查器件的存在和对齐,而准确的激光测量可让设备控制探测力和压缩。

测试后,可以在输出阶段进行进一步的完整光学检查。在带上精加工完成后,还会进行袋内检查和带封检查,以保证器件可以直接运送给客户,无需进一步检查。

KGD测试-温度调节:

通常需要温度测试,以检测受热变化影响的器件中的缺陷,或应用要求的测试条件,例如汽车标准的要求。

SPEA 测试单元采用灵活的无氮温度调节系统,可以在 -50 至 + 180°C 的温度范围内加热或冷却部件。每个站点的专用温度控制避免温度在不同被测器件之间散布,确保所有器件的测试条件一致。