热门标签

热门文章

- 1idea远程连接Docker调试 debug_idea docker 调试

- 2无人机集群作战仿真研究现状及在城市作战中的应用前景(附最新无人集群项目内容)_研究无人机作战的必要性和可行性

- 3【2023年电工杯数学建模竞赛B题人工智能对大学生学习影响的评价】完整思路分析+完整代码_人工智能对大学生学习影响的评价数学建模

- 4Idea之Java代码Remote JVM Debug_idea remote jvm debug

- 5【项目总结】基于SpringBoot+Ansj分词+正倒排索引的Java文档搜索引擎项目总结_springboot引入ansj统计词频

- 6【蓝桥杯计算思维题】少儿编程 蓝桥杯青少组计算思维真题及详细解析第5套_蓝桥杯小学组真题

- 7FPGA学习笔记_fpga16‘h什么意思

- 8计算机专业有哪些【含金量超高竞赛】?_计算机含金量高的比赛

- 9Devops系统化,从零开始学习容器技术(更新中)_系统学习容器化技术

- 10C++const成员函数/取地址运算符重载_const 版本的取地址运算符

当前位置: article > 正文

verilog实现4位计数器、Modelsim仿真、Chipscope调试以及下板子测试_quartus 4bit二进制计数器的仿真文件

作者:小蓝xlanll | 2024-05-22 10:38:35

赞

踩

quartus 4bit二进制计数器的仿真文件

工具:Quartus、Modelsim。

内容:用Verilog语言编写4位二进制计数器,并仿真、下载、通过逻辑分析仪在线调试。

(一)设计原理

设计4位寄存器,使用50M时钟,进行每个clk上升沿加一,完成每次计数0~15,计数器计数到15后,在时序逻辑中下一个clk计数器就归0。

(二)下板子注意事项

由于开发板的工作频率为50Mhz,因此在观察实际上板情况和逻辑分析仪采集结果时,需要加入分频模块。预设寄存器对原时钟信号计数,当记录到预设的值时,寄存器清零并翻转输出信号,由此得到频率较低的时钟。

50Mhz,周期为20ns

4位计数器的的最大值为15。

(三)模块代码

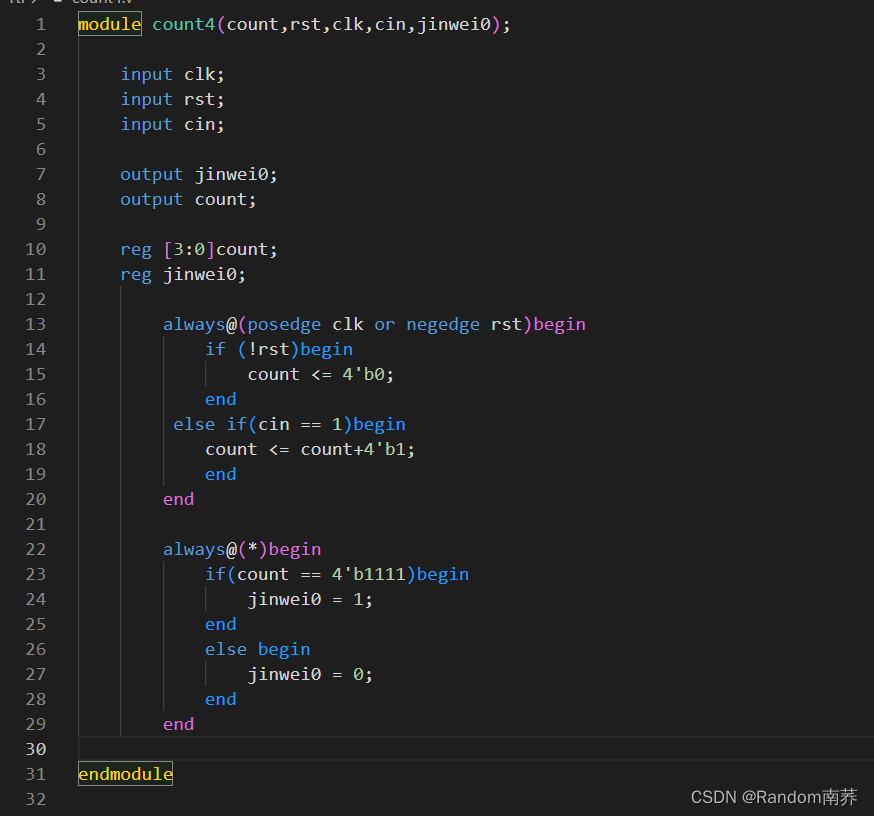

(1)4位计数器

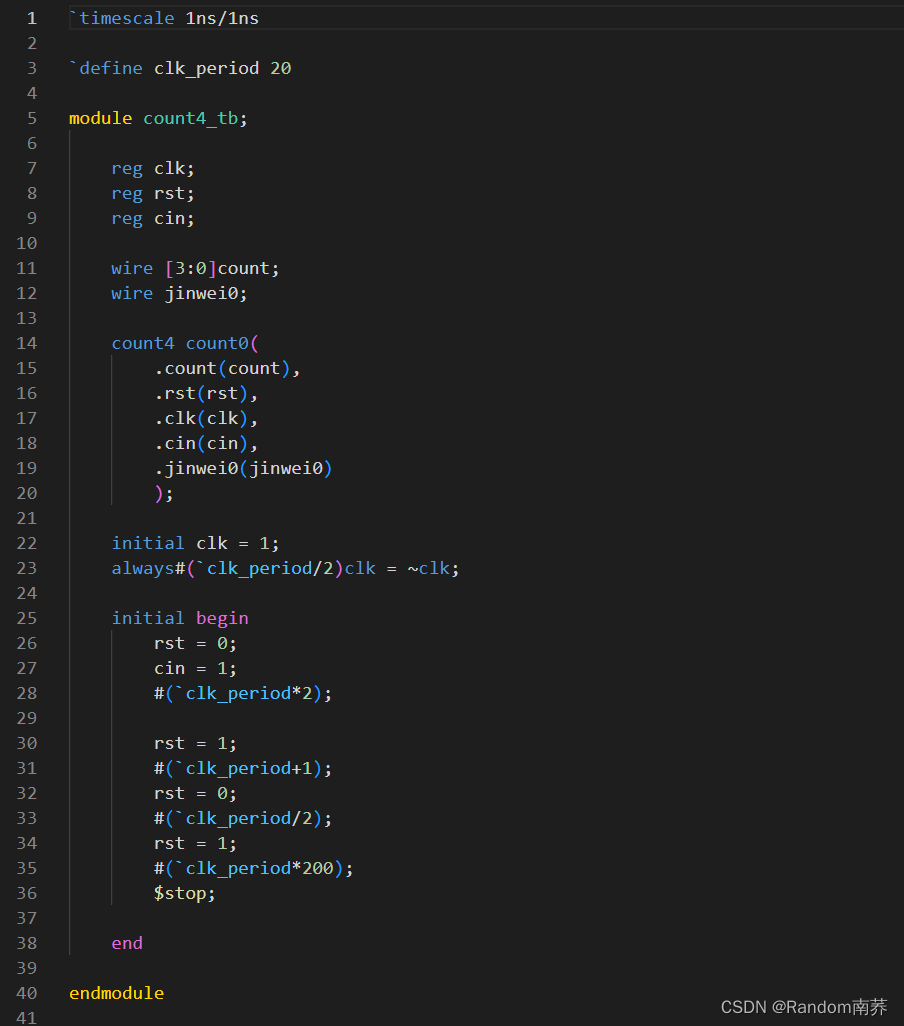

(2)4位计数器仿真tb

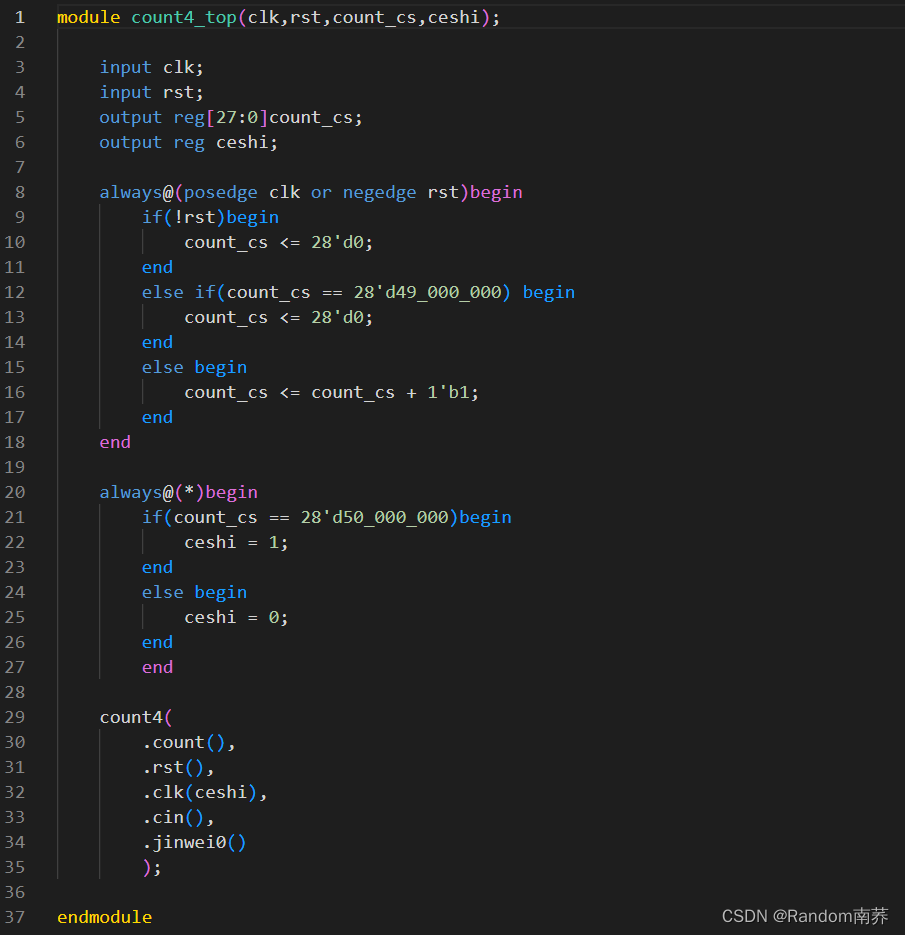

(3)4位计数器下板子

(4)Modelsim仿真图

(5)Chipscope调试图

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小蓝xlanll/article/detail/607830

推荐阅读

相关标签