- 1Unity ML-agents 参数设置解明_ml-agent configuration参数含义

- 2Anaconda环境下OpenCV的三种安装方法_opencv安装教程anaconda

- 3Scrum敏捷项目管理_在spring planing 会议上scrummaster说:我来安排一下,需求a有张同学负责,需

- 4vivado工程板级调试调用ISE的chipscope软件查看波形_chipscope中设置观察模拟波形

- 501-IDEA使用技巧_idea查询todo

- 6hive on spark

- 7unity渲染篇:画面亮度、饱和度、对比度调整_unity怎么修改饱和度

- 8core-js介绍及安装使用_corejs

- 9postman前置脚本加密(java script)_postman sm3

- 10【Linux网络编程】传输层中的TCP和UDP(TCP篇)

NPU架构分析与应用_手戳一个npu

赞

踩

NPU架构分析与应用

参考文献链接

https://mp.weixin.qq.com/s/62P8zVF7rySLakZJEkd7VA

https://mp.weixin.qq.com/s/hvzwCxzlgfS1yE-PRfs58A

https://mp.weixin.qq.com/s/BKzNwfVe-Bsoh_2090HHcQ

https://mp.weixin.qq.com/s/tEvskB3kIyA0t6a3z3zDhg

https://mp.weixin.qq.com/s/U2TIcwrq75FthslLgNJr2A

https://mp.weixin.qq.com/s/JVXSK_gr49IkRfl0s9UClQ

https://mp.weixin.qq.com/s/u_kBc5yoPJxtiovQD2EbWw

ADS算力芯片NPU的硬件架构

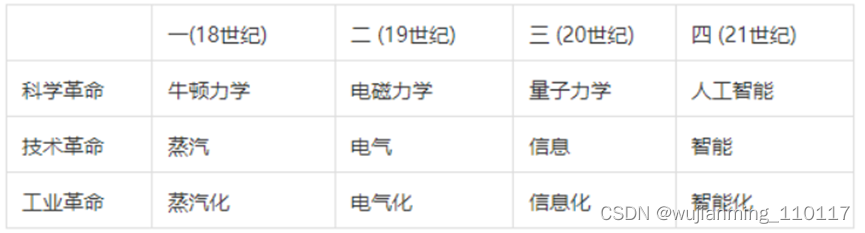

人类自然科学史是一幅幅波澜壮阔的画面:其起源于2500年前古希腊的自然哲学,经过400年前伽利略时期的痛苦孕育,在300年前成功诞生出牛顿力学。其后经历了四次科学革命,同步紧随了四次技术革命和工业革命的大爆发。

当前行业AI化与数字化为核心的智能化时代,云计算与AI等先进生产力开始有机结合与延伸拓展,通过加速提升的算力来逐步呈现数字经济的核心价值。按照《云网融合:算力时代的数字信息基础设施》一书的统计分析,算力的支撑使得数字经济占GDP比重由2015年的14.2%提升至2020年的38.6%。

算力、数据、算法共同构成了计算资源的三要素,而ADS领域正是三要素集大成者。AI算法在ADS领域的行业应用,其当前演进方向主要体现在:

1)能够在统一空间支持多模传感器感知融合与多任务共享;

2)预测与规划联合建模,离线与在线学习相结合,能够自学习处理不确定性下的安全与可解释问题,通过持续学习解决新场景问题。

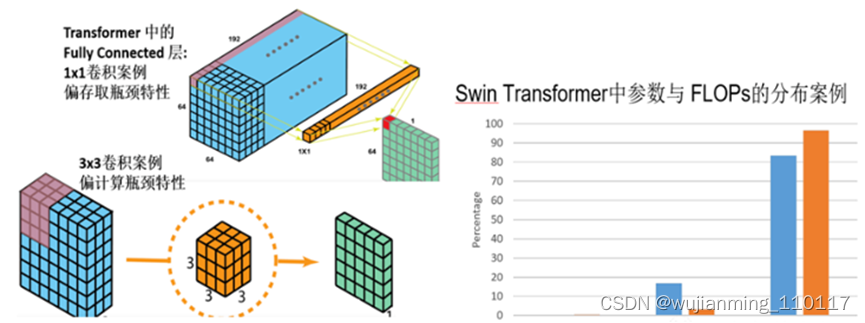

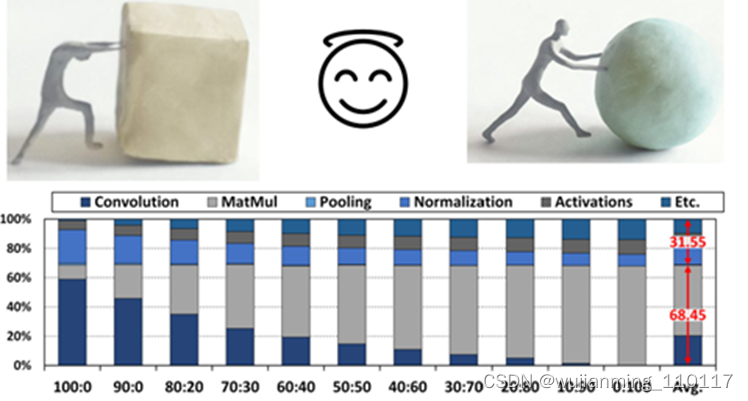

如图1和图2所示,对应ADS负载的多样化和融合感知决策算法多样化的演进趋势,ADS算力新需求体现在从compute-bound走向memory-bound,NPU的设计需求也从偏计算走向偏存算的混合模式。

图1 NPU设计新需求:从偏计算走向偏存算的混合模式

图2 DNN中不同模块的运行时间剖析图案例(注:引用参考文献1)

当前市场上主流AI算力芯片,都存在几个共性问题,一是低算力问题:多针对3x3卷积优化,算法总体效率低;二是内存墙问题:PE存算分离数据难共享;三是能耗墙问题:数据重复搬移高耗能。

从下一代的工程实践上看,ADS算法需要通过“硬件预埋,算法迭代,算力均衡“ ,提供一个向前兼容的解决方案,以通用大算力来解决未来不确定性的算法演进,具体体现在:

- 底层架构的演进:从存算分离到近内存计算,最终走向内存计算。

- 数据通道与模型:高速数据接口+数据压缩+模型压缩+低精度逼近计算+稀疏计算加速。

- 并行的顶层架构:模型-硬件联合设计,以及硬设计可配置+硬件调度+软运行可编程调度引擎。

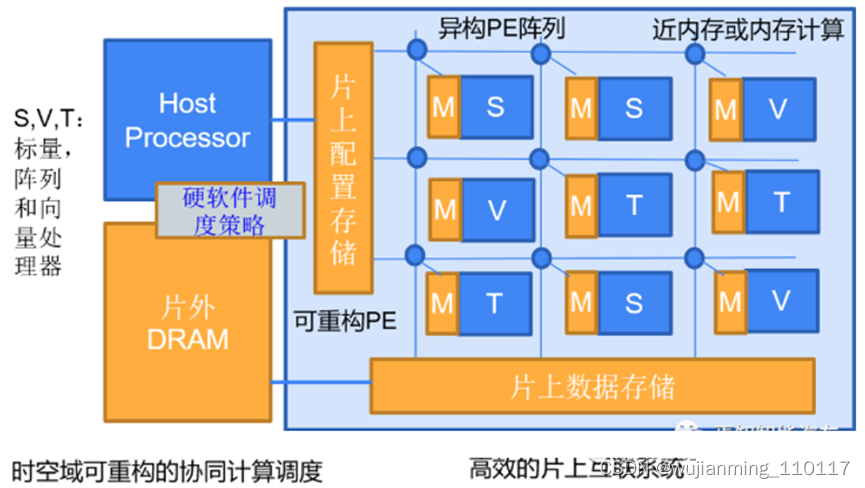

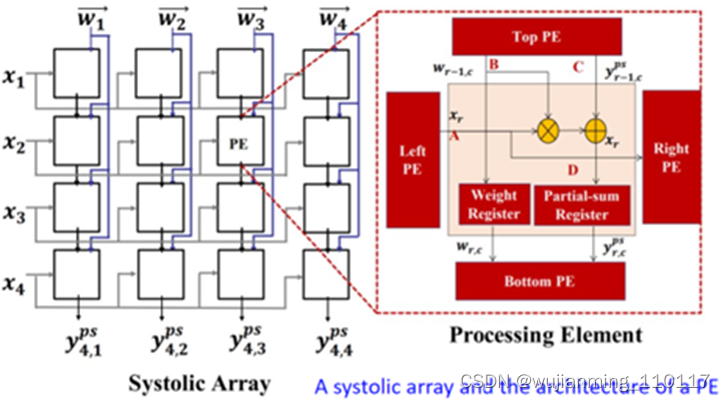

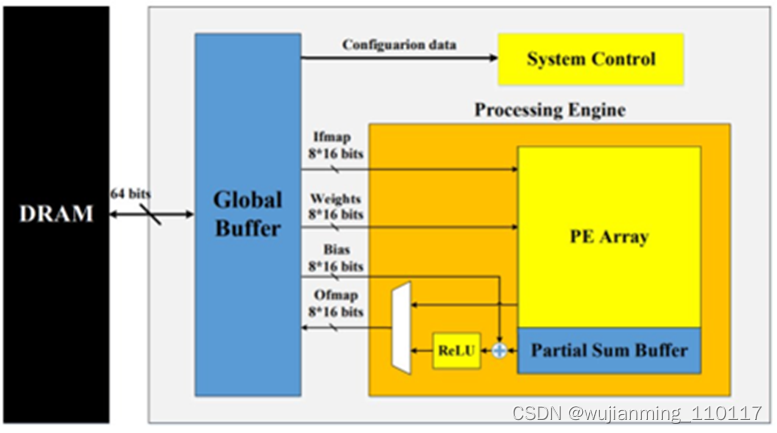

对比CPU十百级的并行处理单元和GPU上万级的并行处理单元,NPU会有百万级的并行计算单元,可以采用Spatial加速器架构来实现,即Spatial PE空间单元阵列通过NoC,数据总线,或跨PE的互联来实现数据流交互。粗颗粒度的可配置架构CGRA是Spatial加速器的一种形态,即可配置的PE Array通过纳秒或微秒级别可配置的Interconnect来对接,可以支持配置驱动或者数据流驱动运行。脉动Systolic加速器架构也是Spatial加速器的一类实现方式,其主要计算是通过1D或2D计算单元对数据流进行定向固定流动处理最终输出累加计算结果,存在的问题难以支撑压缩模型的稀疏计算加速处理。NPU的第二类计算单元是Vector加速器架构,其计算可以通过可配置的矢量核来实现。NPU也可以采用多核架构技术,即提供千百级的加速器物理核来组件封装提供更高程度的平行度,尤其是适合大算力下高并行数据负载。NPU另外一个在演进中的是内存处理器PIM架构,即通过将计算靠近存储的方式来降低数据搬移能耗和提升内存带宽。可以分成近内存计算与内存计算两种类型。近内存计算将计算引擎靠近传统的DRAM或者SRAM cell,保持设计特性。内存计算需要对内存cell添加数据计算逻辑,多采用ReRAM或者STT-RAM新型工艺,目前多采用数字类型的设计,技术难题是如何在运行态时进行大模型参数动态刷新,工艺实现也落后于市场预期。

图3 NPU细粒度可重构的硬件架构CGRA案例

如图3所示,总结来说,NPU可配置特性是指NPU可以通过软件定义来修改运行状态下CGRA硬件逻辑单元的运算与互联,可以通过配置数据比特流来修改配置内存。NPU可编程特性是指针对用户自定义的数据流,通过指令集来实现不同类型的计算操作。通常只有FPGA可以针对计算单元和互联提供细颗粒度的可配置特性,大算力NPU能够引进这样的先进设计思路也是势在必然的。

综上所述,NPU硬件架构的演进,其总体特性可以归结如下:

软件定义架构:当前行业云化和数字化推动软件架构从单体应用架构 - 垂直应用架构 - 分布式架构 -SOA 架构 - 微服务架构的演变。对于大算力NPU的硬件架构而言,其演进也不言而喻,同样需要解决高并发、大吞吐等问题,针对算法的多样性需求,同样需要通过软件定义架构,来实现底层微架构硬件的可配置、可调度、可弹性扩展特性,以及顶层架构的微任务与多并行调度,提升底层PE与数据通道的效率均衡,减少数据流的无效搬移与无效计算,提升能耗比和算力效率。

弹性负载均衡:对NPU微架构中的存储与计算PE而言,可配置意味着可以通过片上的控制逻辑来动态配置细颗粒度的PE阵列,通过Array+Vector异构组合的SHAV弹性架构,来适应算法中多形态的算子尺寸和数据流变化需求。对NPU顶层架构而言,微任务与多并行调度意味着,多核的SHAV计算模块,可以通过高带宽的分布式数据总线来搭建实现多核的弹性扩展。

联合优化设计:对NPU中模型-硬件联合设计而言,具体的实现策略体现在:

1)降低计算资源需求的策略,例如3x3卷积Conv可以通过面向通道的Conv3x3 +Conv1x1来实现,Conv5x5以上可以通过Conv3x3 +Conv1x1组合来实现;

2)逼近计算策略,可以通过低比特数据优化表征HFP8/INT8/INT4/IN4+Quantization-aware后训练来实现;

3)压缩与稀疏计算策略,可以通过模型裁剪与优化,参数统计从偏置分布向零分布调整,以及类似参数扰动+列打包的RL压缩编码来实现;

4)模型-硬件联合搜索,可以认为NPU预定义的硬件架构是模板,网络模型ASIC-NAS在有限硬件计算空间内进行DNN的模型搜索和模型小型化,寻求计算单元的最佳组合模型来提升相同计算复杂度下的等效算力效率。

达芬奇架构NPU

ADS-NPU芯片架构

AI算法在自动驾驶ADS领域的行业应用,其当前从感知到认知的演进方向,主要体现在:

1)能够在统一空间支持多模传感器感知融合与多任务共享,在提升有限算力的计算效率的同时,确保算法模型在信息提取中对极端恶劣场景(雨雪雾、低照度、高度遮挡、传感器部分失效、主动或被动场景攻击等)的泛化感知能力,降低对标注数据和高清地图的过度依赖;

2)预测与规划联合建模,离线与在线学习相结合,监督与自监督学习相结合,从而能够处理不确定性下的安全行驶与有效决策,提供认知决策行为的可解释问题,通过持续学习解决新场景问题。

当前,对应于ADS传感器负载多样化和融合感知决策算法多样化的演进趋势,ADS的算力需求和芯片加速能力以(十倍速/每几年)的持续高增长态势呈现。ADS领域大算力NPU芯片的当前发展现状,真可谓是:大算力之时代,以感知策,四两拨千斤者;狂洗牌乎战局,唯快应变,一力降十会也。

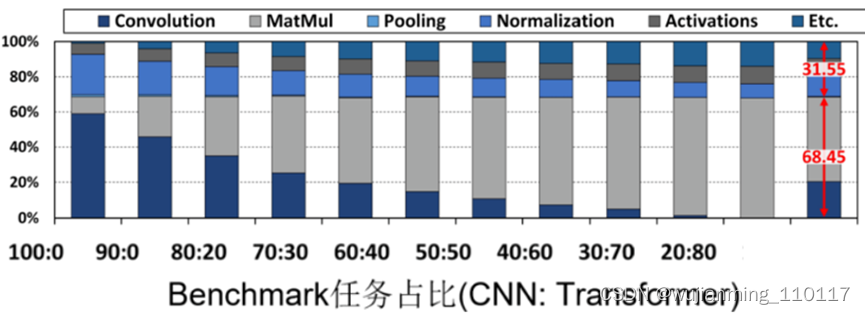

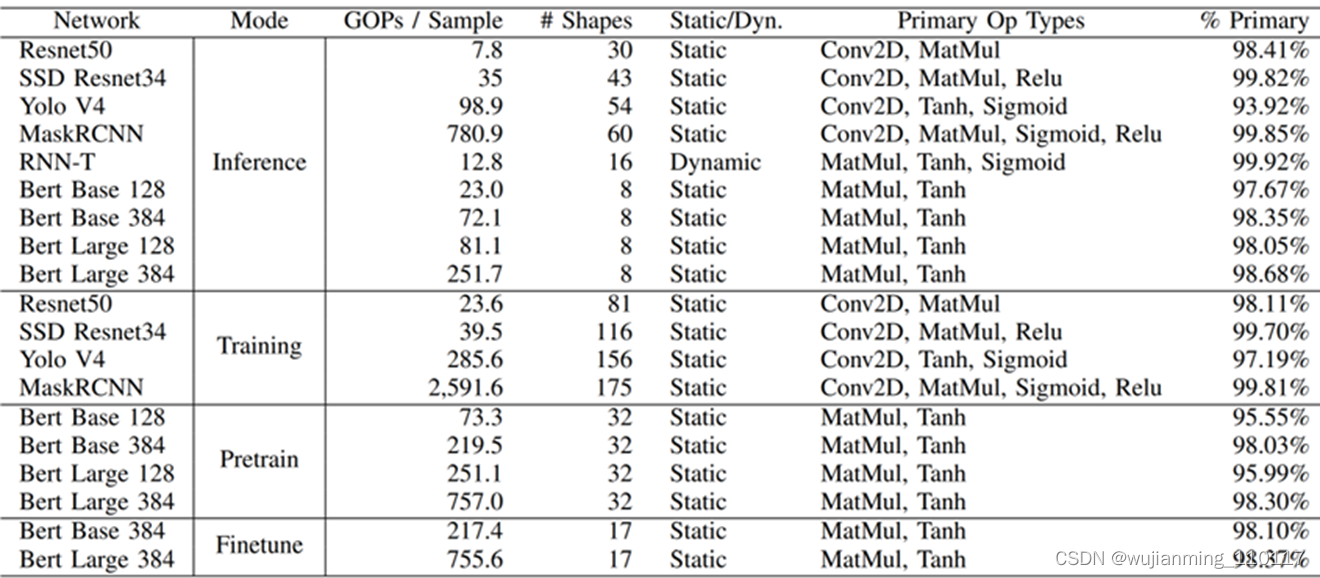

图1. DNN任务占比分析: CNN vs Transformer

(图表分析来自文献1)

如图1 所示,ADS算法从Compute-bound向Memory-bound演进。ADS的存算混合需求,可以通过“硬件预埋,算法迭代,算力均衡“ ,来提供一个向前兼容的解决方案,以通用大算力NPU设计来解决算法未来的不确定性,具体体现在:1) 底层架构的演进:从存算分离到近内存计算,最终走向内存计算; 2) 数据通道与模型:高速数据接口+数据压缩+模型压缩+低精度逼近计算+稀疏计算加速; 3) 并行的顶层架构:模型-硬件联合设计,以及硬设计可配置+硬件调度+软运行可编程调度引擎。

老子曾曰“合抱之木,生于毫末;九层之台,起于垒土;千里之行,始于足下。” 老子又曰 ”天下难事,必作于易;天下大事,必作于细。”处理艰难问题从易入手,致力远大目标从微着力。ADS-NPU芯片的架构设计,同样需要用【见微知著】的能力,来解决异构计算、稀疏计算、逼近计算、内存计算等几类常见的难题与挑战。

- 异构计算之设计挑战

图2. 脉动阵列架构(图表分析来自文献1)

图3. 可配置的脉动阵列架构(图表分析来自文献1)

对比CPU十百级的并行处理单元和GPU上万级的并行处理单元,NPU会有百万级的并行计算单元,可以采用Spatial加速器架构来实现,即Spatial PE空间单元阵列通过NoC,数据总线,或跨PE的互联来实现矩阵乘运算(全卷积计算或全连接FC计算)、数据流高速交互、以及运算数据共享。

粗颗粒度的可配置架构CGRA是Spatial加速器的一种形态,即可配置的PE Array通过纳秒或微秒级别可配置的Interconnect来对接,可以支持配置驱动或者数据流驱动运行。

如图2和图3所示,脉动Systolic加速器架构也是Spatial加速器的一类实现方式,其主要计算是通过1D或2D计算单元对数据流进行定向固定流动处理最终输出累加计算结果,对DNN输出对接卷积层或池化层的不同需求,可以动态调整硬件计算逻辑和数据通道,但存在的问题难以支撑压缩模型的稀疏计算加速处理。

NPU的第二类计算单元是Vector矢量加速器架构,面向矢量的Element-wise Sum、Conv1x1卷积、Batch Normalization、激活函数处理等运算操作,其计算可以通过可配置的矢量核来实现,业界常用的设计是标量+矢量+阵列加速器的组合应用来应对ADS多类传感器的不同前处理需求和多样化算法模型流水线并行处理的存算混合需求。

NPU SoC也可以采用多核架构技术,即提供千百级的加速器物理核来组件封装和Chiplet片上互联提供更高程度的平行度,尤其是适合大算力下高并行数据负载,这需要底层硬件调度与上层软件调度相结合,提供一个分布式硬件计算资源的细颗粒度运行态调用。

NPU另外一个在演进中的内存处理器PIM架构,即通过将计算靠近存储的方式来降低数据搬移能耗和提升内存带宽。可以分成近内存计算与内存计算两种类型。近内存计算将计算引擎靠近传统的DRAM或者SRAM cell,保持设计特性。

内存计算需要对内存cell添加数据计算逻辑,多采用ReRAM或者STT-MRAM新型工艺,目前采用模拟或数字类型的设计,可实现>100TOPS/Watt的PPA性能,但技术难题是如何在运行态时进行大模型参数动态刷新,工艺实现可能也落后于市场预期。

图4. AI算法模型负载的算子分布统计(图表分析来自文献2)

图5. nVidia A100的Tens