- 1mysql数据库now_MySQL NOW() 函数

- 2Chatglm3+langchain智能对话,本地文本库构建问答,图片文本库构建与问答搜索

- 3自动驾驶apollo9.0 Dreamview Debug方法_apollo9.0代码下载

- 4linux下的vim使用教程!从零基础到入门!_linux的vim使用教程

- 5阅读《吴军·硅谷来信》一年的回顾与思考

- 6AttributeError: module ‘pkgutil‘ has no attribute ‘ImpImporter‘. Did you mean: ‘zipimporter‘?_attributeerror: module 'pkgutil' has no attribute

- 7BAT面试算法基础学习笔记_bat 固定长度数列

- 8LeetCode 刷题 [C++] 第3题.无重复字符的最长子串

- 9[uniapp]使用uview组件自定义tabbar_uniapp uview tabbar

- 10HarmonyOS_Dev,DevEco Studio安装HarmonyOS JSSDK报错“Run 'npm install' failed”?

SSD LDPC软错误探测方案解读

赞

踩

上一篇文档中,基于SSD LDPC(Low-Density Parity-Check Codes)原理背景和纠错能力作了简单的介绍。

扩展阅读:

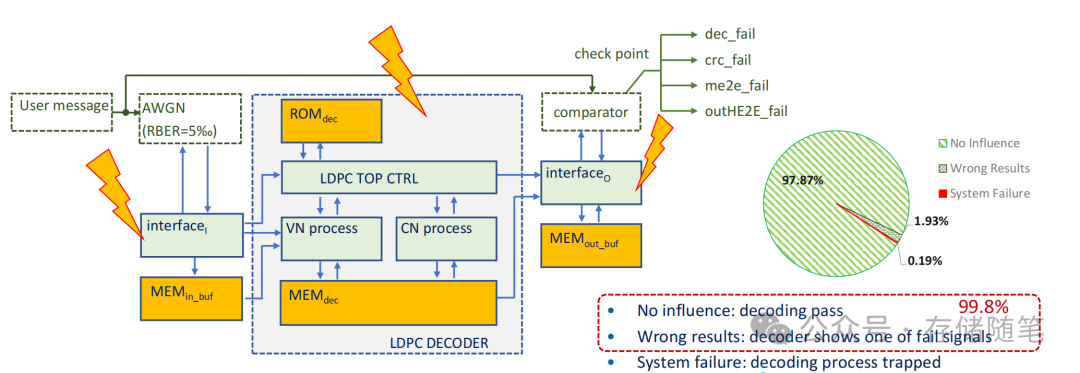

本篇结合SMI发布的研究成果,通过SSD控制内部LDPC更底层的架构,来解读如何增强软错误探测能力和抗噪声干扰能力。

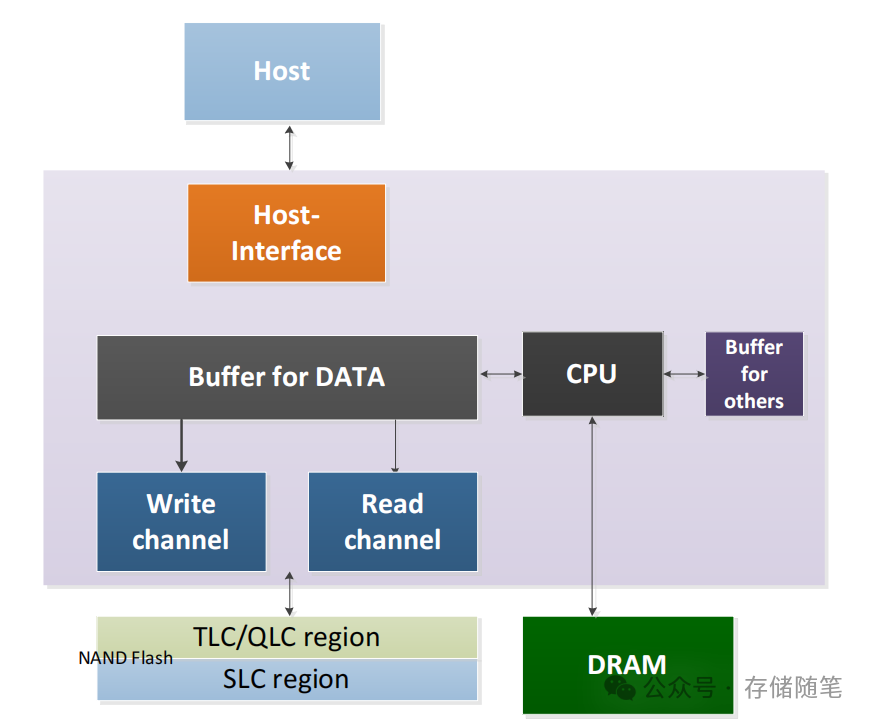

在固态硬盘SSD模块级别,噪声源主要有以下几类:

-

控制器外部数据传输总线噪声:比如PCIe总线,以及与DRAM缓存和闪存芯片之间的接口。这些接口在高速数据交换过程中会产生电磁干扰,影响数据的准确传输。

-

NAND编程/读取/擦除操作噪声:NAND闪存的P/E(编程/擦除)周期中,由于电荷迁移、漏电流等因素,尤其是在高密度QLC存储单元中,噪声和各种干扰现象会变得更严重。

-

辐射诱导的软错误:宇宙射线等放射性粒子对电子设备中的存储单元造成单粒子翻转(Single Event Upset, SEU),导致数据位错误。

-

其他噪声:除了上述明确提及的噪声源外,还有诸如电源波动、温度变化、器件老化等其他不确定因素产生的噪声。

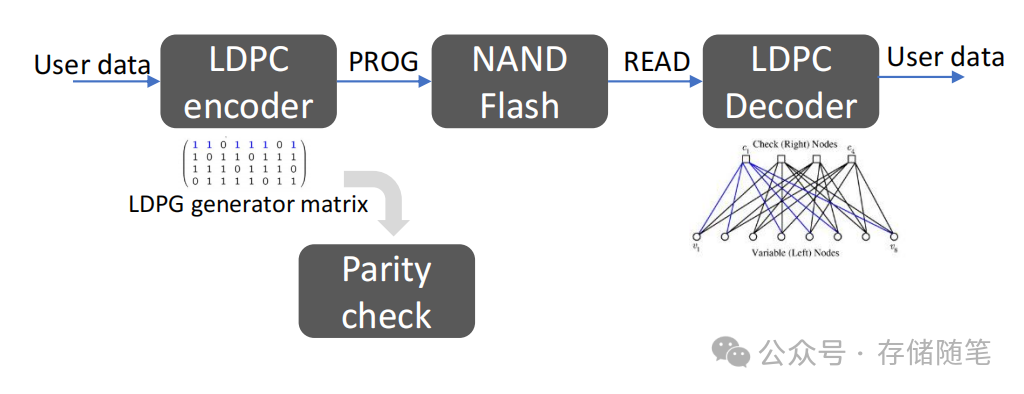

为了对抗这些噪声导致的数据错误,SSD模块采用了ECC技术。ECC能够检测和纠正部分错误,通过将数据编码成带有冗余信息的编码字(codewords),可以区分出可纠正错误和不可纠正错误,同时也能够识别出可检测错误和未被检测出的错误。

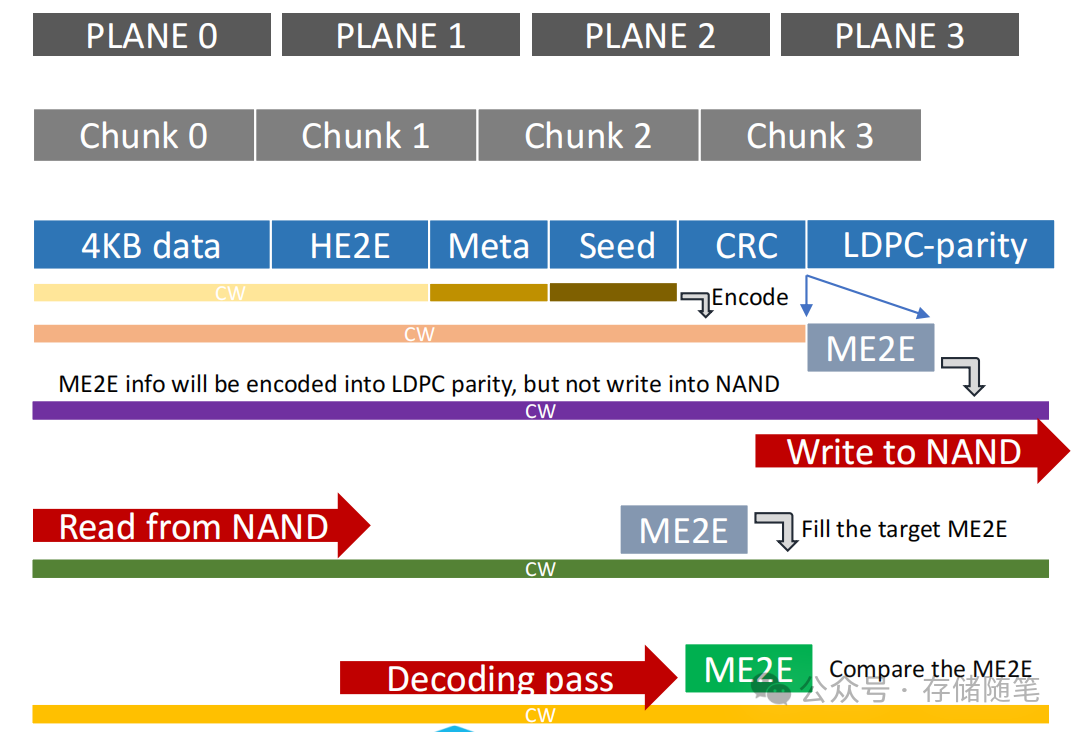

在固态存储中,数据通常会被划分为多个数据块(Chunks),每个数据块除了包含用户数据外,还会附加额外的信息,如HE2E、元数据(Meta)、种子(Seed)、CRC校验值以及LDPC奇偶校验码。

LDPC奇偶校验完整性检查是一个确保基于LDPC编码的数据在写入或读取过程中不遭受意外损坏的关键环节。在数据写入NAND闪存前,首先需要对用户数据和相关辅助信息进行LDPC编码生成相应的奇偶校验位,这些奇偶校验位包含了足以恢复潜在错误的信息。LDPC编码器本身包含了大量的组合逻辑和寄存器结构,甚至包括只读存储器(ROM)部分,以实现复杂而高效的编码过程。

在实际操作中,由于宇宙射线等自然现象引发的单粒子翻转(Single Event Upset, SEU)可能会导致LDPC奇偶校验位出现错误。为了避免这种情况导致的无效写入,必须在数据从控制器传输至NAND的过程中对LDPC奇偶校验的完整性进行即时检查。如果检测到奇偶校验位错误,则跳过编程指令,避免将错误的奇偶校验信息写入NAND,而是重新进行编码后再尝试写入。

此外,在数据读取阶段,同样会进行多重验证以确保数据的准确无误。读取的数据不仅通过LDPC解码器来尝试纠正潜在的软错误,同时还需要通过CRC校验来验证整个数据块的完整性。另外,介质端到端(Media End-to-End, E2E)信息的比较也是重要的一环,通过对比原始写入时记录的E2E信息与当前读出的数据进行一致性校验,确保即使是在错误的位置上但内容仍然可纠正的数据块能够被正确识别和处理。

在SSD控制器设计中,LDPC解码器作为一个强大的错误纠正工具,用于修复在数据路径中发生的大部分软错误。通过LDPC编码和解码技术,可以有效地检测并修复由噪声或者其他不可预见因素引起的错误位。

当错误被检测到时,会执行读重试操作,这是高效错误恢复步骤的一部分,体现了LDPC解码器在纠正偶尔错误方面的灵活性和效率。除了LD