- 1-bash: sqlplus: command not found 解决

- 2电子政务信息系统整合共享管理研究_政务系统整合的原因

- 3浅析xxl-obj分布式任务调度平台RCE漏洞_xxljob 漏洞

- 4java outofmemory怎么解决_java.lang.OutOfMemoryError异常解决方法

- 5python程序设计风格描述_Python 编程风格

- 6深度学习基础——卷积神经网络的基础模块

- 7SourceTree强大的GIT工作流_sourcetree git工作流

- 8FlinkJob提交和参数配置_jobmanager.rpc.address

- 9es映射父子关系java_es 父子关系

- 10C语言之fileno()函数_c语言fileno

VGA协议实践

赞

踩

实验说明: FPGA芯片采用“EP4CE115F29C7”,软件环境-Quartus-Ⅱ

一、VGA介绍

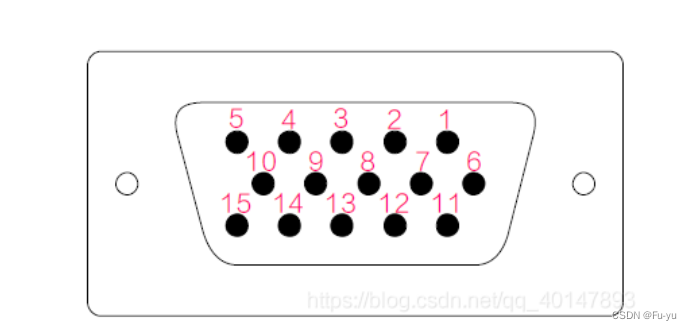

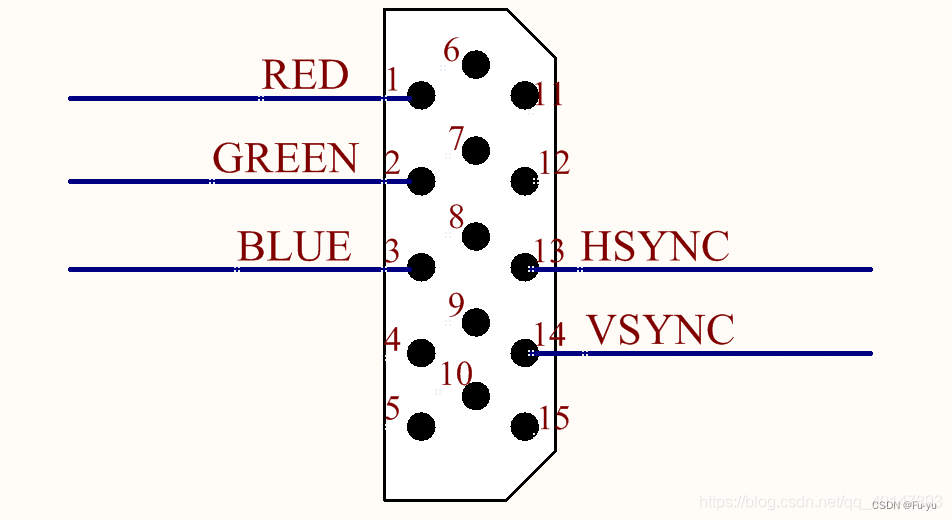

VGA(Video Graphics Array)视频图形阵列是IBM于1987年提出的一个使用模拟信号的电脑显示标准。VGA接口即电脑采用VGA标准输出数据的专用接口。VGA是一种D型接口,采用非对称分布连接方式,共有15针,分三排,每排5个孔。

VGA接口:

VGA接口管脚表:

VGA显示原理:

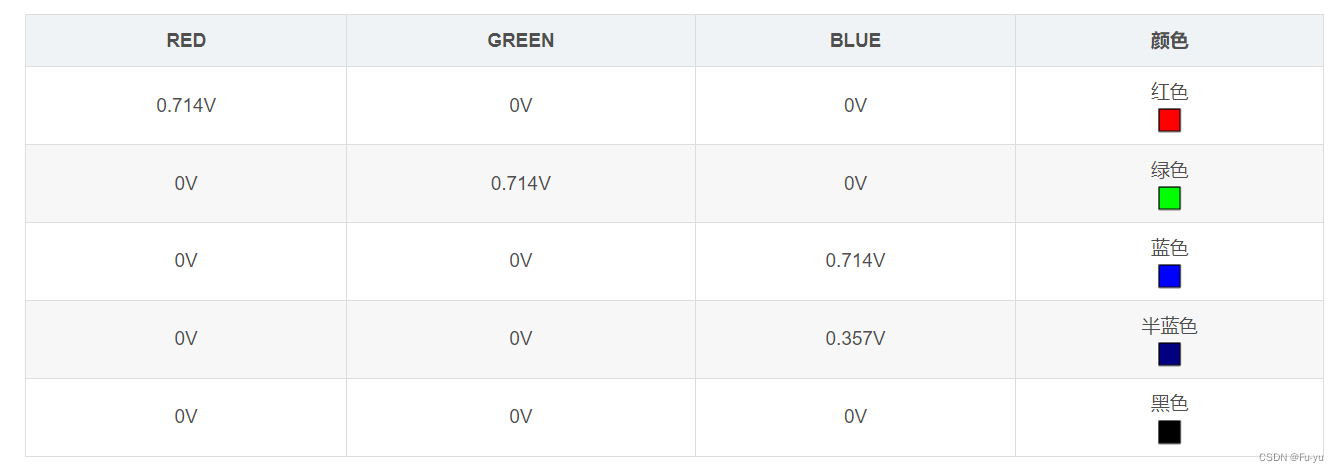

要知道VGA显示器是不认识数字信号的,它只认识模拟信号。所谓它只认识模拟信号,即 在它的数据引脚1、2、3(RED、GREEN、BLUE)输入的不是简单的0、1数字信号,而是模拟电压(0V-0.714V)。1、2、3引脚具有不同的电压时,VGA显示器显示不同的颜色。

在VGA接口的1、2、3引脚分别接至以下电压:

VGA通信时序:

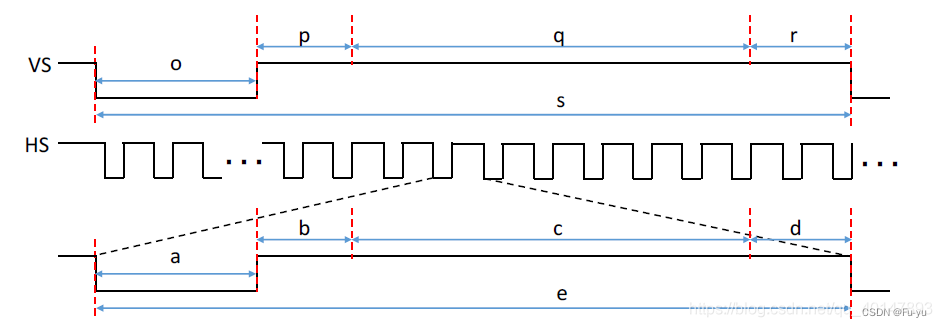

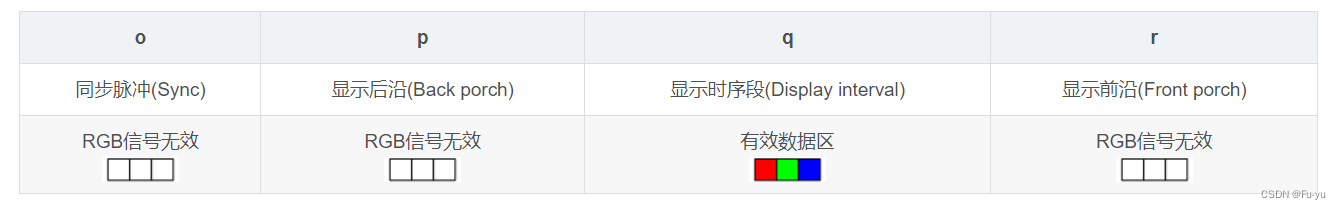

帧时序和行时序都有四部分:

帧时序和行时序都有四部分:

帧时序的四个部分别是:同步脉冲(Sync o)、显示后沿(Back porch p)、显示时序段(Display interval q)和显示前沿(Front porchr)。其中同步脉冲(Sync o)、显示后沿(Back porch p)和显示前沿(Front porch r)是消隐区,RGB信号无效,屏幕不显示数据。显示时序段(Display interval q)是有效数据区。.

行时序的四个部分分别是:同步脉冲(Sync a)、显示后沿(Back porch b)、显示时序(Display interval c)和显示前沿(Front porchd)。其中同步脉冲(Sync a)、显示后沿(Back porch b)和显示前沿(Front porch d)是消隐区,RGB信号无效,屏幕不显示数据。显示时序段(Display interval c)是有效数据区。

VGA时序解析:

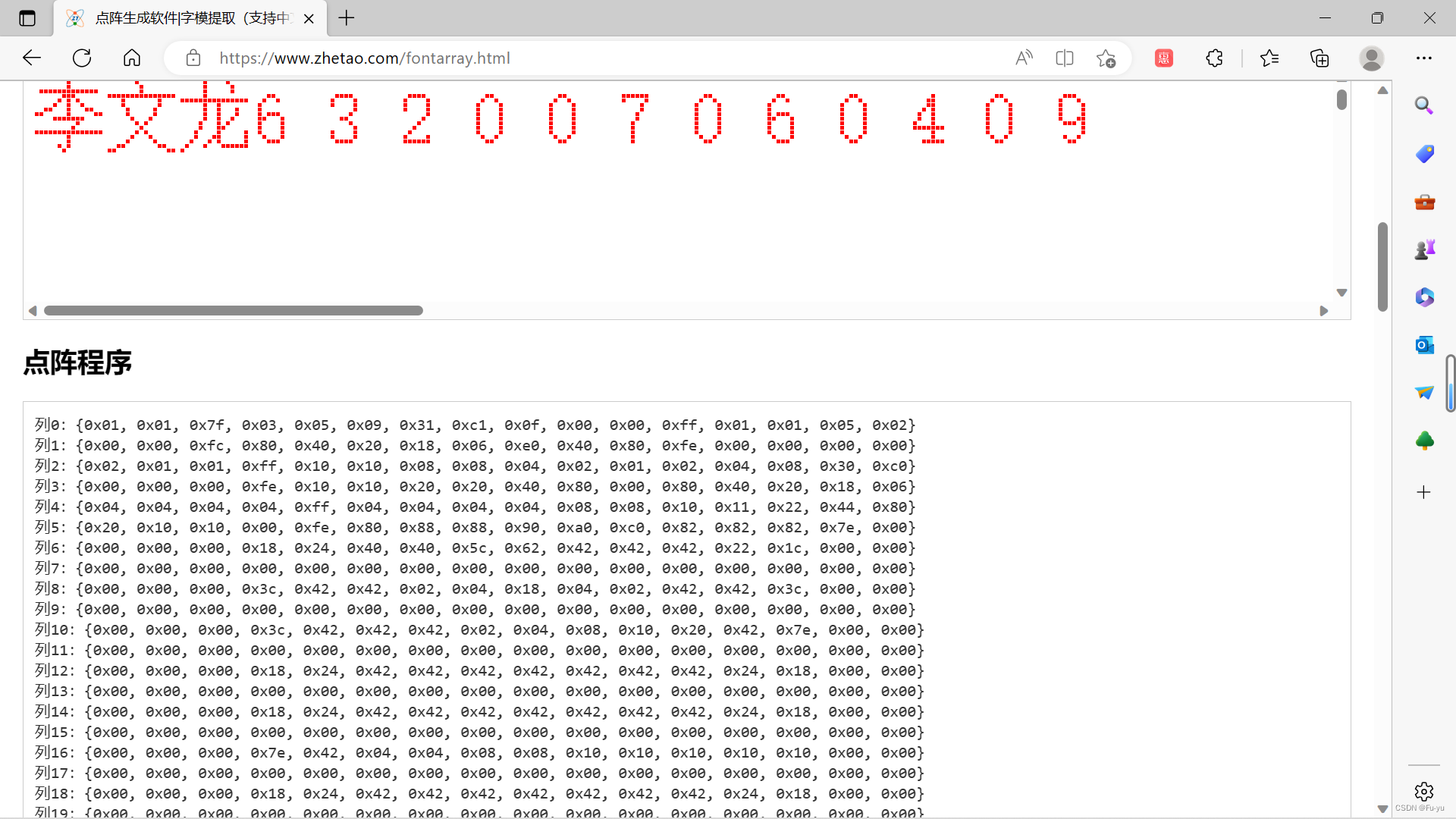

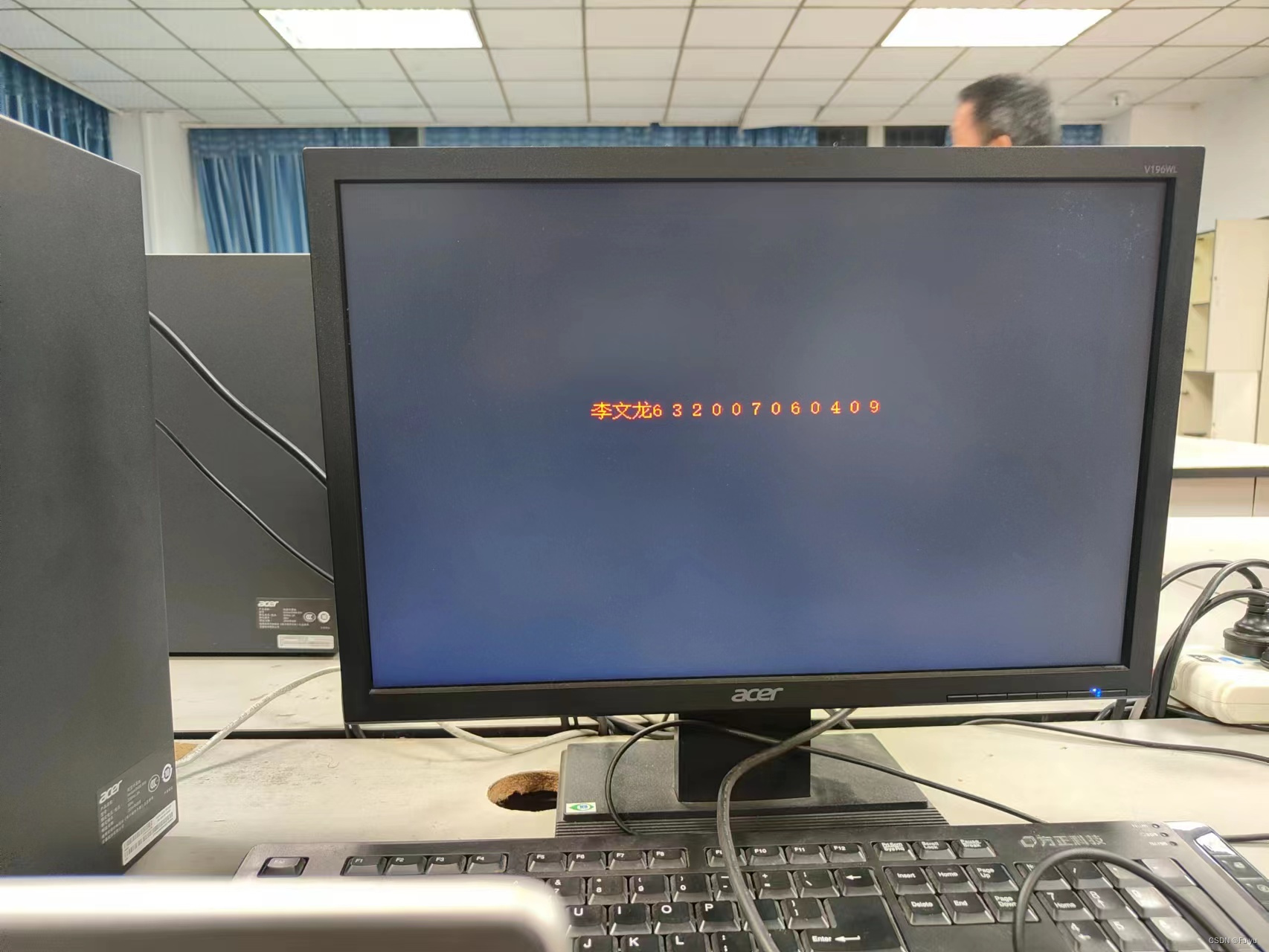

二、verilog编程显示字符

提取字符:

通过在线网站汉字点阵提取:

在线提取网站地址:

https://www.zhetao.com/fontarray.html

代码实现:

module VGA_test( OSC_50, //原CLK2_50时钟信号 VGA_CLK, //VGA自时钟 VGA_HS, //行同步信号 VGA_VS, //场同步信号 VGA_BLANK, //复合空白信号控制信号 当BLANK为低电平时模拟视频输出消隐电平,此时从R9~R0,G9~G0,B9~B0输入的所有数据被忽略 VGA_SYNC, //符合同步控制信号 行时序和场时序都要产生同步脉冲 VGA_R, //VGA绿色 VGA_B, //VGA蓝色 VGA_G); //VGA绿色 input OSC_50; //外部时钟信号CLK2_50 output VGA_CLK,VGA_HS,VGA_VS,VGA_BLANK,VGA_SYNC; output [7:0] VGA_R,VGA_B,VGA_G; parameter H_FRONT = 16; //行同步前沿信号周期长 parameter H_SYNC = 96; //行同步信号周期长 parameter H_BACK = 48; //行同步后沿信号周期长 parameter H_ACT = 640; //行显示周期长 parameter H_BLANK = H_FRONT+H_SYNC+H_BACK; //行空白信号总周期长 parameter H_TOTAL = H_FRONT+H_SYNC+H_BACK+H_ACT; //行总周期长耗时 parameter V_FRONT = 11; //场同步前沿信号周期长 parameter V_SYNC = 2; //场同步信号周期长 parameter V_BACK = 31; //场同步后沿信号周期长 parameter V_ACT = 480; //场显示周期长 parameter V_BLANK = V_FRONT+V_SYNC+V_BACK; //场空白信号总周期长 parameter V_TOTAL = V_FRONT+V_SYNC+V_BACK+V_ACT; //场总周期长耗时 reg [10:0] H_Cont; //行周期计数器 reg [10:0] V_Cont; //场周期计数器 wire [7:0] VGA_R; //VGA红色控制线 wire [7:0] VGA_G; //VGA绿色控制线 wire [7:0] VGA_B; //VGA蓝色控制线 reg VGA_HS; reg VGA_VS; reg [10:0] X; //当前行第几个像素点 reg [10:0] Y; //当前场第几行 reg CLK_25; always@(posedge OSC_50) begin CLK_25=~CLK_25; //时钟 end assign VGA_SYNC = 1'b0; //同步信号低电平 assign VGA_BLANK = ~((H_Cont<H_BLANK)||(V_Cont<V_BLANK)); //当行计数器小于行空白总长或场计数器小于场空白总长时,空白信号低电平 assign VGA_CLK = ~CLK_to_DAC; //VGA时钟等于CLK_25取反 assign CLK_to_DAC = CLK_25; always@(posedge CLK_to_DAC) begin if(H_Cont<H_TOTAL) //如果行计数器小于行总时长 H_Cont<=H_Cont+1'b1; //行计数器+1 else H_Cont<=0; //否则行计数器清零 if(H_Cont==H_FRONT-1) //如果行计数器等于行前沿空白时间-1 VGA_HS<=1'b0; //行同步信号置0 if(H_Cont==H_FRONT+H_SYNC-1) //如果行计数器等于行前沿+行同步-1 VGA_HS<=1'b1; //行同步信号置1 if(H_Cont>=H_BLANK) //如果行计数器大于等于行空白总时长 X<=H_Cont-H_BLANK; //X等于行计数器-行空白总时长 (X为当前行第几个像素点) else X<=0; //否则X为0 end always@(posedge VGA_HS) begin if(V_Cont<V_TOTAL) //如果场计数器小于行总时长 V_Cont<=V_Cont+1'b1; //场计数器+1 else V_Cont<=0; //否则场计数器清零 if(V_Cont==V_FRONT-1) //如果场计数器等于场前沿空白时间-1 VGA_VS<=1'b0; //场同步信号置0 if(V_Cont==V_FRONT+V_SYNC-1) //如果场计数器等于行前沿+场同步-1 VGA_VS<=1'b1; //场同步信号置1 if(V_Cont>=V_BLANK) //如果场计数器大于等于场空白总时长 Y<=V_Cont-V_BLANK; //Y等于场计数器-场空白总时长 (Y为当前场第几行) else Y<=0; //否则Y为0 end reg valid_yr; always@(posedge CLK_to_DAC) if(V_Cont == 10'd32) //场计数器=32时 valid_yr<=1'b1; //行输入激活 else if(V_Cont==10'd512) //场计数器=512时 valid_yr<=1'b0; //行输入冻结 wire valid_y=valid_yr; //连线 reg valid_r; always@(posedge CLK_to_DAC) if((H_Cont == 10'd32)&&valid_y) //行计数器=32时 valid_r<=1'b1; //像素输入激活 else if((H_Cont==10'd512)&&valid_y) //行计数器=512时 valid_r<=1'b0; //像素输入冻结 wire valid = valid_r; //连线 wire[10:0] x_dis; //像素显示控制信号 wire[10:0] y_dis; //行显示控制信号 assign x_dis=X; //连线X assign y_dis=Y; //连线Y parameter char_line00=240'h010002000420000000000000000000000000000000000000000000000000, char_line01=240'h010001000410000000000000000000000000000000000000000000000000, char_line02=240'h7ffc01000410000000000000000000000000000000000000000000000000, char_line03=240'h0380fffe040018003c003c00180018007e00180018001800040018003800, char_line04=240'h05401010fffe2400420042002400240042002400240024000c0024004400, char_line05=240'h0920101004804000420042004200420004004200400042000c0042004200, char_line06=240'h311808200488400002004200420042000400420040004200140042004200, char_line07=240'hc106082004885c000400020042004200080042005c004200240042004200, char_line08=240'h0fe004400490620018000400420042000800420062004200240042004600, char_line09=240'h0040028008a0420004000800420042001000420042004200440042003a00, char_line0a=240'h0080010008c04200020010004200420010004200420042007f0042000200, char_line0b=240'hfffe02801082420042002000420042001000420042004200040042000200, char_line0c=240'h010004401182220042004200240024001000240022002400040024002400, char_line0d=240'h0100082022821c003c007e0018001800100018001c0018001f0018001800, char_line0e=240'h05003018447e000000000000000000000000000000000000000000000000, char_line0f=240'h0200c0068000000000000000000000000000000000000000000000000000; reg[7:0] char_bit; always@(posedge CLK_to_DAC) if(X==10'd180)char_bit<=9'd240; //当显示到144像素时准备开始输出图像数据 else if(X>10'd180&&X<10'd420) //左边距屏幕144像素到416像素时 416=144+272(图像宽度) char_bit<=char_bit-1'b1; //倒着输出图像信息 reg[29:0] vga_rgb; //定义颜色缓存 always@(posedge CLK_to_DAC) if(X>10'd180&&X<10'd420) //X控制图像的横向显示边界:左边距屏幕左边144像素 右边界距屏幕左边界416像素 begin case(Y) //Y控制图像的纵向显示边界:从距离屏幕顶部160像素开始显示第一行数据 10'd200: if(char_line00[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; //如果该行有数据 则颜色为红色 else vga_rgb<=30'b0000000000_0000000000_0000000000; //否则为黑色 10'd201: if(char_line01[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd202: if(char_line02[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd203: if(char_line03[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd204: if(char_line04[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd205: if(char_line05[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd206: if(char_line06[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd207: if(char_line07[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd208: if(char_line08[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd209: if(char_line09[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd210: if(char_line0a[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd211: if(char_line0b[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd212: if(char_line0c[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd213: if(char_line0d[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd214: if(char_line0e[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000; 10'd215: if(char_line0f[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; else vga_rgb<=30'b0000000000_0000000000_0000000000; default:vga_rgb<=30'h0000000000; //默认颜色黑色 endcase end else vga_rgb<=30'h000000000; //否则黑色 assign VGA_R=vga_rgb[23:16]; assign VGA_G=vga_rgb[15:8]; assign VGA_B=vga_rgb[7:0]; endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

- 121

- 122

- 123

- 124

- 125

- 126

- 127

- 128

- 129

- 130

- 131

- 132

- 133

- 134

- 135

- 136

- 137

- 138

- 139

- 140

- 141

- 142

- 143

- 144

- 145

- 146

- 147

- 148

- 149

- 150

- 151

- 152

- 153

- 154

- 155

- 156

- 157

- 158

- 159

- 160

- 161

- 162

- 163

- 164

- 165

- 166

- 167

- 168

- 169

- 170

- 171

- 172

- 173

- 174

- 175

运行效果:

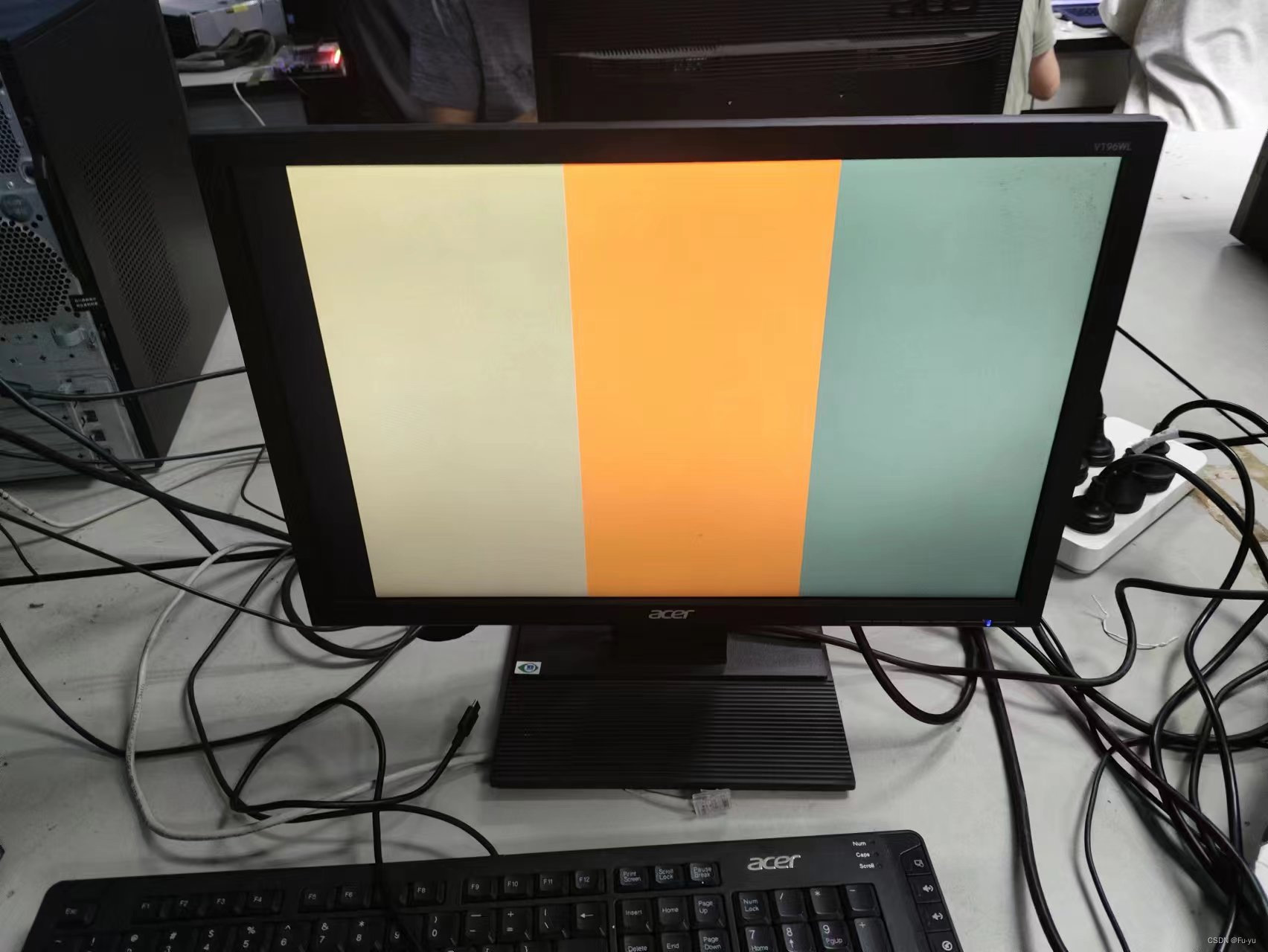

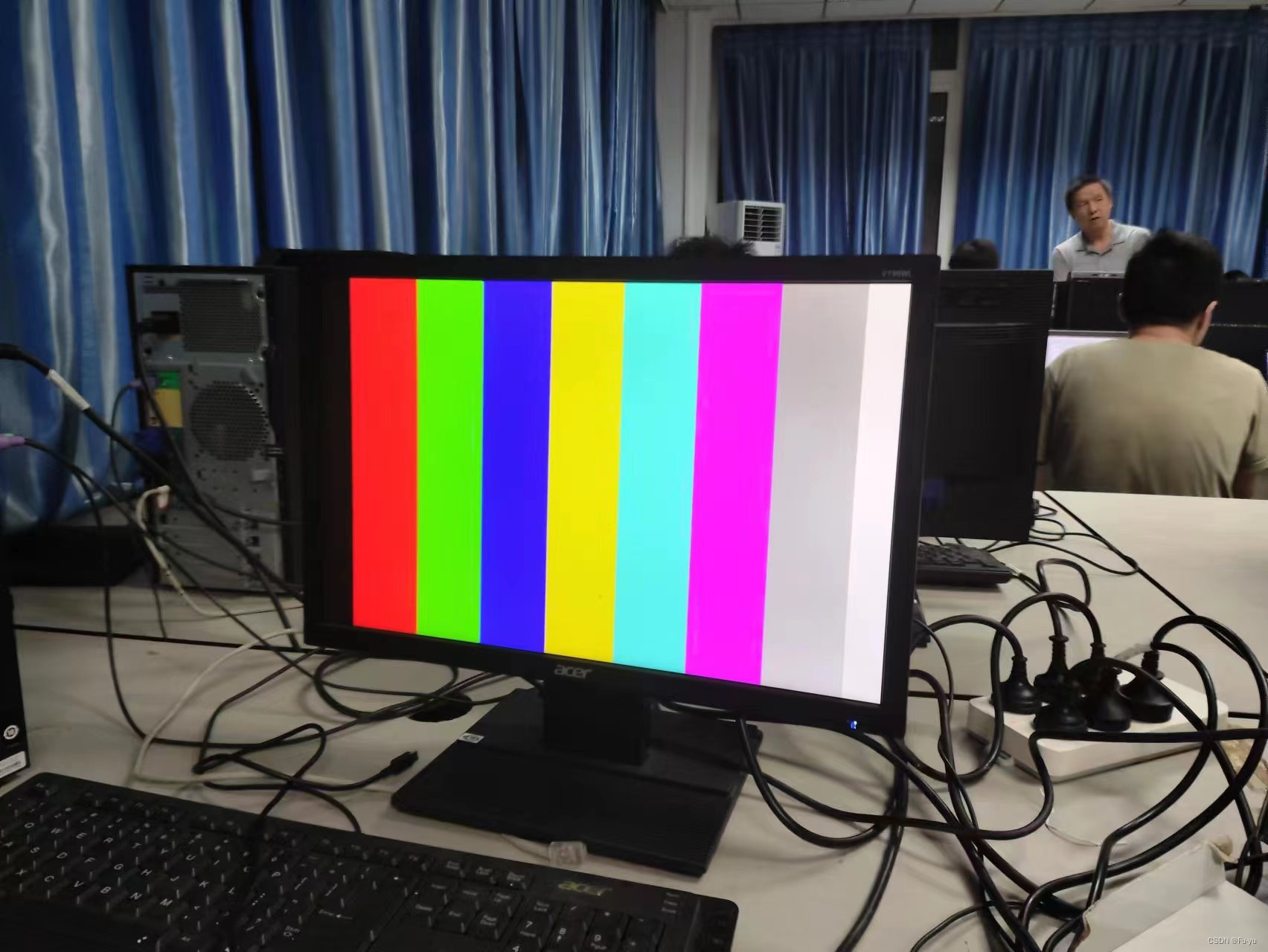

三、verilog编写显示彩色条纹

代码编写:

module VGA_colorbar_test( OSC_50, //原CLK2_50时钟信号 VGA_CLK, //VGA自时钟 VGA_HS, //行同步信号 VGA_VS, //场同步信号 VGA_BLANK, //复合空白信号控制信号 当BLANK为低电平时模拟视频输出消隐电平,此时从R9~R0,G9~G0,B9~B0输入的所有数据被忽略 VGA_SYNC, //符合同步控制信号 行时序和场时序都要产生同步脉冲 VGA_R, //VGA绿色 VGA_B, //VGA蓝色 VGA_G); //VGA绿色 input OSC_50; //外部时钟信号CLK2_50 output VGA_CLK,VGA_HS,VGA_VS,VGA_BLANK,VGA_SYNC; output [7:0] VGA_R,VGA_B,VGA_G; parameter H_FRONT = 16; //行同步前沿信号周期长 parameter H_SYNC = 96; //行同步信号周期长 parameter H_BACK = 48; //行同步后沿信号周期长 parameter H_ACT = 640; //行显示周期长 parameter H_BLANK = H_FRONT+H_SYNC+H_BACK; //行空白信号总周期长 parameter H_TOTAL = H_FRONT+H_SYNC+H_BACK+H_ACT; //行总周期长耗时 parameter V_FRONT = 11; //场同步前沿信号周期长 parameter V_SYNC = 2; //场同步信号周期长 parameter V_BACK = 31; //场同步后沿信号周期长 parameter V_ACT = 480; //场显示周期长 parameter V_BLANK = V_FRONT+V_SYNC+V_BACK; //场空白信号总周期长 parameter V_TOTAL = V_FRONT+V_SYNC+V_BACK+V_ACT; //场总周期长耗时 reg [10:0] H_Cont; //行周期计数器 reg [10:0] V_Cont; //场周期计数器 wire [7:0] VGA_R; //VGA红色控制线 wire [7:0] VGA_G; //VGA绿色控制线 wire [7:0] VGA_B; //VGA蓝色控制线 reg VGA_HS; reg VGA_VS; reg [10:0] X; //当前行第几个像素点 reg [10:0] Y; //当前场第几行 reg CLK_25; always@(posedge OSC_50)begin CLK_25=~CLK_25; //时钟 end assign VGA_SYNC = 1'b0; //同步信号低电平 assign VGA_BLANK = ~((H_Cont<H_BLANK)||(V_Cont<V_BLANK)); //当行计数器小于行空白总长或场计数器小于场空白总长时,空白信号低电平 assign VGA_CLK = ~CLK_to_DAC; //VGA时钟等于CLK_25取反 assign CLK_to_DAC = CLK_25; always@(posedge CLK_to_DAC)begin if(H_Cont<H_TOTAL) //如果行计数器小于行总时长 H_Cont<=H_Cont+1'b1; //行计数器+1 else H_Cont<=0; //否则行计数器清零 if(H_Cont==H_FRONT-1) //如果行计数器等于行前沿空白时间-1 VGA_HS<=1'b0; //行同步信号置0 if(H_Cont==H_FRONT+H_SYNC-1) //如果行计数器等于行前沿+行同步-1 VGA_HS<=1'b1; //行同步信号置1 if(H_Cont>=H_BLANK) //如果行计数器大于等于行空白总时长 X<=H_Cont-H_BLANK; //X等于行计数器-行空白总时长 (X为当前行第几个像素点) else X<=0; //否则X为0 end always@(posedge VGA_HS)begin if(V_Cont<V_TOTAL) //如果场计数器小于行总时长 V_Cont<=V_Cont+1'b1; //场计数器+1 else V_Cont<=0; //否则场计数器清零 if(V_Cont==V_FRONT-1) //如果场计数器等于场前沿空白时间-1 VGA_VS<=1'b0; //场同步信号置0 if(V_Cont==V_FRONT+V_SYNC-1) //如果场计数器等于行前沿+场同步-1 VGA_VS<=1'b1; //场同步信号置1 if(V_Cont>=V_BLANK) //如果场计数器大于等于场空白总时长 Y<=V_Cont-V_BLANK; //Y等于场计数器-场空白总时长 (Y为当前场第几行) else Y<=0; //否则Y为0 end reg valid_yr; always@(posedge CLK_to_DAC)begin if(V_Cont == 10'd32) //场计数器=32时 valid_yr<=1'b1; //行输入激活 else if(V_Cont==10'd512) //场计数器=512时 valid_yr<=1'b0; //行输入冻结 end wire valid_y=valid_yr; //连线 reg valid_r; always@(posedge CLK_to_DAC)begin if((H_Cont == 10'd32)&&valid_y) //行计数器=32时 valid_r<=1'b1; //像素输入激活 else if((H_Cont==10'd512)&&valid_y) //行计数器=512时 valid_r<=1'b0; //像素输入冻结 end wire valid = valid_r; //连线 assign x_dis=X; //连线X assign y_dis=Y; //连线Y // reg[7:0] char_bit; // always@(posedge CLK_to_DAC) // if(X==10'd144)char_bit<=9'd240; //当显示到144像素时准备开始输出图像数据 // else if(X>10'd144&&X<10'd384) //左边距屏幕144像素到416像素时 416=144+272(图像宽度) // char_bit<=char_bit-1'b1; //倒着输出图像信息 reg[29:0] vga_rgb; //定义颜色缓存 always@(posedge CLK_to_DAC) begin if(X>=0&&X<200)begin //X控制图像的横向显示边界:左边距屏幕左边144像素 右边界距屏幕左边界416像素 vga_rgb<=30'hffffffffff; //白色 end else if(X>=200&&X<400)begin vga_rgb<=30'hf00ff65f1f; end else if(X>=400&&X<600)begin vga_rgb<=30'h9563486251; end else begin vga_rgb<=30'h5864928654; end end assign VGA_R=vga_rgb[23:16]; assign VGA_G=vga_rgb[15:8]; assign VGA_B=vga_rgb[7:0]; endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

结果显示:

使用不同的分辨率可以定义一个文件保存

`define vga_640_480 `define vga_1920_1080 `define vga_1024_768 `ifdef vga_640_480 //执行操作A `define H_Right_Border 8 `define H_Front_Porch 8 `define H_Sync_Time 96 `define H_Back_Porch 40 `define H_Left_Border 8 `define H_Data_Time 640 `define H_Total_Time 800 `define V_Bottom_Border 8 `define V_Front_Porch 2 `define V_Sync_Time 2 `define V_Back_Porch 25 `define V_Top_Border 8 `define V_Data_Time 480 `define V_Total_Time 525 `elsif vga_1920_1080 //执行操作B `define H_Right_Border 0 `define H_Front_Porch 88 `define H_Sync_Time 44 `define H_Back_Porch 148 `define H_Left_Border 0 `define H_Data_Time 1920 `define H_Total_Time 2200 `define V_Bottom_Border 0 `define V_Front_Porch 4 `define V_Sync_Time 5 `define V_Back_Porch 36 `define V_Top_Border 0 `define V_Data_Time 1080 `define V_Total_Time 1125 `elsif vga_1024_768 `define H_Right_Border 0 `define H_Front_Porch 24 `define H_Sync_Time 136 `define H_Back_Porch 160 `define H_Left_Border 0 `define H_Data_Time 1024 `define H_Total_Time 1344 `define V_Bottom_Border 0 `define V_Front_Porch 3 `define V_Sync_Time 6 `define V_Back_Porch 29 `define V_Top_Border 0 `define V_Data_Time 768 `define V_Total_Time 806 `else `endif

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

vga驱动:

`define vga_640_480 `include "vga_para.v" module vga_ctrl( input clk ,//时钟信号 //25.2MHZ input rst_n ,//复位信号 input [23:0] data_disp , output reg [10:0] h_addr ,//数据有效显示区域行地址 output reg [10:0] v_addr ,//数据有效显示区域场地址 output reg vsync , output reg hsync , output reg [7 :0] vga_r , output reg [7 :0] vga_b , output reg [7 :0] vga_g , output wire vga_blk , output wire vga_sync , output reg vga_clk //25.2MHZ ); //参数定义 parameter H_SYNC_START = 1, H_SYNC_STOP = `H_Sync_Time , H_DATA_START = `H_Sync_Time + `H_Back_Porch + `H_Left_Border, H_DATA_STOP = `H_Sync_Time + `H_Back_Porch + `H_Left_Border + `H_Data_Time, V_SYNC_START = 1, V_SYNC_STOP = `V_Sync_Time, V_DATA_START = `V_Sync_Time + `V_Back_Porch + `V_Top_Border, V_DATA_STOP = `V_Sync_Time + `V_Back_Porch + `V_Top_Border + `V_Data_Time; //信号定义 reg [11:0] cnt_h_addr ;//行地址计数器 wire add_h_addr ; wire end_h_addr ; reg [11:0] cnt_v_addr ;//长地址计数器 wire add_v_addr ; wire end_v_addr ; assign vga_sync = 1'b0; assign vga_blk = ~((cnt_h_addr<`H_Front_Porch + `H_Sync_Time + `H_Back_Porch)||(cnt_v_addr<`V_Front_Porch + `V_Sync_Time + `V_Back_Porch)); always@(posedge vga_clk or negedge rst_n)begin if(!rst_n)begin cnt_h_addr <= 12'd0; end else if(add_h_addr)begin if(end_h_addr)begin cnt_h_addr <= 12'd0; end else begin cnt_h_addr <= cnt_h_addr + 12'd1; end end else begin cnt_h_addr <= 12'd0; end end assign add_h_addr = 1'b1; assign end_h_addr = add_h_addr && cnt_h_addr == `H_Total_Time - 1; always@(posedge vga_clk or negedge rst_n)begin if(!rst_n)begin cnt_v_addr <= 12'd0; end else if(add_v_addr)begin if(end_v_addr)begin cnt_v_addr <= 12'd0; end else begin cnt_v_addr <= cnt_v_addr + 12'd1; end end else begin cnt_v_addr <= cnt_v_addr; end end assign add_v_addr = end_h_addr; assign end_v_addr = add_v_addr && cnt_v_addr == `V_Total_Time - 1; //行场同步信号 always@(posedge vga_clk or negedge rst_n)begin if(!rst_n)begin hsync <= 1'b1; end else if(cnt_h_addr == H_SYNC_START - 1)begin hsync <= 1'b0; end else if(cnt_h_addr == H_SYNC_STOP - 1)begin hsync <= 1'b1; end else begin hsync <= hsync; end end always@(posedge vga_clk or negedge rst_n)begin if(!rst_n)begin vsync <= 1'b1; end else if(cnt_v_addr == V_SYNC_START - 1)begin vsync <= 1'b0; end else if(cnt_v_addr == V_SYNC_STOP - 1)begin vsync <= 1'b1; end else begin vsync <= vsync; end end always@(posedge clk or negedge rst_n)begin if(!rst_n)begin vga_clk =0; end else begin vga_clk = ~vga_clk; end end //数据有效显示区域定义 always@(posedge vga_clk or negedge rst_n)begin if(!rst_n)begin h_addr <= 11'd0; end else if((cnt_h_addr >= H_DATA_START - 1) &&( cnt_h_addr <= H_DATA_STOP - 1))begin h_addr <= cnt_h_addr - H_DATA_START - 1; end else begin h_addr <= 11'd0; end end always@(posedge vga_clk or negedge rst_n)begin if(!rst_n)begin v_addr <= 11'd0; end else if((cnt_v_addr >= V_DATA_START - 1) && (cnt_v_addr <= V_DATA_STOP - 1))begin v_addr <= cnt_v_addr - V_DATA_START -1; end else begin v_addr <= 11'd0; end end //显示数据 always@(posedge vga_clk or negedge rst_n)begin if(!rst_n)begin vga_r <= 8'b0; vga_g <= 8'b0; vga_b <= 8'b0; end else if((cnt_h_addr >= H_DATA_START - 1) &&( cnt_h_addr <= H_DATA_STOP - 1) && (cnt_v_addr >= V_DATA_START - 1) && (cnt_v_addr <= V_DATA_STOP - 1))begin vga_r <= data_disp[23:16]; vga_g <= data_disp[15: 8]; vga_b <= data_disp[7 : 0]; end else begin vga_r <= 8'b0; vga_g <= 8'b0; vga_b <= 8'b0; end end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

- 121

- 122

- 123

- 124

- 125

- 126

- 127

- 128

- 129

- 130

- 131

- 132

- 133

- 134

- 135

- 136

- 137

- 138

- 139

- 140

- 141

- 142

- 143

- 144

- 145

- 146

- 147

- 148

- 149

- 150

- 151

- 152

- 153

- 154

- 155

- 156

- 157

- 158

- 159

- 160

- 161

- 162

- 163

- 164

- 165

- 166

- 167

- 168

- 169

- 170

- 171

- 172

- 173

- 174

生成数据:

module data_gen( input clk ,//时钟信号 input rst_n ,//复位信号 input [10:0] h_addr ,//数据有效显示区域地址 input [10:0] v_addr ,//数据有效显示区域地址 output reg [23:0] data_disp ); //参数定义 parameter BLACK = 24'h000000, RED = 24'hFF0000, GREEN = 24'h00FF00, BLUE = 24'h0000FF, YELLOW = 24'hFFFF00, SKY_BULE = 24'h00FFFF, PURPLE = 24'hFF00FF, GREY = 24'hC0C0C0, WIGHT = 24'hFFFFFF; always@(posedge clk or negedge rst_n)begin if(!rst_n)begin data_disp <= BLACK; end else begin case(h_addr) 0 : data_disp <= RED; 80 : data_disp <= GREEN; 160: data_disp <= BLUE; 240: data_disp <= YELLOW; 320: data_disp <= SKY_BULE; 400: data_disp <= PURPLE; 480: data_disp <= GREY; 560: data_disp <= WIGHT; default:data_disp <= data_disp; endcase end end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

vga_top文件:

module vga_top( input clk ,//时钟信号 input rst_n ,//复位信号 output wire vsync , output wire hsync , output wire [7 :0] vga_r , output wire [7 :0] vga_b , output wire [7 :0] vga_g , output vga_blk , output wire vga_sync , output vga_clk ); wire [23:0] data_disp ; wire [10:0] h_addr ; wire [10:0] v_addr ; data_gen u_data_gen( .clk (vga_clk ),//时钟信号 .rst_n (rst_n ),//复位信号 .h_addr (h_addr ),//数据有效显示区域地址 .v_addr (v_addr ),//数据有效显示区域地址 .data_disp (data_disp ) ); vga_ctrl u_vga_ctrl( .clk (clk ),//时钟信号 25.2MHZ .rst_n (rst_n ),//复位信号 .data_disp (data_disp ), .h_addr (h_addr ),//数据有效显示区域行地址 .v_addr (v_addr ),//数据有效显示区域场地址 .vsync (vsync ), .hsync (hsync ), .vga_r (vga_r ), .vga_b (vga_b ), .vga_g (vga_g ), .vga_blk (vga_blk ), .vga_sync (vga_sync ), .vga_clk (vga_clk ) ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

显示效果:

参考链接:

https://blog.csdn.net/qq_45659777/article/details/124834294

https://blog.csdn.net/qq_40147893/article/details/108342484