- 1【大数据】【Hadoop】2、Hadoop安装_win如何使用wget下载handoop

- 2vim使用教程图文教程(零基础超详细)_vim教程

- 3Stable Diffusion AnimateDiff | 最火文本生成视频插件_animatediff模型下载

- 4mysql ERROR 1129 : unblock with ‘mysqladmin flush-hosts‘_unblock with 'mysqladmin flush-hosts

- 5解决 CondaHTTPError 问题(必定有效版)

- 6AI绘画技巧分享 如何快速生成多个电商图

- 7maven项目报错Non-resolvable parent POM for com.example:demo-1:0.0.1-SNAPSHOT: Failure to transfer org.sp_[fatal] non-resolvable parent pom for com.example:

- 835岁以后的程序员出路在哪里?深夜思考

- 9python将xml格式文件转成png或者pdf格式

- 10人工智能普及之JAVA & AI 课程第一课_java ai

vivado使用方法(初级)_vivado使用教程

赞

踩

1 创建新工程

1.1 工程创建

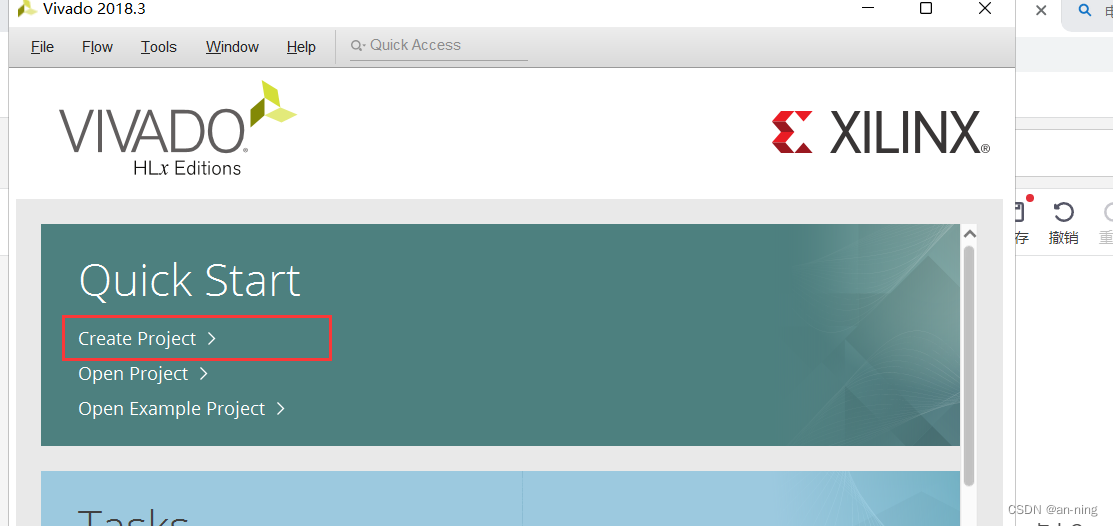

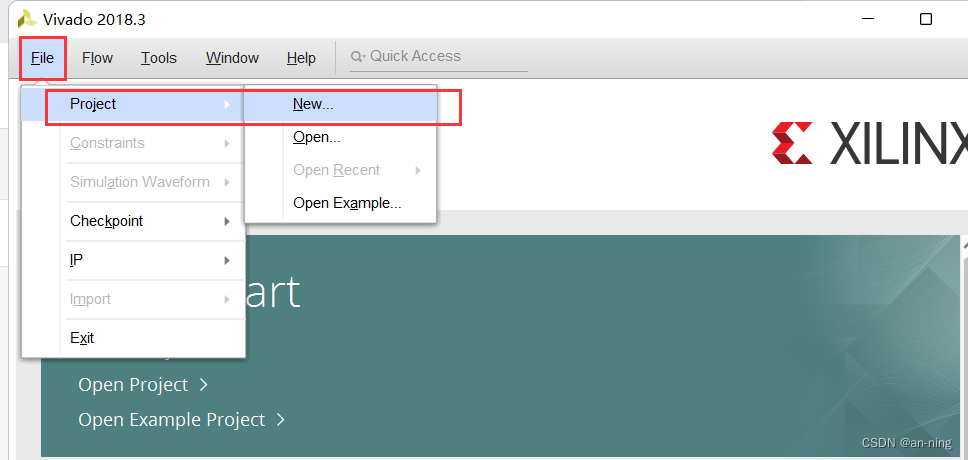

1、首先打开Vavido软件,点击Creat Project或者在File——>Project——>New里面进行新工程的创建

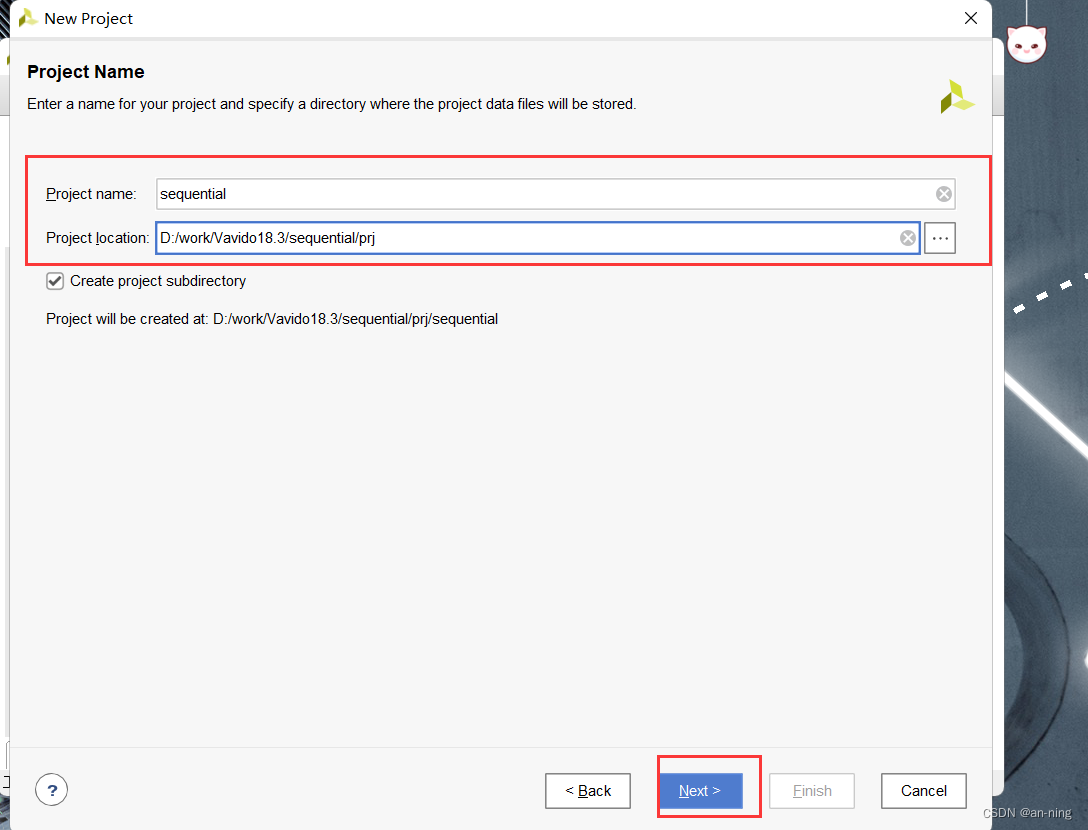

2、然后在弹出的界面上点击Next进入下一个界面进行项目的命名及保存位置的选择(注意保存路径不能有中文否则后面可能会引起一些不必要的错误),然后进行下一步

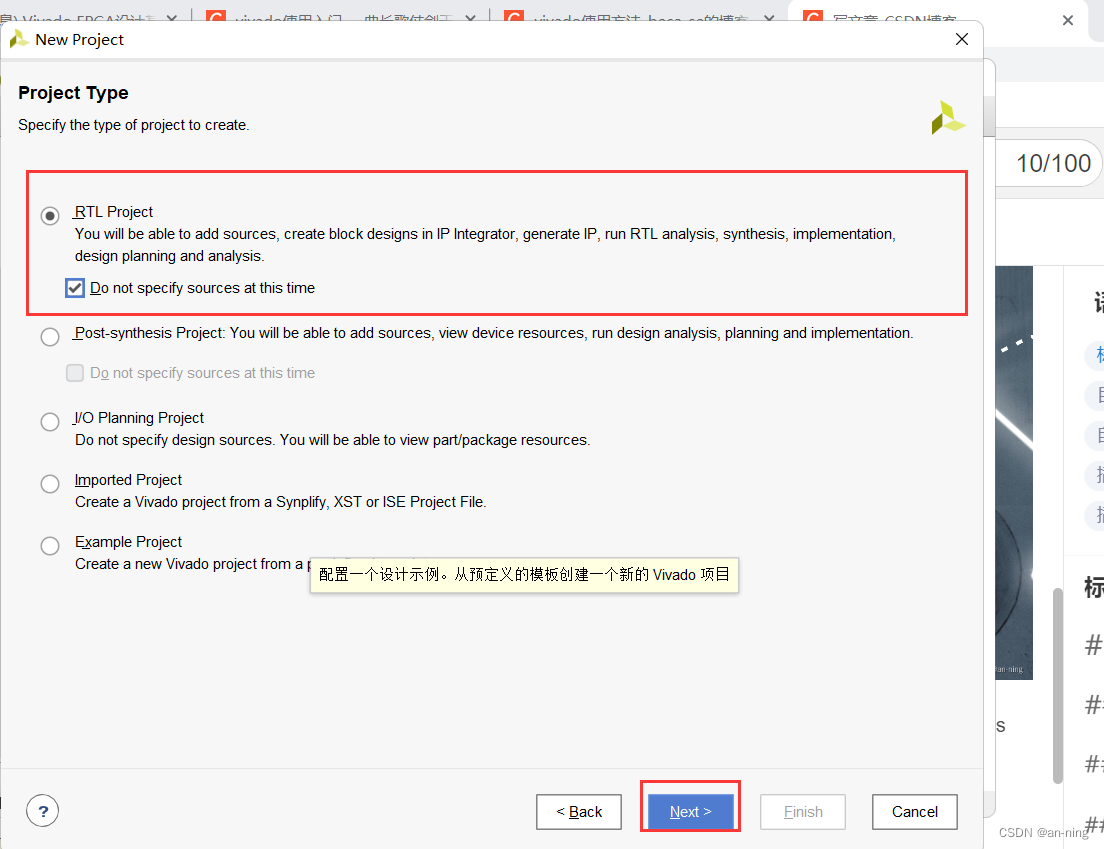

3、选择RTL Project (一般为RTL工程),此时把Do not specify at this time勾上,表示在新建工程时不去指定源文件

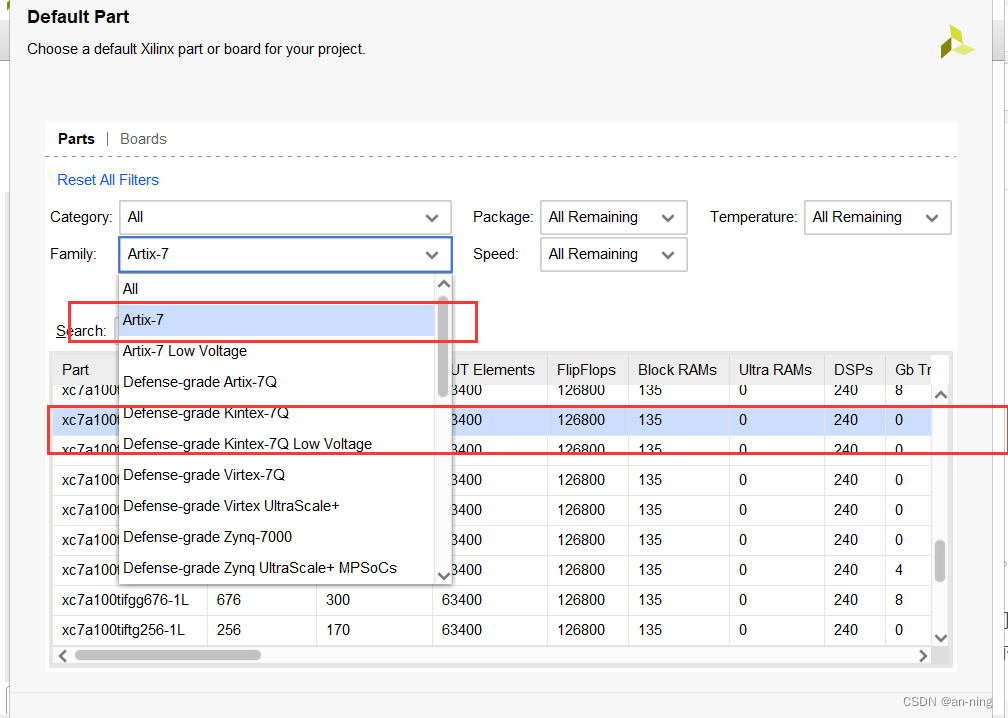

4、接下来选择开发板型号,Parts表示器件,Boards表示板子,器件可以根据系列去选,也可以直接在Search栏搜索器件型号。器件的选择根据你的FPGA芯片来定,此处我们先随便选择一个

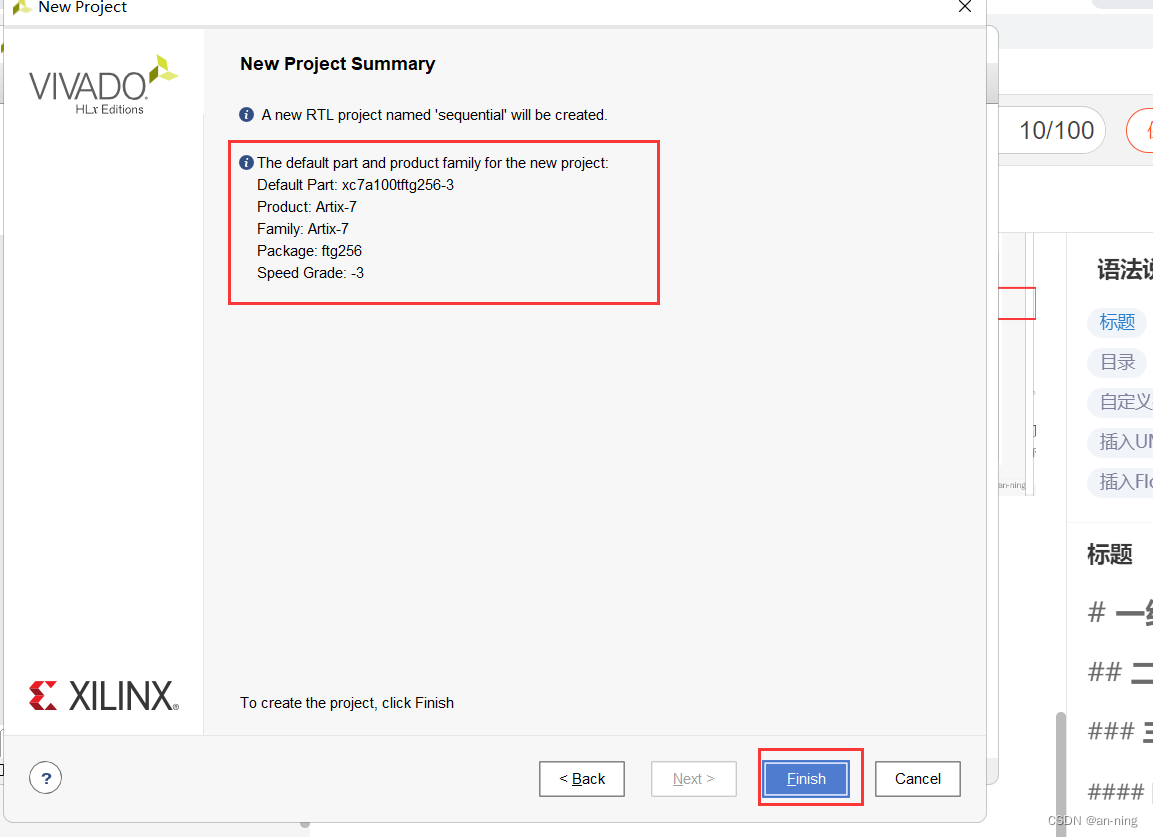

5、确认后点击Finish完成整个工程项目的创建

1.2 新建Verilog文件

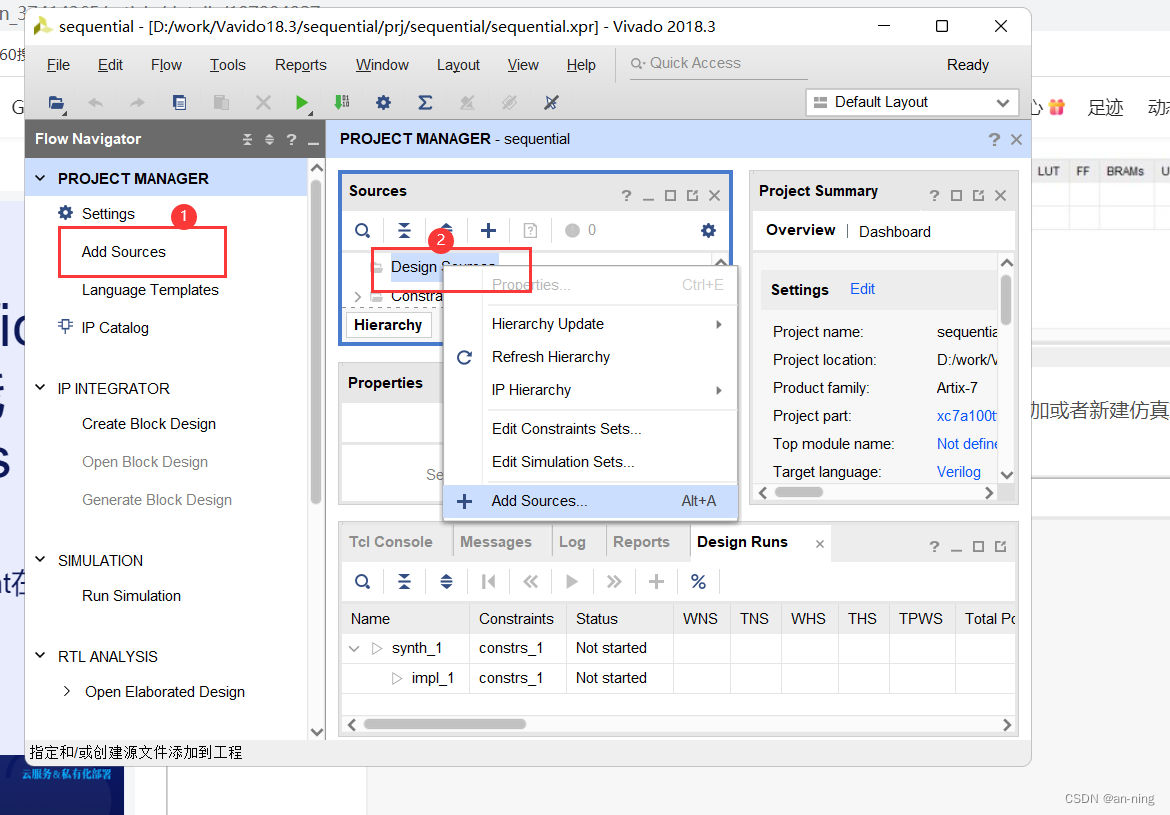

1、新建Verilog文件,直接点击1处或者右键2处后点击Add Sources进行Verilog文件的创建

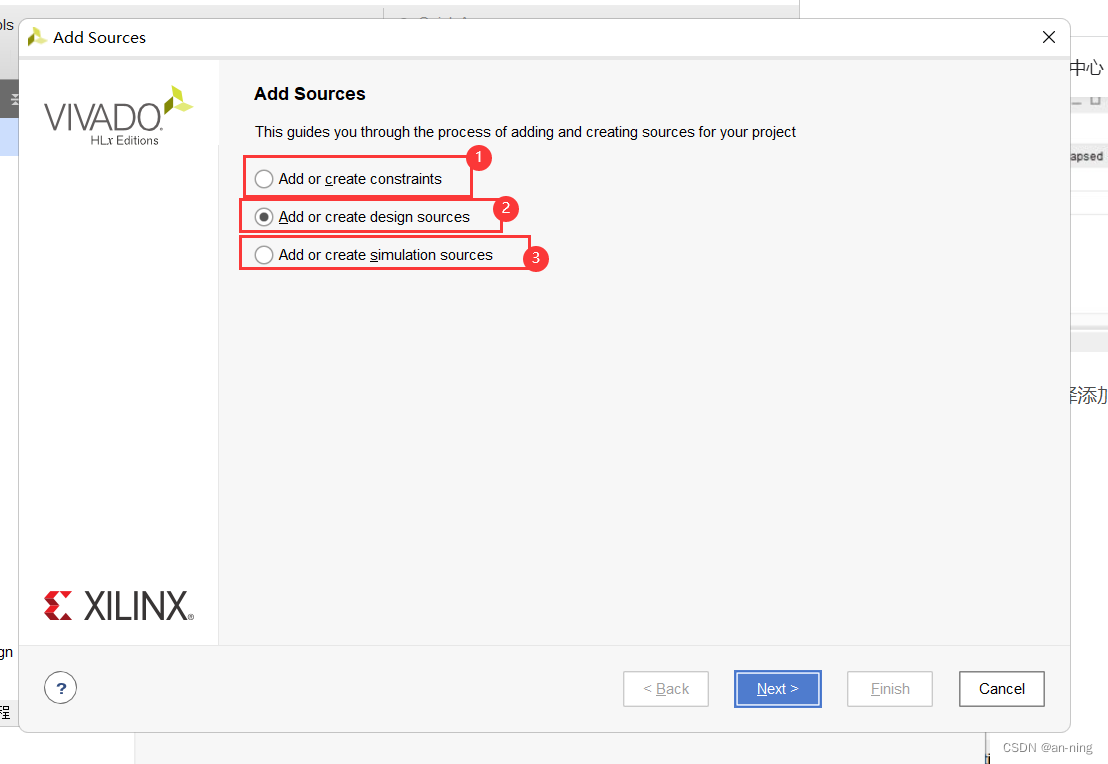

2、选择add or creat design source,其中1为创建约束文件;2为创建设计文件;3为创建工程仿真文件,因此我们存储选择第二个就可以了

3、然后选择Create File,若已有文件,则选择Add File添加文件即可

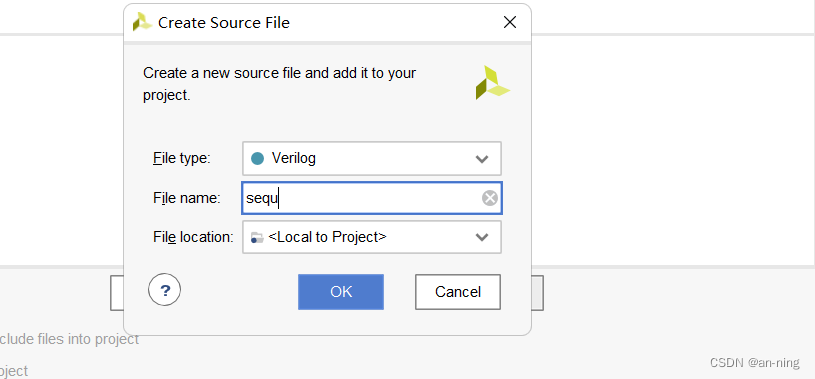

4、对文件进行命名与路径的选择(默认存放在工程默认路径),文件类型(File type)一般选择为Verilog,如果你用的是其它硬件描述语言,则选择你用的语言类型,然后点击Finish完成命名

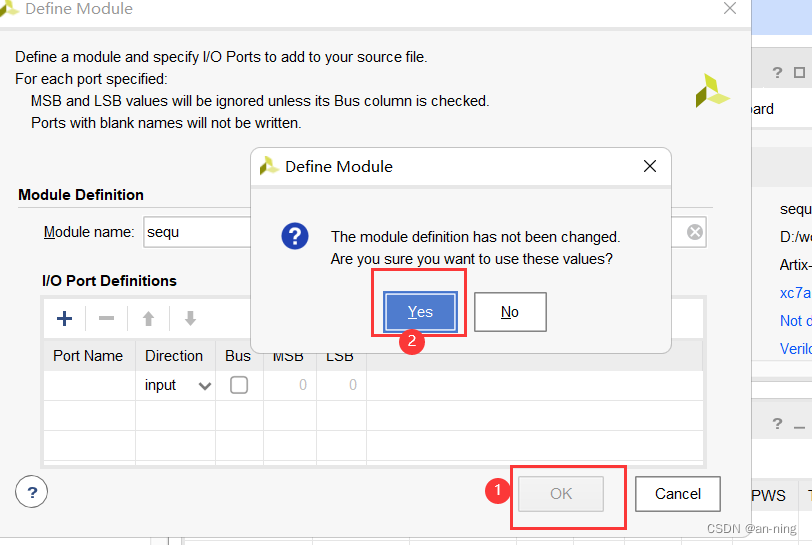

5、在弹出的对话框里一次选择OK,Yes完成设计文件的新建

6、然后在Sources里面就可以看到刚才新建的设计文件,双击打开即可在右边的代码编辑区进行代码的编写

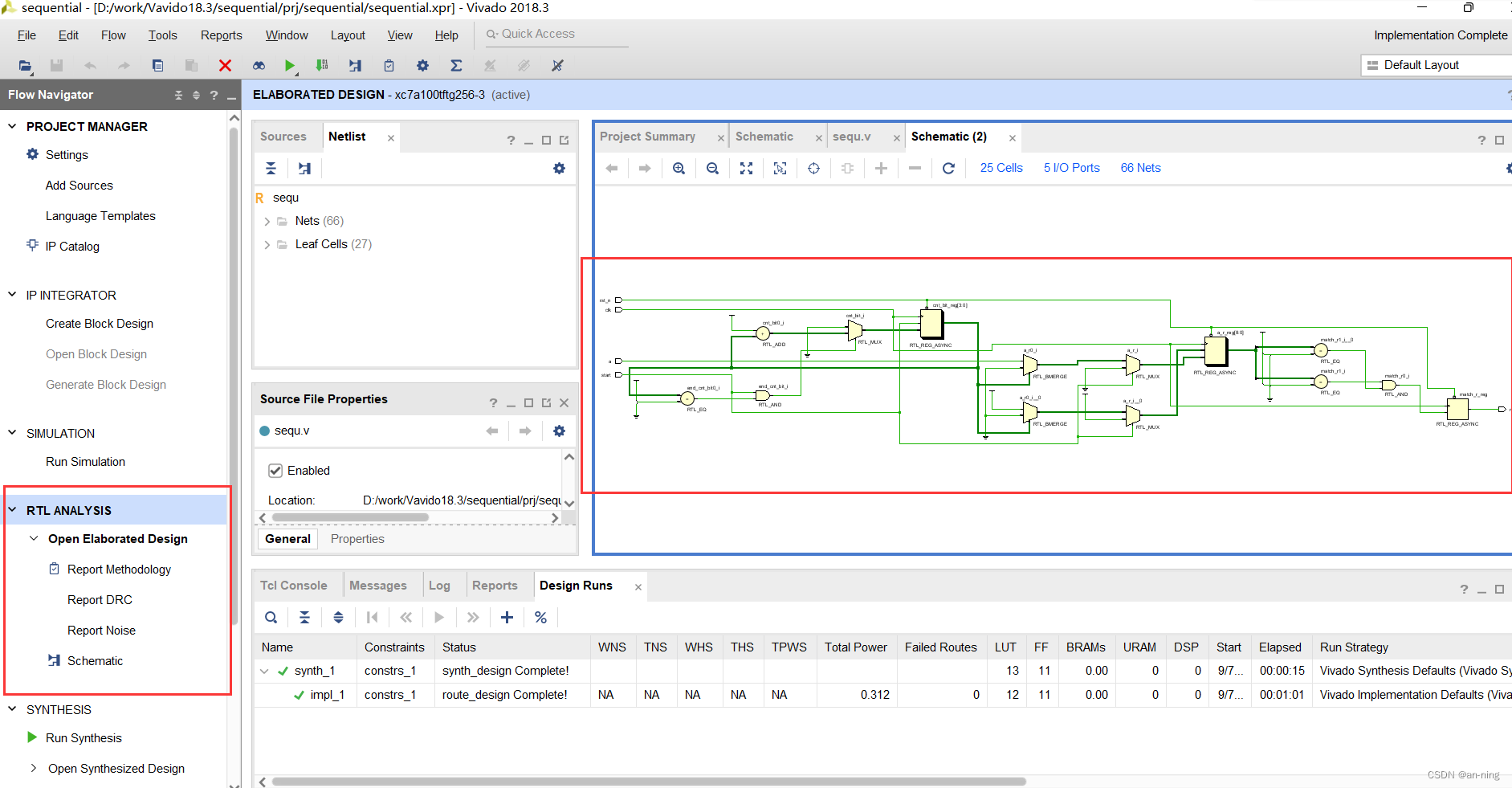

7、运行后查看RTL原理图:在Flow Navigator 下点击RTL ANALYSIS -> Open Elaborated Design -> Schematic

1.3 仿真

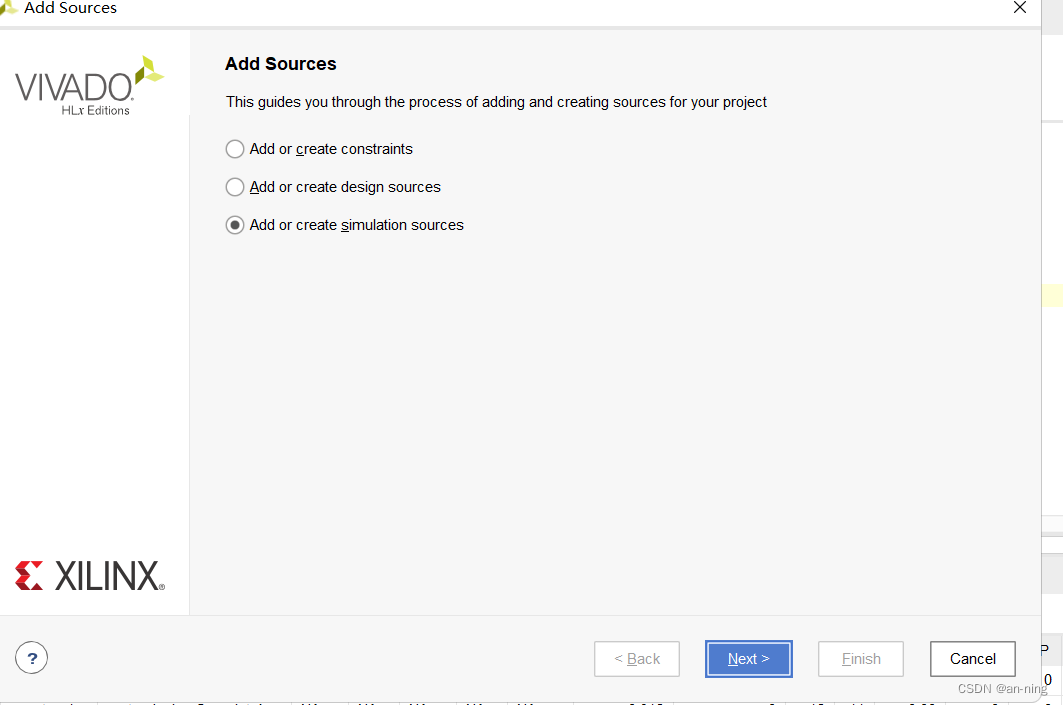

1、新建测试文件,和新建设计文件几乎差不多,只是在这里选择的是Add or create simulation sources

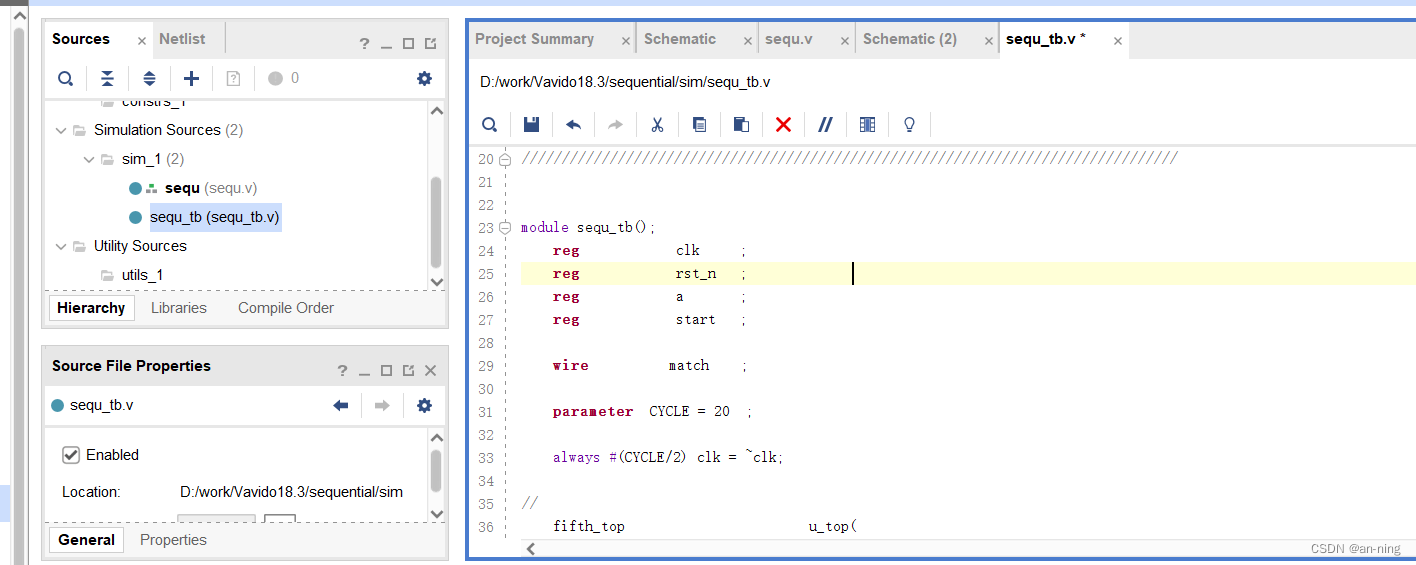

2、同样在代码编辑区完成测试代码的编写

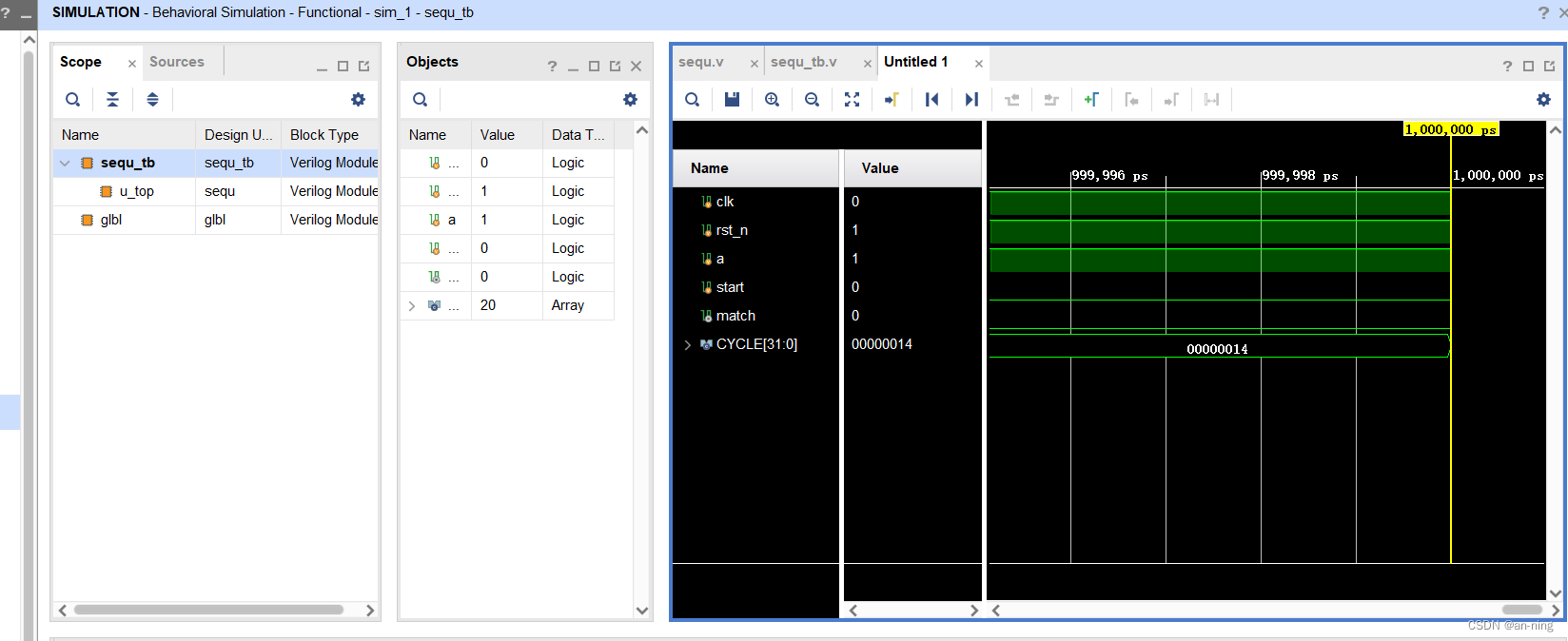

3、 在Flow Navigator界面下点击 Run Simulation -> Run Behavioral Simultion。如果代码没有错误,则一会儿将会在右边出现如下图所示的波形窗口。