- 1windows mongoDB备份工具使用_failed: error parsing query as extended json: inva

- 2【Redis】Redis是什么、能干什么、主要功能和工作原理的详细讲解_redis是干嘛的

- 3api接口文档_接口文档示例

- 4机器学习每周挑战——二手车车辆信息&交易售价数据

- 5STM32使用定时器的捕获比较功能输出PWM波,并且实现呼吸灯的效果bjtu

- 6Flink 解析(一):基础概念解析_能讲flink的解析直接拿出来

- 7如何在织梦中使用SMTP验证发送邮件_dede 配置qqsmtp

- 8家政上门预约服务小程序源码+前端后端_上门小程序源码

- 9COPU陆首群教授应邀在开放原子全球开源峰会上做主旨演讲_开源 大会 发言

- 10侯捷C++ STL:哈希表(unordered_set,unordered_multiset,unordered_map,unordered_multimap)的底层实现_c++中三种哈希表的底层实现

FPGA_学习_05_管脚约束_fpga管脚约束

赞

踩

前言:就初学管脚约束相关知识而言,内容还不足以构成饱满的文章。 但管脚约束是一个独立的内容,它是值得有一篇单独的博客的。若后续学习了管脚约束新的知识,则进一步扩充本篇博客内容。

1 XDC基础语法

Vivado的管脚约束文件用XDC 编写的,下面介绍XDC基础语法,普通IO口只需约束引脚号和电压。

引脚号约束:

set_property PACKAGE_PIN “引脚编号” [ get_ports “端口名称” ]

电平信号约束:

set_property IOSTANDARD “电压” [ get_ports “端口名称” ]

这里需要注意文字的大小写,端口名称是数组的话用{}括起来,端口名称必须和源代码中的名字一致,且端口名字不能和关键字一样。

以 led[0]的约束为例:

set_property PACKAGE_PIN P15 [ get_ports {led[0]} ]

// 绑定 led[0]的管脚

set_property IOSTANDARD LVCMOS33 [ get_ports {led[0]} ]

// 设置 led[0]的电平约束。

如果端口名称是数组的话,电平信号约束可以批量化操作

set_property IOSTANDARD LVCMOS33 [ get_ports {led[*]} ]

// 约束led数组所有的电平。

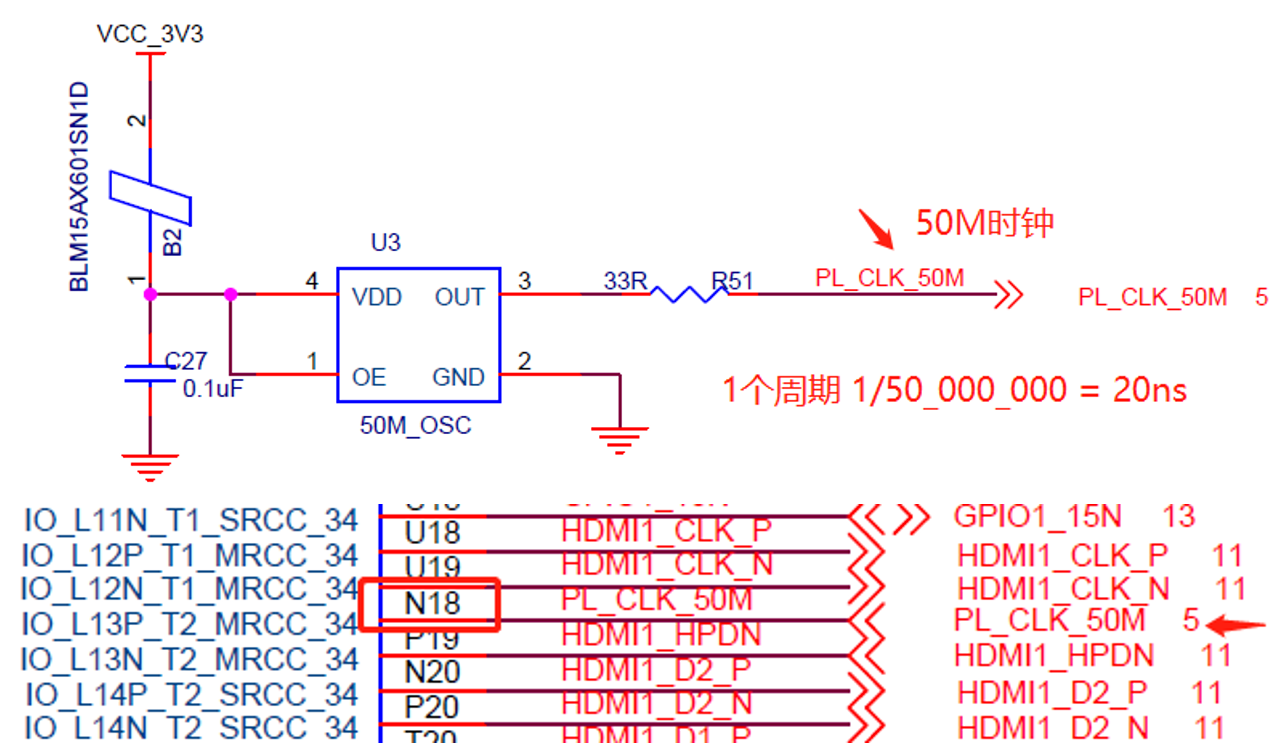

另外系统的主时钟也需要添加一行约束。

create_clock -period 20.000 [ get_ports clk ]

set_property PACKAGE_PIN N18 [ get_ports clk ]

和时钟相关的原理图如下所示:

上述约束语句对应的模块接口定义如下:

- module led(

- input wire clk,

- output wire [1:0] led

- );

- endmodule

再次强调例子中用的端口名称是clk和led,这是与 模块源码的接口定义对应的。

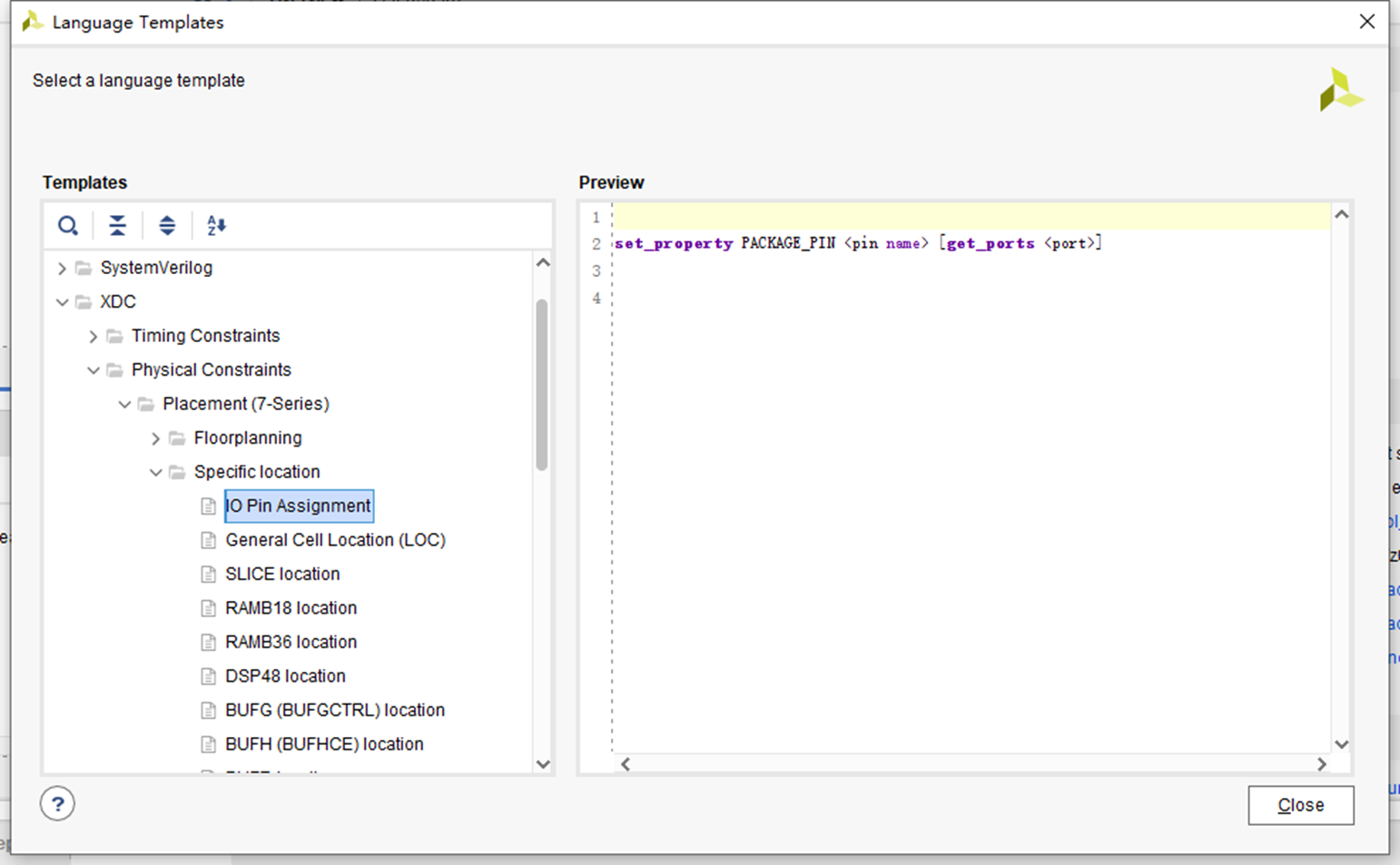

2 XDC语言模板查询方法

相关内容,可以在Vivado的Tools→Language Templates里面学习

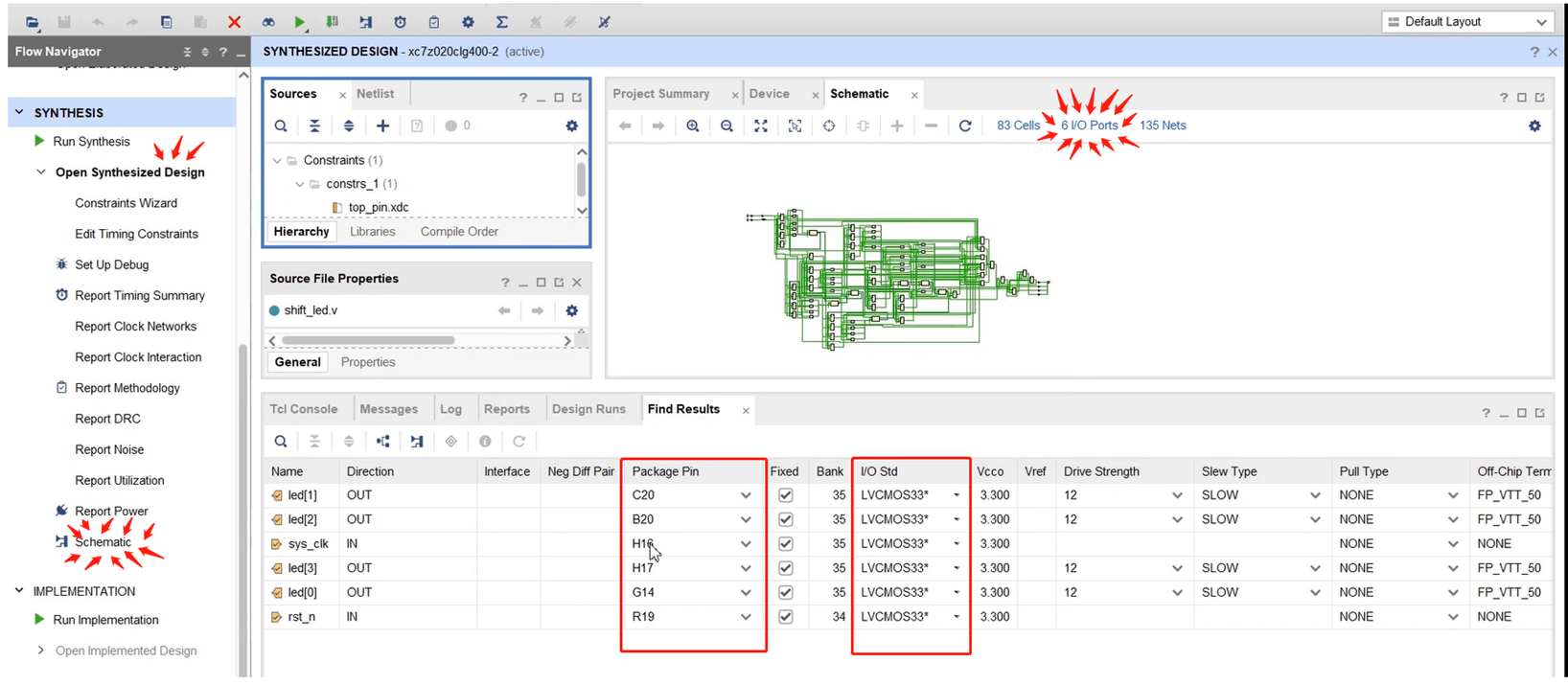

3 管脚约束UI操作

约束文件也可以不用手写,直接用操作完成。

流程:源码写好,先综合(Synthesis),之后点击Synthesis → Open Synthesized Design → Schematic → n I/O Ports,就可以图形化操作管脚约束了。

关于管脚约束的知识应该还有到目前为止没有碰到的内容,后续遇到了再补充,未完待续…

愿我们共同进步! 感谢您的阅读,欢迎留言讨论、收藏、点赞、分享。