- 1Vue+element-plus展开/收回功能_elementplus作业书控制全部展开和全部关闭

- 2kafka如何保证消息的顺序性_kafka消息顺序性

- 3Git不同分支代码合并_git不同版本代码合并

- 4mumu配置_mumu模拟器如何安装ca证书

- 5【NLP】模型压缩与蒸馏!BERT的忒修斯船

- 6centos 中使用 kubekey 安装 k8s v1.22.12 支持 GPU 调用

- 7三大深度学习生成模型:VAE、GAN及其变种_vae gan transformer

- 8优雅的使用 Dockerfile 定制镜像_dockerfile指定镜像名称

- 9基于javaweb+mysql的ssm网上果蔬商城水果蔬菜商城系统(java+ssm+mysql+tomcat+jsp)

- 10通过城市名,实现按照A,B,C,D...排序

从零开始利用MATLAB进行FPGA设计(一):建立脉冲检测模型的Simulink模型2_matlab fpga

赞

踩

目录

文章灵感来源于MATLAB官方免费教程:HDL Coder Self-Guided Tutorial

考虑到MATLAB官网的英文看着慢,再加上视频讲解老印浓浓的咖喱味,我决定记录利用MATLAB&Simulink&SystemGenerator进行FPGA数字信号处理的学习过程。

往期回顾:

从零开始利用MATLAB进行FPGA设计(一):建立脉冲检测模型的Simulink模型1

上一期分析了MATLAB的黄金算法原理,这一期进行Simulink模块分析。

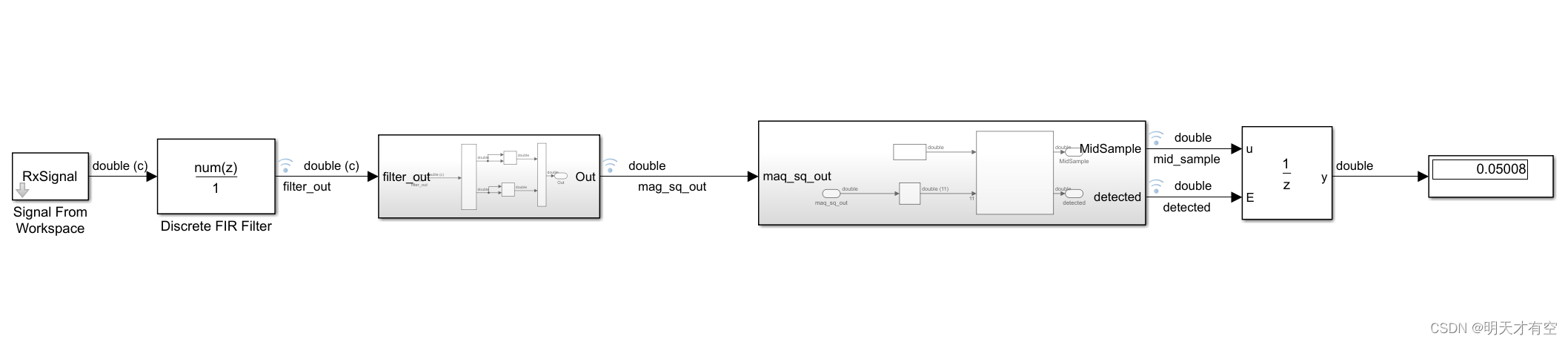

1.模块的总体结构

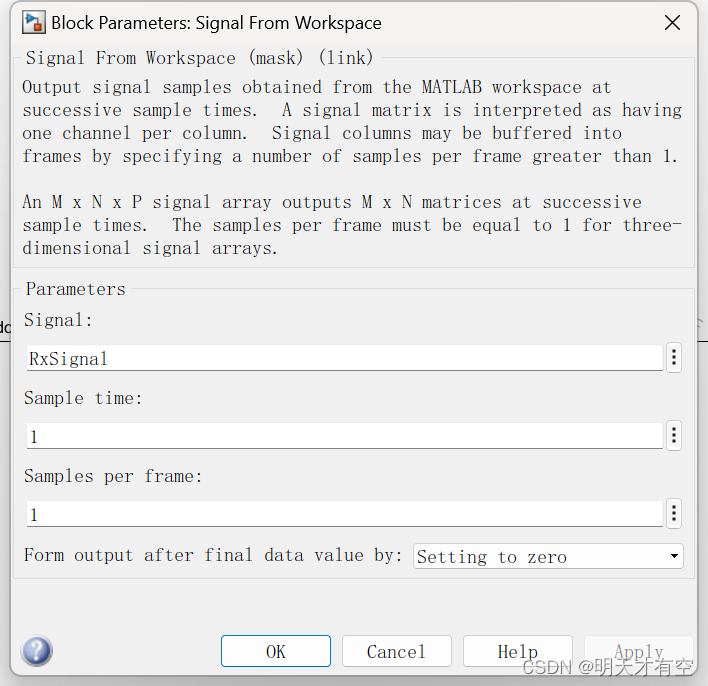

1.1从工作空间导入输入信号

Ctrl+Shift+L呼出Simulink模块库,查找Signal From Workspace,右击后添加到Simulink,双击修改属性:

1.2FIR滤波器

有限冲激响应滤波器可以简单的理解成高通/低通/带通/带阻滤波器,在频域上对通过的信号频率进行限制。

本例中使用的滤波器为直接型滤波器结构:

使用CorrFilter作为匹配滤波器的滤波器系数,系数的计算方法为:

- 先将发送端的信号取共轭。

- 然后将其进行翻转,即反转信号的顺序。

- 最后将其除以信号模式的长度,以确保匹配滤波器的输出的幅度在一定程度上不受信号长度的影响。

MATLAB生成方法可见上一篇博客。

在现代的数字通信中,如果信号遇到的干扰是高斯白噪声,那么匹配滤波器是系统接收端的标配。匹配滤波器的设计准则是使滤波器在某一特定时刻达到最大(一个线性系统的频率响应函数为输入信号的复共轭时,其输出信号的信噪比达到最大)。

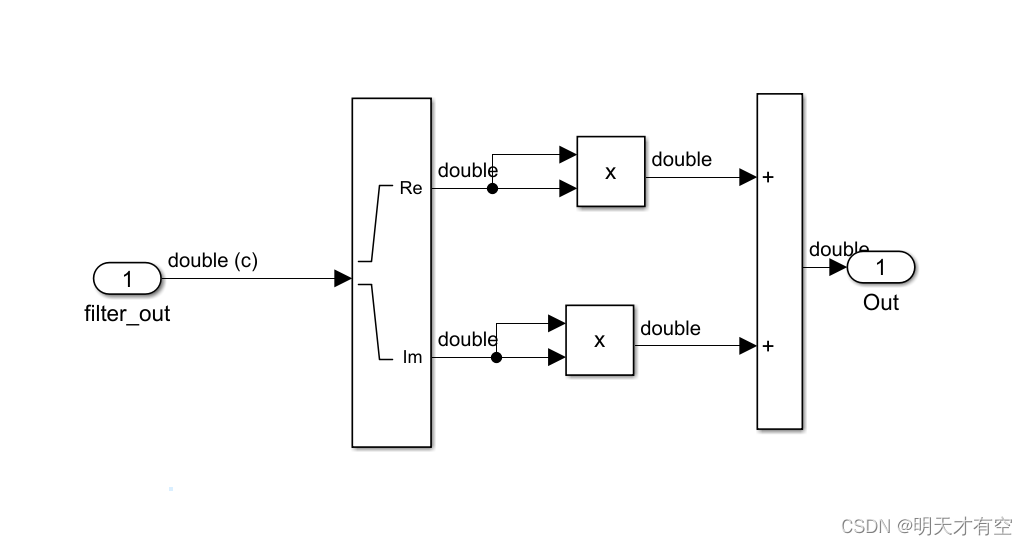

2.Subsystem

滤波器的输出信号输入Complex to Real-Imag 模块分离虚部和实部,通过product模块对其分别进行平方,通过add模块重新组合后输出。该模块的主要作用是避免开方操作,节省算力。

3.MATLAB Function

Tapped Delay (抽头延迟)模块将输入延迟11个采样周期,并为每个延迟提供一个输出。第一个输出延迟11个采样周期,第二个输出延迟10个采样周期,以此类推。

fcn中的函数为:

- function [MidSample,detected] = fcn(threshold,DataBuff,WindowLen)

- MidIdx = ceil(WindowLen/2);

- % Compare each value in the window to the middle sample via subtraction

- MidSample = DataBuff(MidIdx);

- CompareOut = DataBuff - MidSample; % this is a vector

- % if all values in the result are negative and the middle sample is

- % greater than a threshold, it is a local max

- if all(CompareOut <= 0) && (MidSample > threshold)

- detected = 1;

- else

- detected = 0;

- end

MIdIdx表示窗口中的中间索引,由于WindowLen是一个奇数,为了确保中心点用ceil函数向上取整。

将窗口中的每个值和中间值进行比较,如果中间样本值大于阈值且所有结果都为负,则将这个值作为局部最大值。

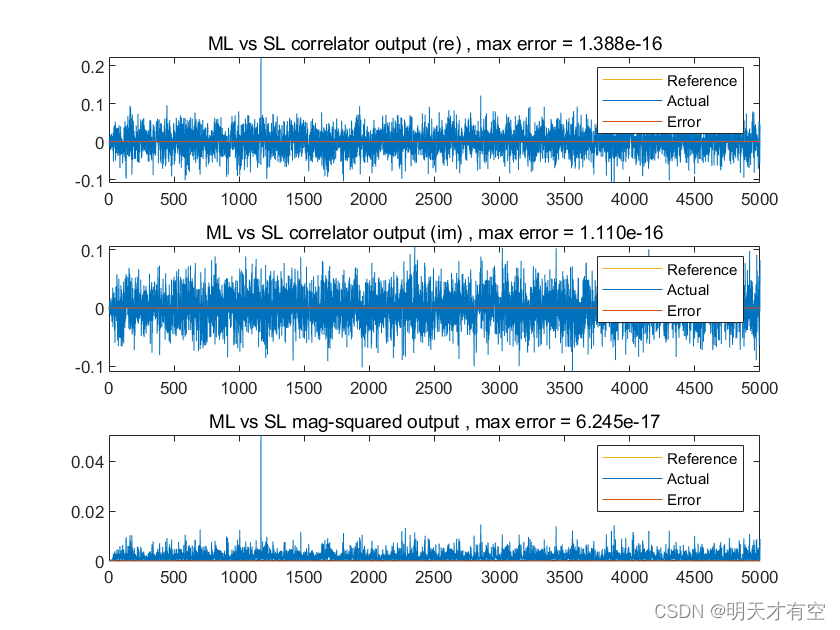

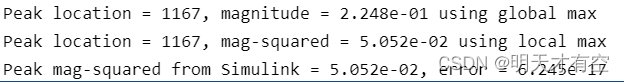

可以看到模块化设计和算法设计的误差为浮点数,效果一致。