- 1python中argsort_浅析python中numpy包中的argsort函数的使用

- 2PyCharm下载安装_pycharmxiazaianzhaung

- 3全屋智能,华为和小米的优劣势在哪?_华为智能 缺点

- 4编写ChatGPT指令(Prompt)的万能模板以及使用示例!_chagpt如何写propt

- 5【Linux】Linux下centos更换国内yum源_centos 6 yum更新源

- 6【数据结构】拓扑排序的实现_为什么拓扑排序中,可以使用栈或者队列来暂存度为0的顶点

- 7二叉树的先序、中序、后序以及层次遍历_先序遍历

- 8git:一、GIT介绍+安装+全局配置+基础操作_请确保本地完成了 git 的全局配置

- 9软件测试面试题_每天一道软件测试面试题系列 (六)_如何提交高质量的软件缺陷(Bug)记录,Web项目中的安全测试怎么测?

- 10python实现刷问卷星份数(面向对象)_问卷星python刷问卷

Quartus II(13.1)如何新建工程+仿真+硬件 异步加载计数器为例_quartus ii仿真

赞

踩

EDA课程所需软件,用过的软件太多了,怕自己以后用到的时候记忆模糊,就决定简单写一个(很详细)新建工程和仿真的过程,这也是我的第一个博客,可能存在很多问题,欢迎指出。种一棵树最好的时间是十年前,其次就是现在。加油!

我习惯创建一个项目前先建新文件夹。

如下图所示,在E盘下新建了一个EDA文件夹,里面创建了两个工程文件。(因为要做两个作业呜呜呜)

一 正式开始创建工程

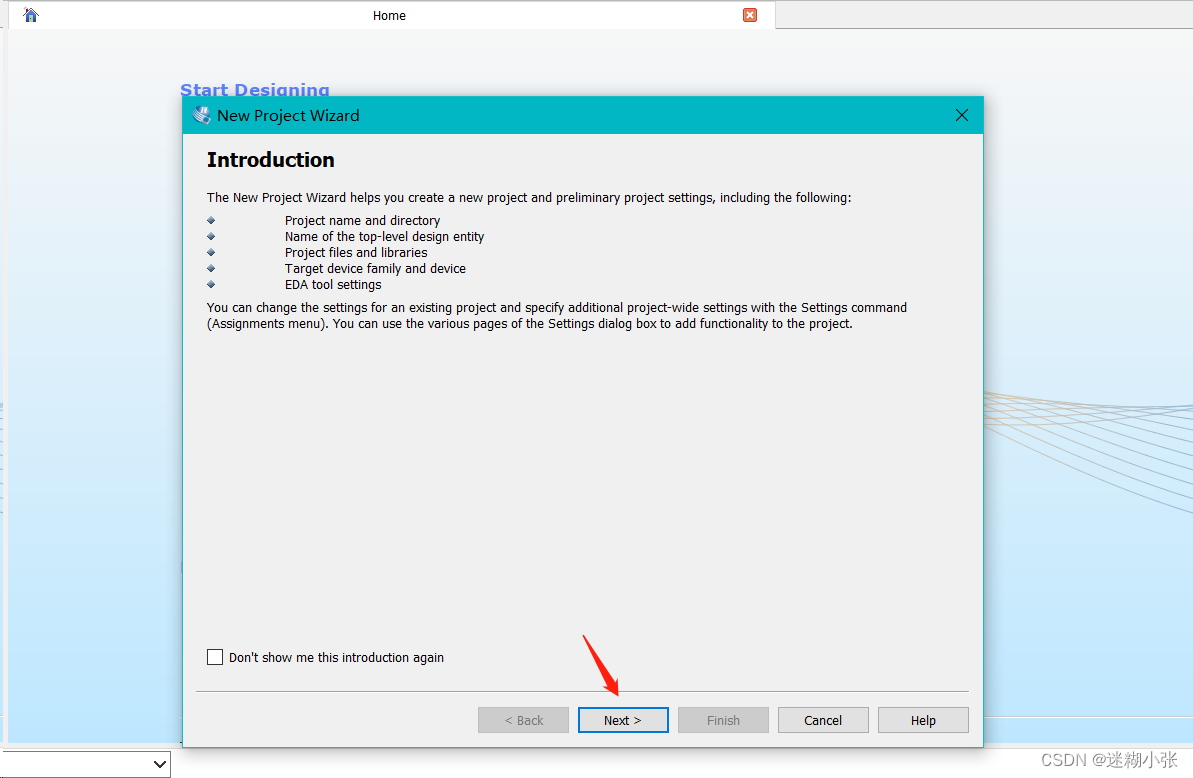

1.打开该软件页面是这样的,点击New Project Wizard(如下图红色箭头所示)

2.弹出窗口如下图所示,点击Next

3.第一行点后面三个点选择路径,即工程所在文件(千万不要出现中文,因为识别不了)

图中第二行写工程名称,第三行紧接着会自动识别,一定不要把工程名称输错,不然后面会报错。

然后点击Next。

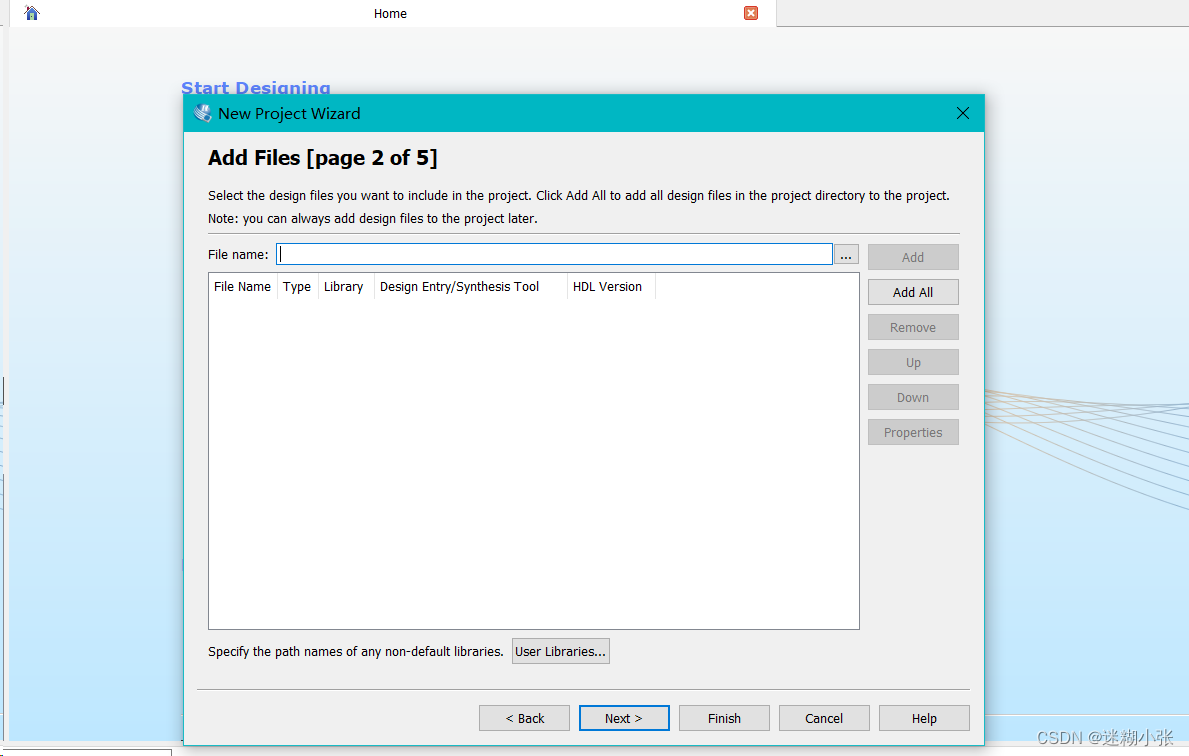

4.这个可以不填写,点击Next。

5.红色箭头输入自己手里面有的开发板,没有的话就别动它了,蓝色箭头点该行后边倒三角,选择FPGA,点击Next。

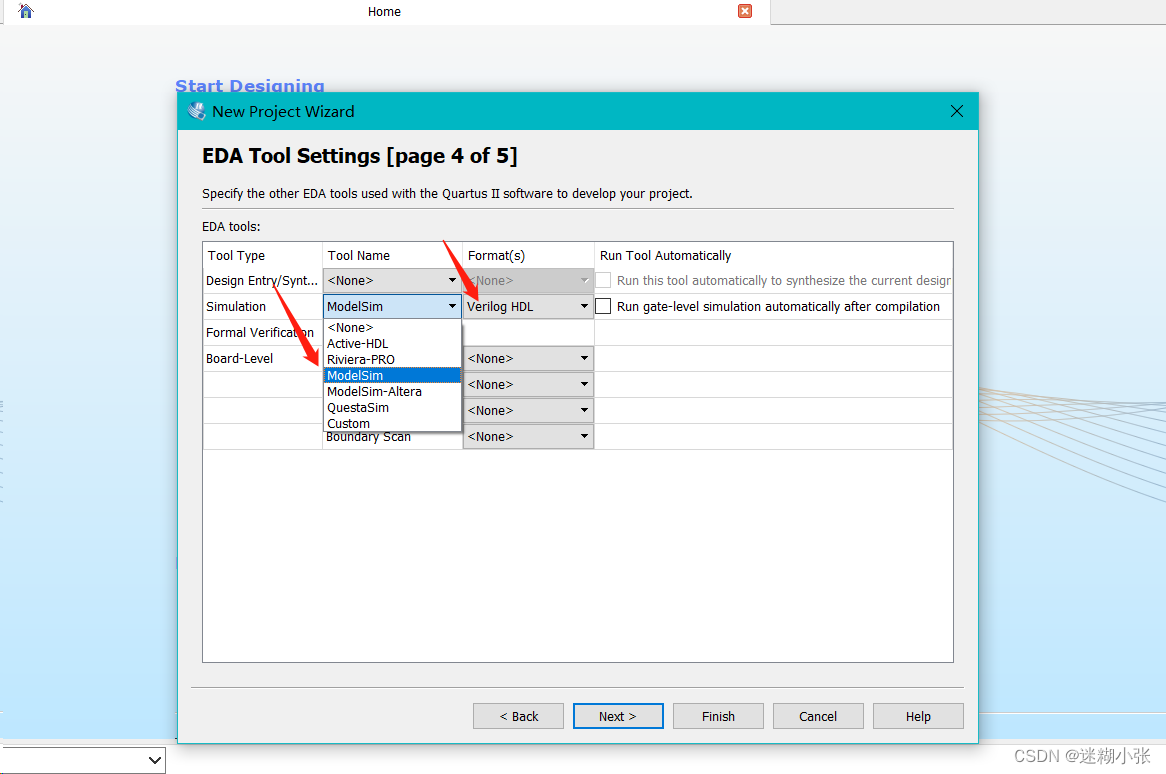

6.仿真选择modelism,右侧选择Verilog HDL,一般应该不用改,点击Next。

7.出现下面这个界面,点击Finish。

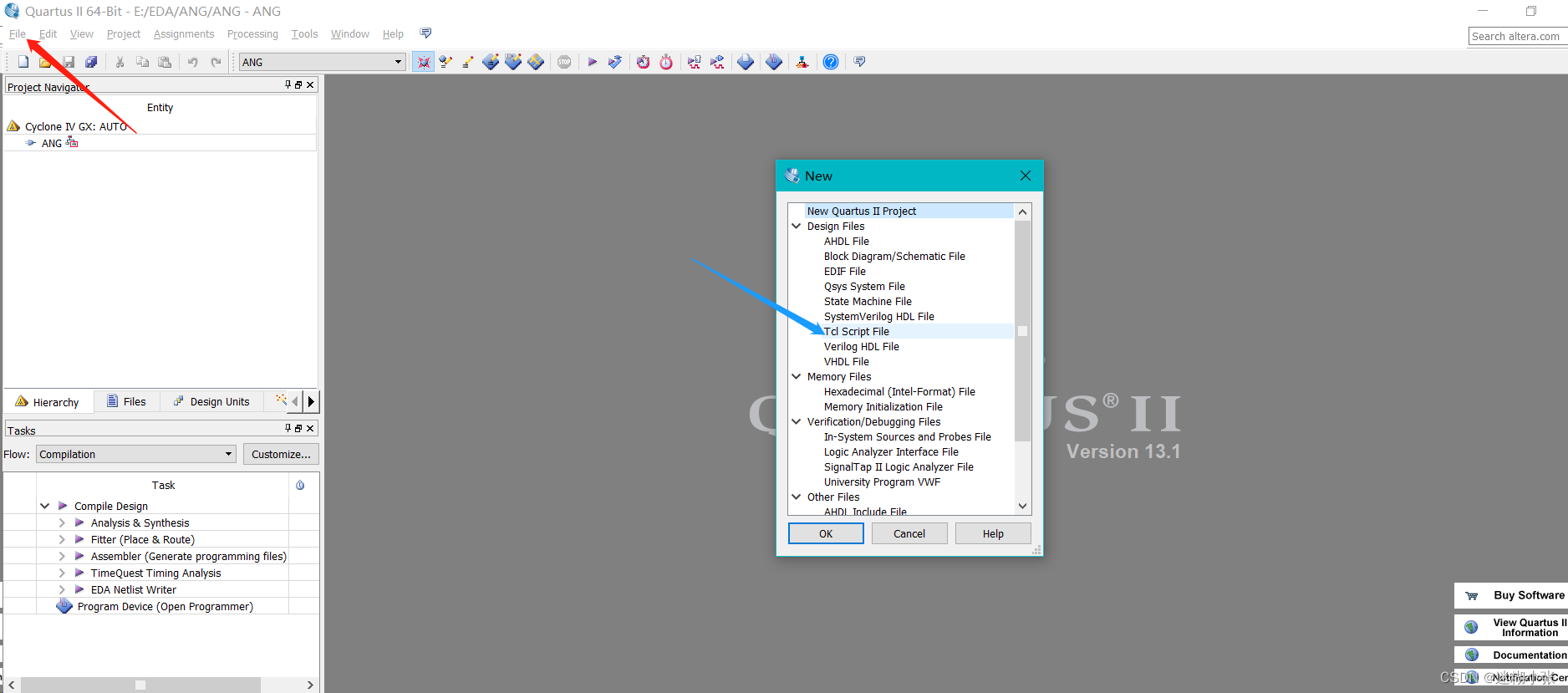

8.点击File-New(红色箭头位置),出现蓝色箭头所在位置弹窗,选中箭头所指即Verlog HDL File

点击OK。

9.然后就可以编写代码啦,一定要注意红色箭头位置一定要是自己工程所在的名称,刚开始学的时候,参考书上的代码照抄,名称也不改,然后编译错误还不知道哪错了!!!!!(切记切记,因为我傻同学犯这个错误!!!!)

点击蓝色箭头所指图标,进行编译。

代码放在这里啦!

- module ANG (CLK,PM,D,DOUT,RST);

- input CLK;

- input RST;

- input [3:0] D;

- output PM;

- output[3:0] DOUT;

- reg[3:0] Q1;

- reg FULL;

- (* synthesis,probe_port,keep*) wire LD;

- always @(posedge CLK or posedge LD or negedge RST)

- if (!RST) begin Q1<=0; FULL<=0; end

- else if (LD) begin Q1<=D; FULL<=0; end

- else begin Q1<=Q1+1; FULL<=0; end

- assign LD=(Q1==4'B0000);

- assign PM=FULL;

- assign DOUT=Q1;

- endmodule

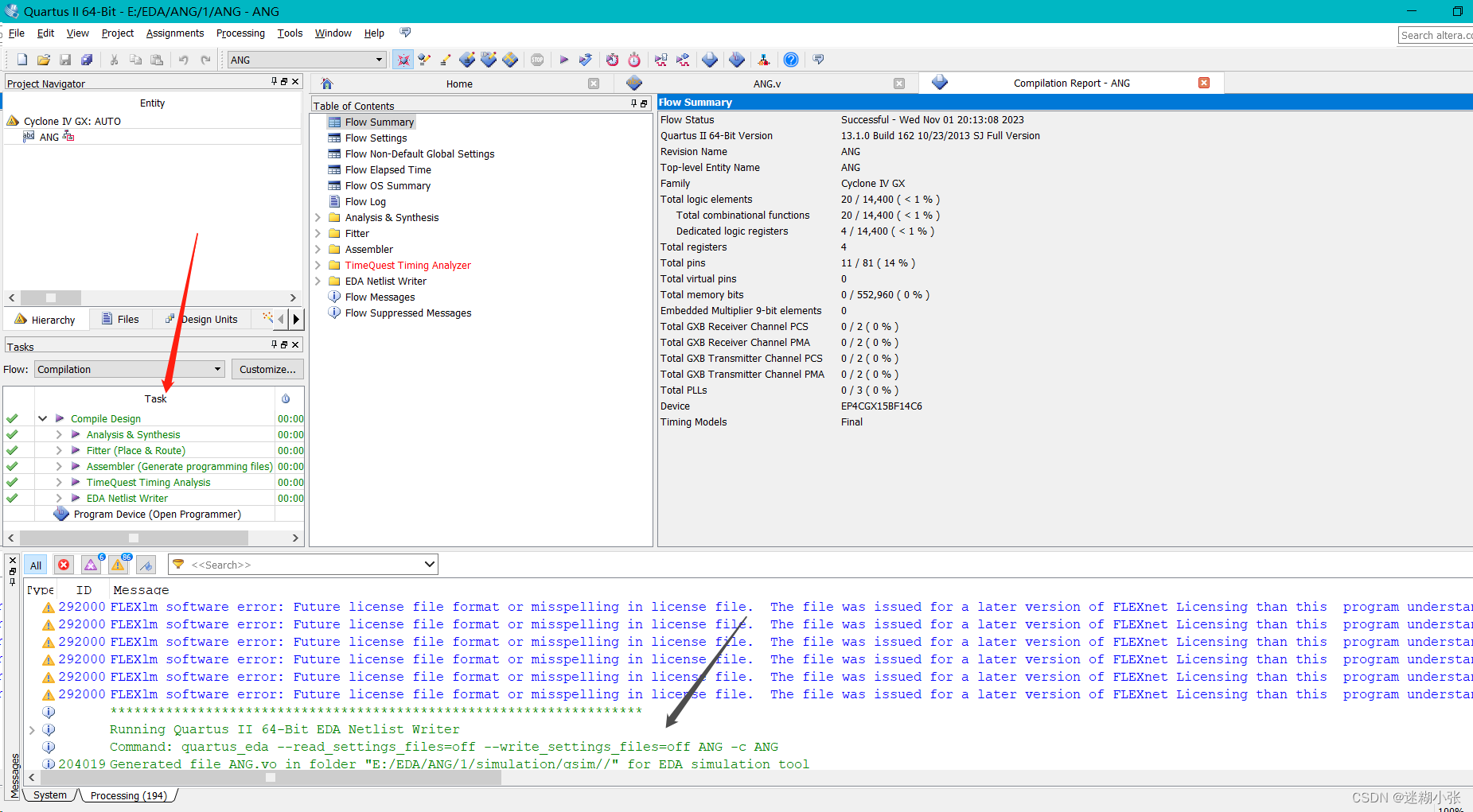

10.红色箭头所指地方全是绿色对勾说明编译成功,否则会有红色×,最底下灰色箭头那会有红色错误改正提示。

二 波形仿真

1.点击File-New,在弹出窗口中点击VWF(蓝色箭头)点击OK。

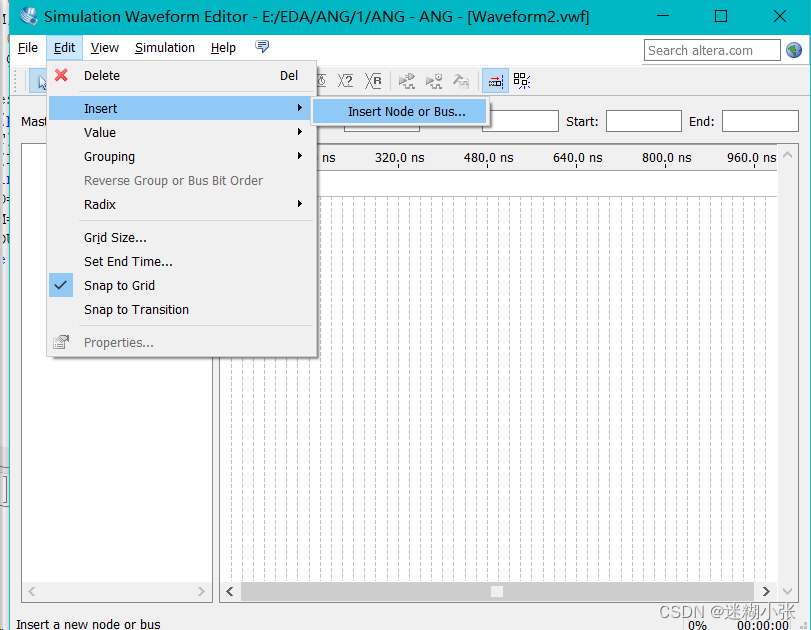

2. 会弹出这个下图所示窗口,点击Edit-Insert-Insert Node

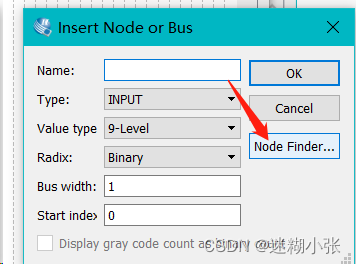

3. 弹出如下窗口,点击红色箭头所指。

4.弹出如下窗口,点击List(红色),然后导入你想仿真的数据挪到右边,蓝色所指即全部从左边移到右边。点击OK。

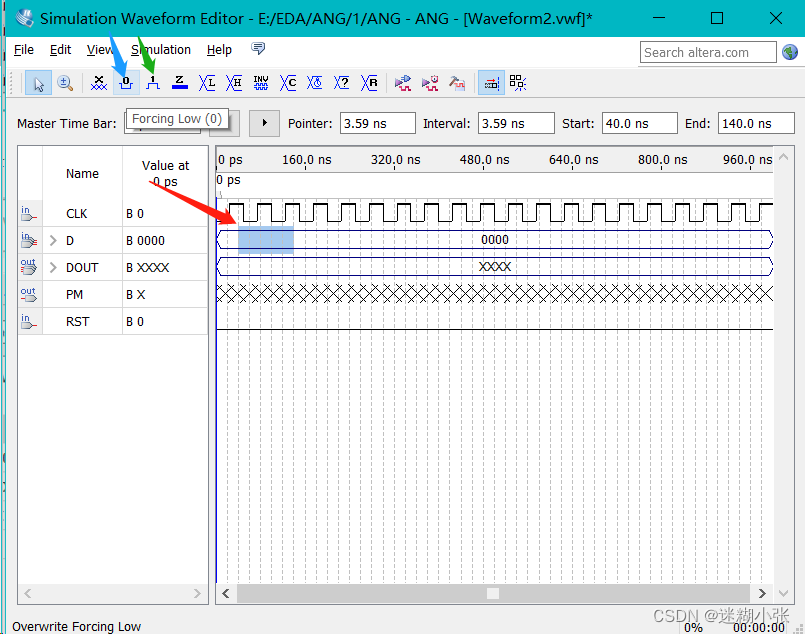

5.按照红蓝绿箭头依次操作。(红:选中引脚;蓝:给予连续脉冲;绿:可以改脉冲周期)

6.可以像上一步一样给予连续高低电平信号,也可如下图所示,红选中,蓝给予持续低电平,红选中,绿给予才继续高电平。(只随意给输出信号,输入信号是运行出来的)

7.点击如下图红色箭头所指图标,会弹出让你保存,保存就行,(最好和之前代码在同一文件夹下,不乱)

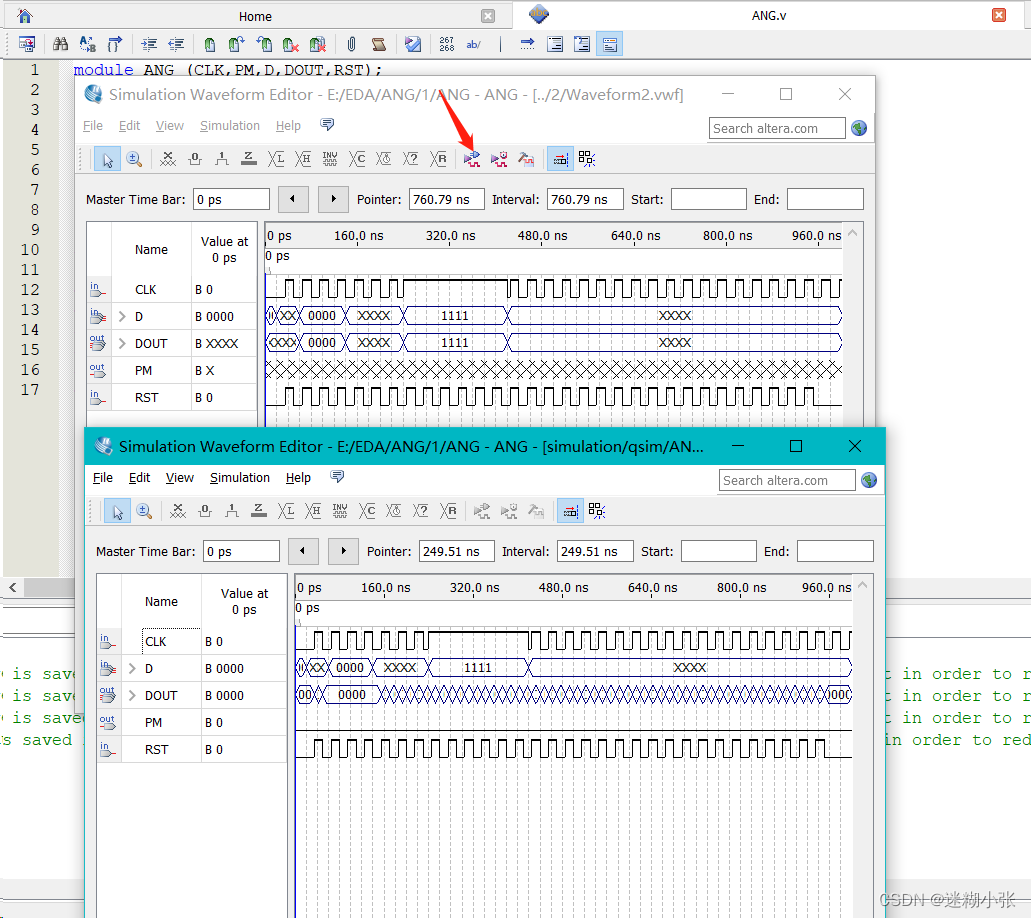

然后会出现一个小窗口那是在检测你给的信号符不符合代码要求,有没有错误,没有的话就会自动弹出一个新的波形窗口,仿真成功。否则检测截止小窗口里会出现错误,一般修改输入波形信号即可。

这样波形仿真就算完成啦!

错误窗口

三 硬件仿真

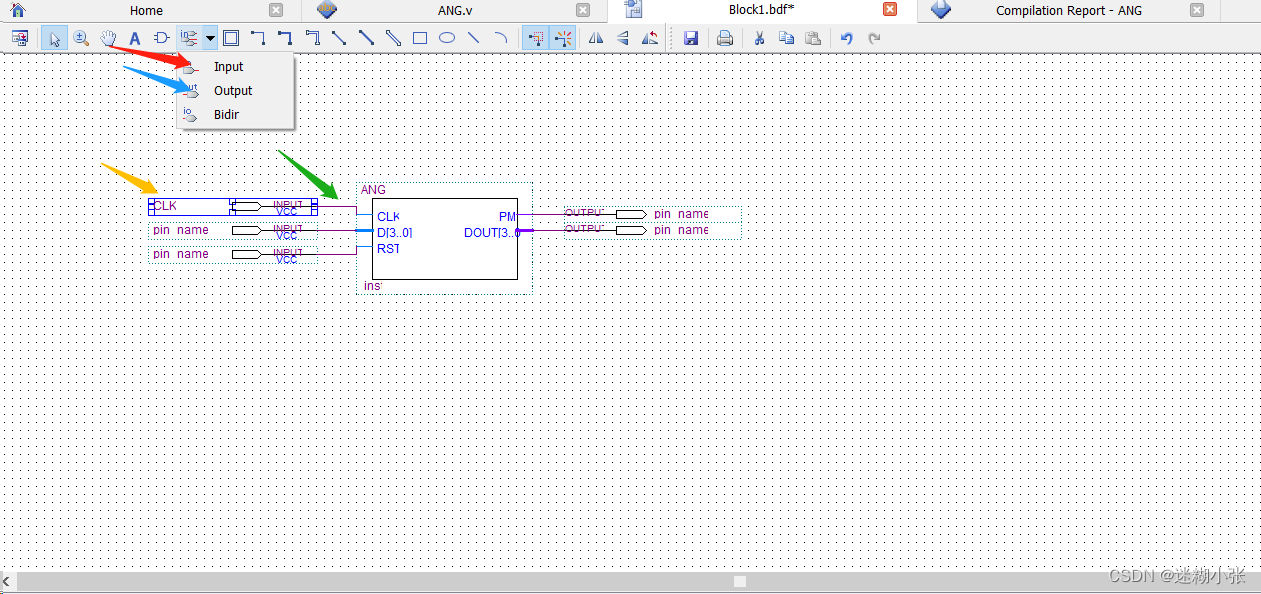

1.点击File-New(红色箭头),在弹出的窗口中选择Block Diagramy(蓝色箭头),点击OK。此时新建了一个硬件仿真文件。

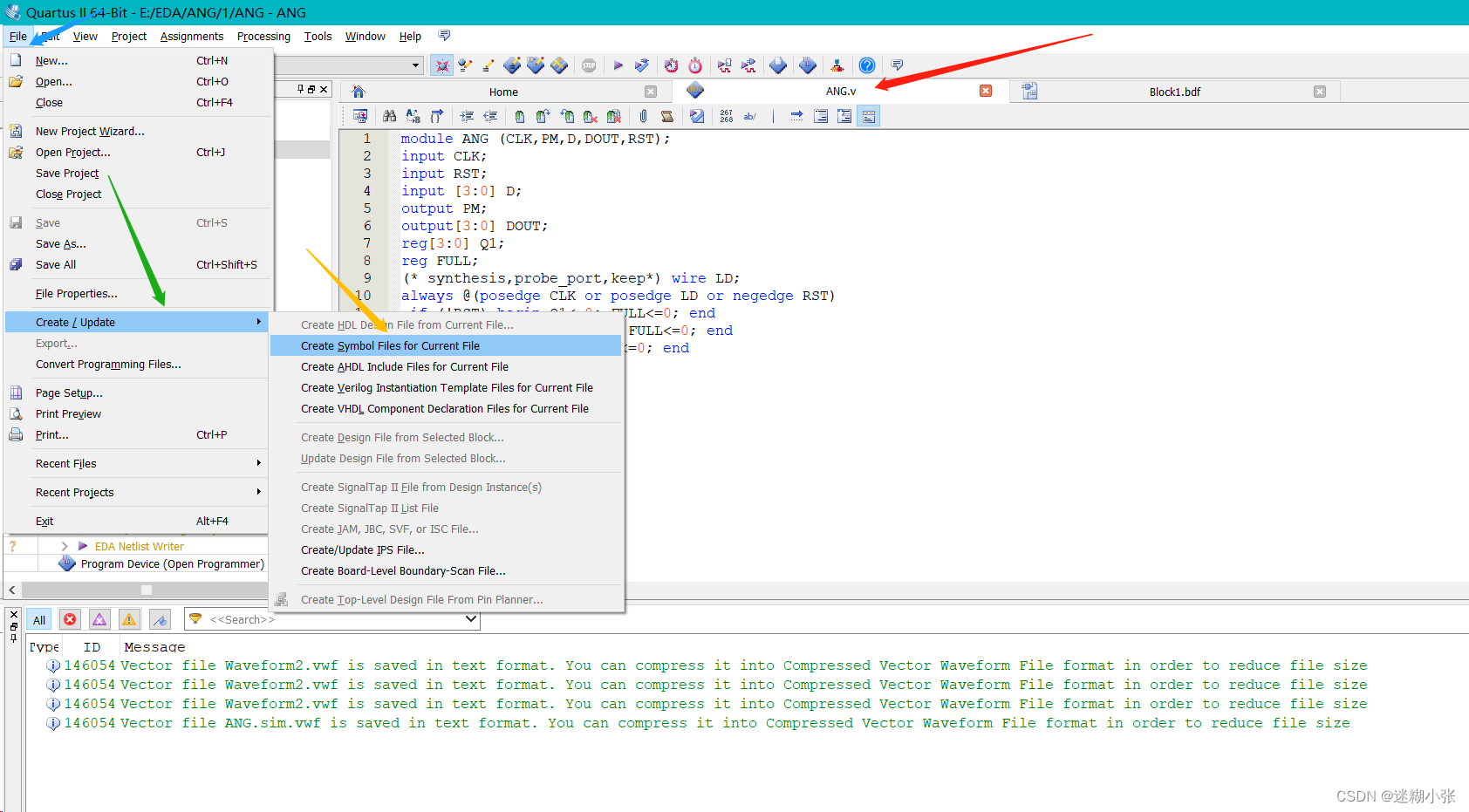

2. 在代码所在界面,File-Creat/Update-Creat Symble Files for Current File(红-蓝-绿-黄)

即把代码打包会生成一个器件(下面会说到)。

3.在硬件工程文件里面,点击与门那个图标,会弹出下面窗口,点击ANG即上一步我们打包后生成的硬件器件。(红-蓝-绿)点击OK.

4.放置输入输出引脚;

连线,鼠标放到一端点住出现“+”连向下一端出现小方框即可;

双击引脚可以修改名称,引脚名称与器件连接处名称一致即可;

(红/蓝-绿-黄)

!!!当鼠标上一直带着你之前用过的器件时,点击上层第二个图标即一个白色斜向上的小箭头,即可取消器件选择。

5.波形仿真

重复 二 波形仿真操作即可。