- 1Ubuntu的SSH安全配置,查看SSH登录日志文件,修改默认端口,UFW配置防火墙,禁止root用户登录,禁用密码登陆,使用RSA私钥登录,使用 Fail2ban 工具,使用两步验证(2FA)_ubuntu 显示登录成功记录

- 2仅用5000行代码,在V853上AI渲染出一亿幅山水画_ai做图代码量

- 3pandas03_dataframe统计某一列空值数量

- 4课程向:深度学习与人类语言处理 ——李宏毅,2020 (P11)_李宏毅 voice conversion

- 52021 RoboCom 世界机器人开发者大赛-本科组(初赛)7-2 芬兰木棋

- 6python 使用 pdf2image 库将PDF转换为图片

- 7(SQL)用bat启动sqlserver服务+创建数据库(学习笔记)(1)_开启sql server 几个服务的cmd命令 bat

- 8懒人神器:自动生成单元测试插件 Squaretest

- 9Spark - 配置参数详解_spark启动增加配置 javaagent --conf

- 10【干货】从0到1搭建公司虚拟专用网络实现异地内网访问(1)之基础简介_企业内网搭建

ARM TrustZone技术解析:构建嵌入式系统的安全扩展基石_arm trust zone_arm trustzone 架构

赞

踩

先自我介绍一下,小编浙江大学毕业,去过华为、字节跳动等大厂,目前阿里P7

深知大多数程序员,想要提升技能,往往是自己摸索成长,但自己不成体系的自学效果低效又漫长,而且极易碰到天花板技术停滞不前!

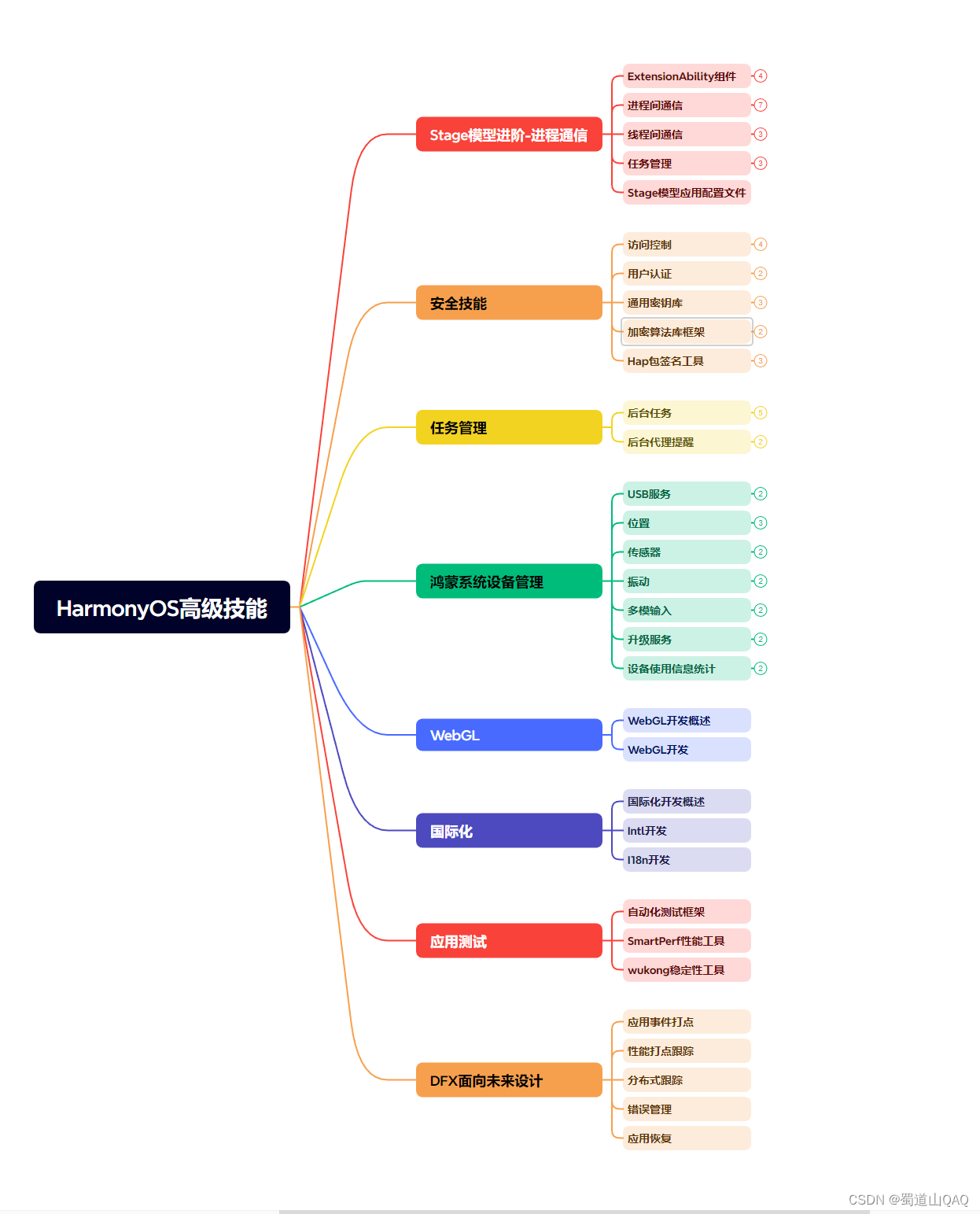

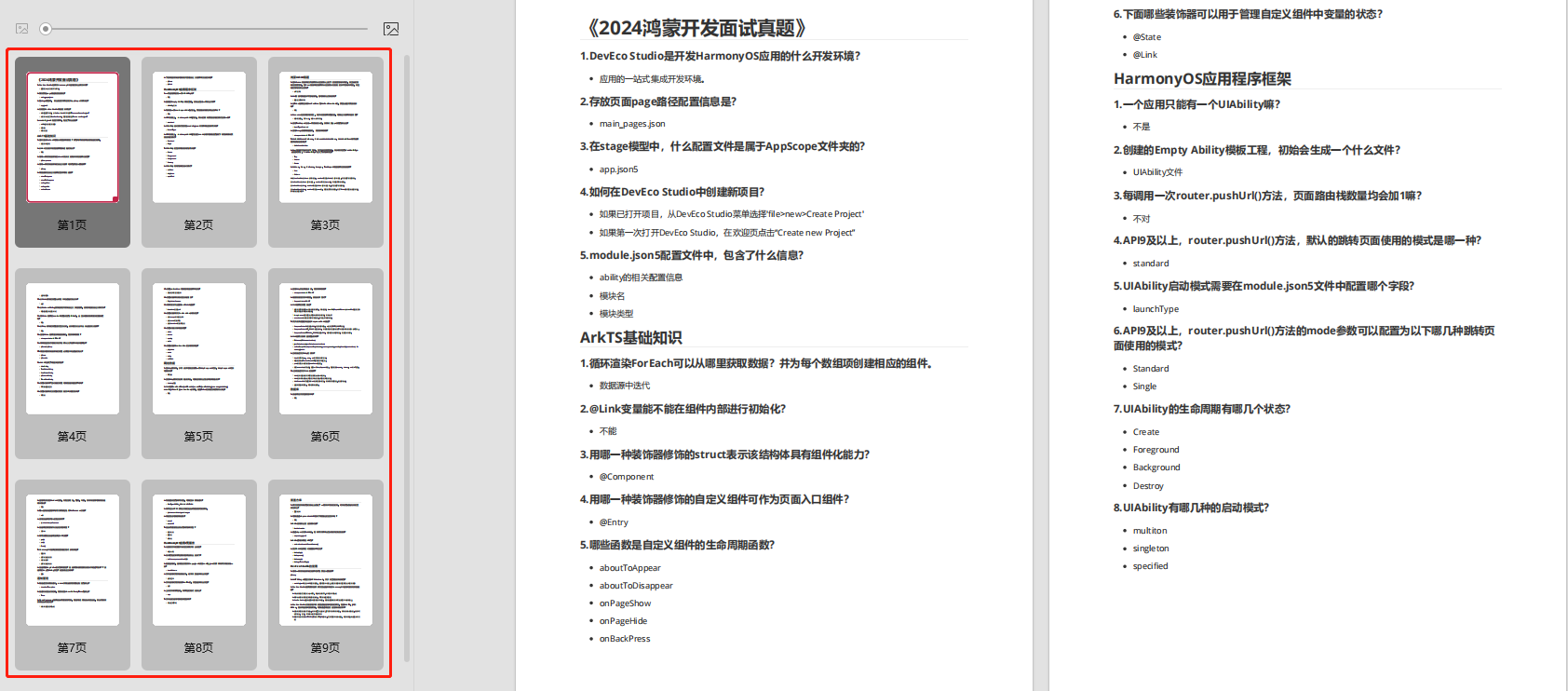

因此收集整理了一份《2024年最新HarmonyOS鸿蒙全套学习资料》,初衷也很简单,就是希望能够帮助到想自学提升又不知道该从何学起的朋友。

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上鸿蒙开发知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

如果你需要这些资料,可以添加V获取:vip204888 (备注鸿蒙)

正文

铁黄 iron oxide yellow

文章目录

说明: 在默认情况下,本文讲述的都是ARMV8-aarch64架构,linux kernel 64位

1、背景:

随着时代的发展、科技的进步,安全需求的趋势也越来越明显,ARM也一直在调整和更新其新架构,很多都是和安全相关的。 如下列出了一些和安全相关的架构

| Trustzone做为ARM安全架构的一部分,从 2008 年 12月 ARM 公司第一次 release Trustzone 技术白皮书。() 2013 年 Apple 推出了第一款搭载指纹解锁的 iPhone:iPhone 5s,用以保证指纹信息安全的 Secure Enclave 技术据分析深度定制了 ARM trustzone 架构,印象中这大概是 Trustzone 技术第一次走进大众视线。到如今 Trustzone 技术已经成为移动安全领域的重要基础技术,你也许不了解它的技术原理,但它一直默默为你守护你的指纹信息,账户密码等各种敏感数据。 如下也列出了一张在Trustzone架构下的一张指纹的框图,这也是这些年(2015-至今)比较流行的一张软件框图。 |

1.1、ARM Trustzone的安全扩展简介

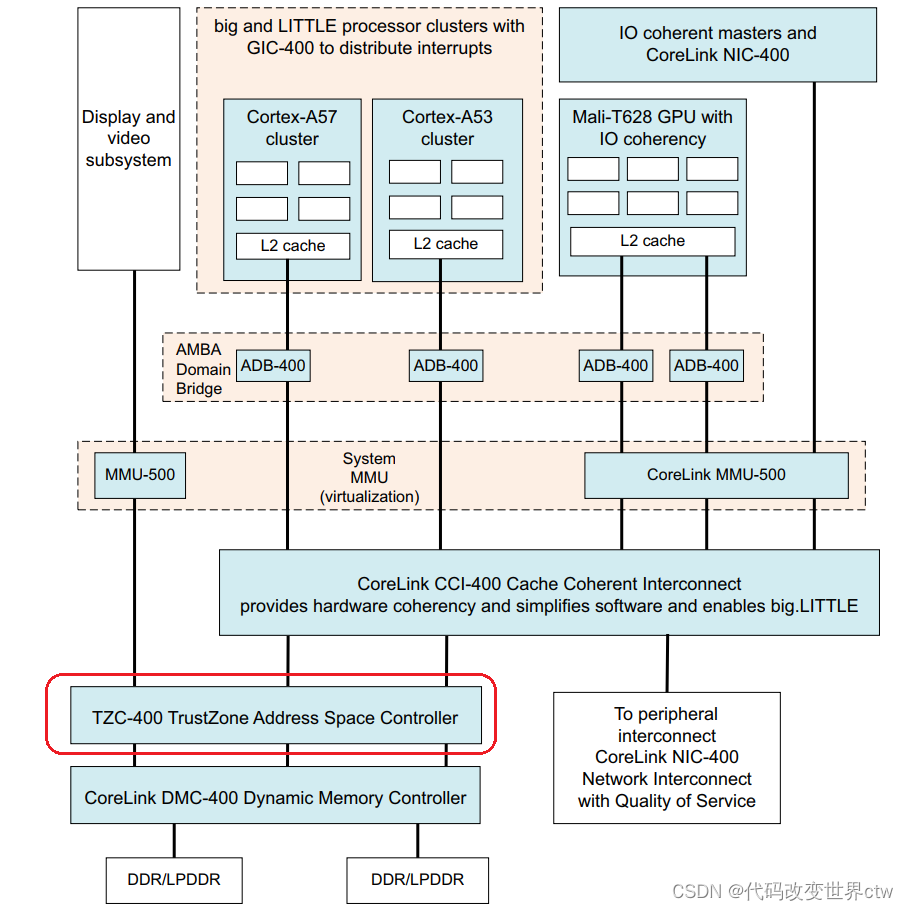

| 从上文我们已经知道, ARM Trustzone不具体指一个硬件,也不是一个软件,而是一个技术架构,在支持ARM Trustzone的SOC中,需按照ARM Trustzone技术对各个子模块进行设计。如下便展示了一个SOC的Trustzone架构下的设计框图 |

其中:

其中:

- (1)、AMBA-AXI总线的扩展, 增加了标志secure读和写地址线:AWPROT[1]和ARPROT[1]

- (2)、processor的扩展(或者说master的扩展),在ARM Core内部增加了SCR.NS比特位,这样ARM Core发起的操作就可以被标记“是以secure身份发起的访问,还是以non-secure身份发起的访问”

- (3)、TZPC扩展,在AXI-TO-APB端增加了TZPC,用于配置apb controller的权限(或者叫secure controller),例如将efuse(OTP Fuse)配置成安全属性后,那么processor以non-secure发起的访问将会被拒绝,非法的访问将会返回给AXI总线一个错误。

- (4)、TZASC扩展,在DDRC(DMC)之上增加一个memory filter,现在一般都是使用TZC400,或由SOC厂商自己设计一个这样的IP,或叫MPU,或集成在DMC内部,它的作用一般就是配置DDR的权限。 如果配置了DDR中某块region为安全属性,那么processor以non-secure发起的访问将会被拒绝。

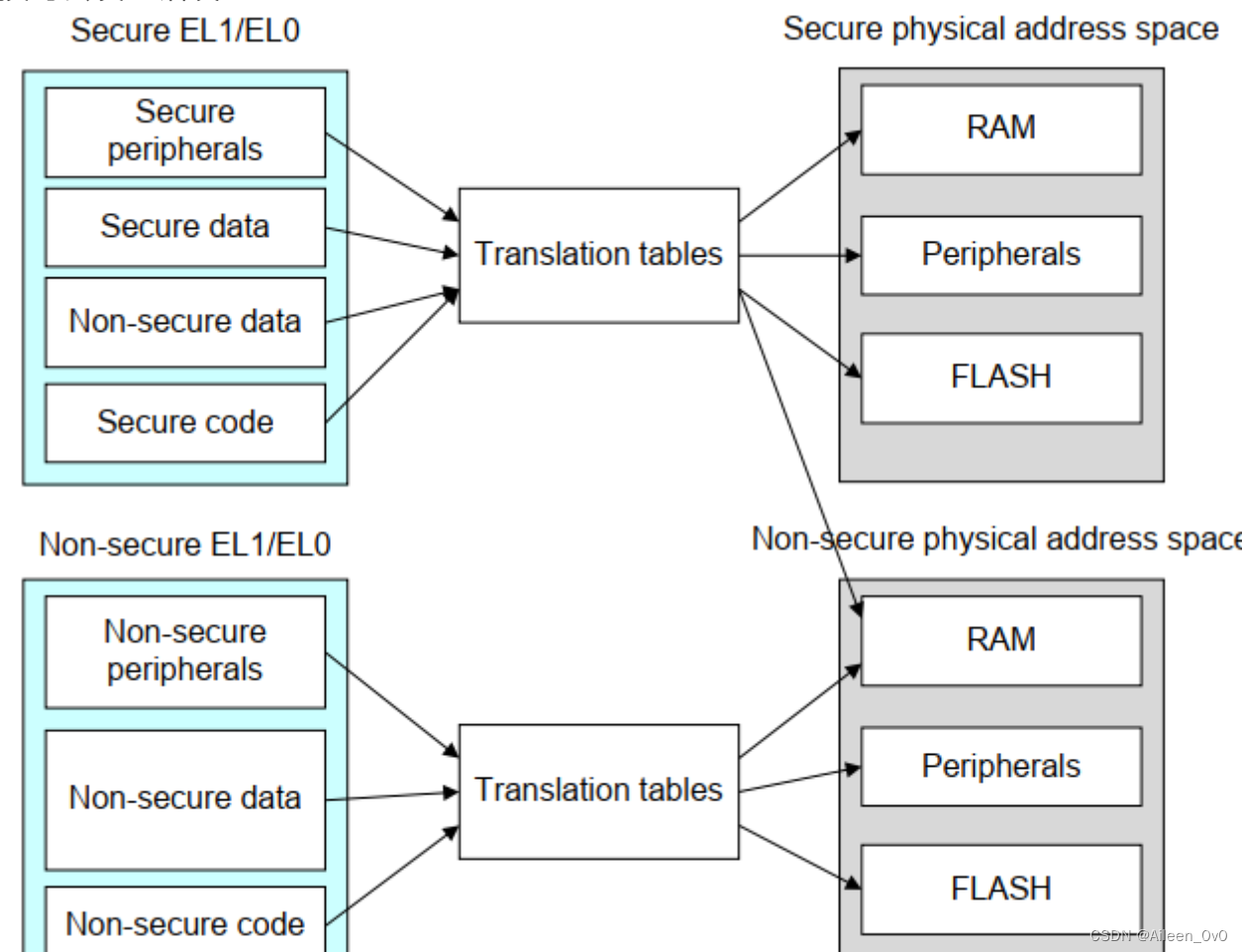

- (5)、MMU/Cache对安全扩展的支持 在软件架构的设计中,就分为: Non-secure EL0&1 Transslation Regime 和 Secure EL0&1 Transslation Regime,即normal world和secure world侧使用不同的Transslation Regime,其实就是使用不同的TTBRx_ELn寄存器,使用不同得页表。 注意:在armv7上,TTBRx_EL0、TTBRx_EL1是banked by Security State,也就是说在安全世界和非安全世界各有一组这样的寄存器,所以在linux和tee中可以各自维护一张自己的内存页表. 在armv8/armv9上,TTBRx_EL0、TTBRx_EL1不再是banked了,但是world switch时会在ATF中switch cpu context, 所以从hypervisror或os的视角来看,依然还是两套不同的TTBRx_ELn寄存器,linux和tee各有各的页表。 而在TLB中,又为每一个entry增加了Non-secure属性位,即标记当前翻译出的物理地址是secure还是non-secure; cache的扩展:在cache的entry中的TAG中,有一个NON-Secure Identifier标记为,表示当前缓存数据的物理地址是属于non-secure还是secure。

- (6)、gic对安全扩展的支持,在gicv2、gicv3的版本中,都增加了对安全扩展的支持. 以gicv3为例,将中断划分成了group0、secure group1和non-secure group1. 在软件的配置下,group0和secure group1的中断将不会target到REE(linux)中处理

1.2、ARM Trustzone的安全扩展详细解剖

1.3、 AMBA-AXI对Trustzone的支持

ARPROT[2:0]和AWPROT[2:0] 分别是读通道和写通道中的关于权限的信号,例如他们中的BIT[1]则分别表示正是进行secure身份的读或secure身份的写操作。

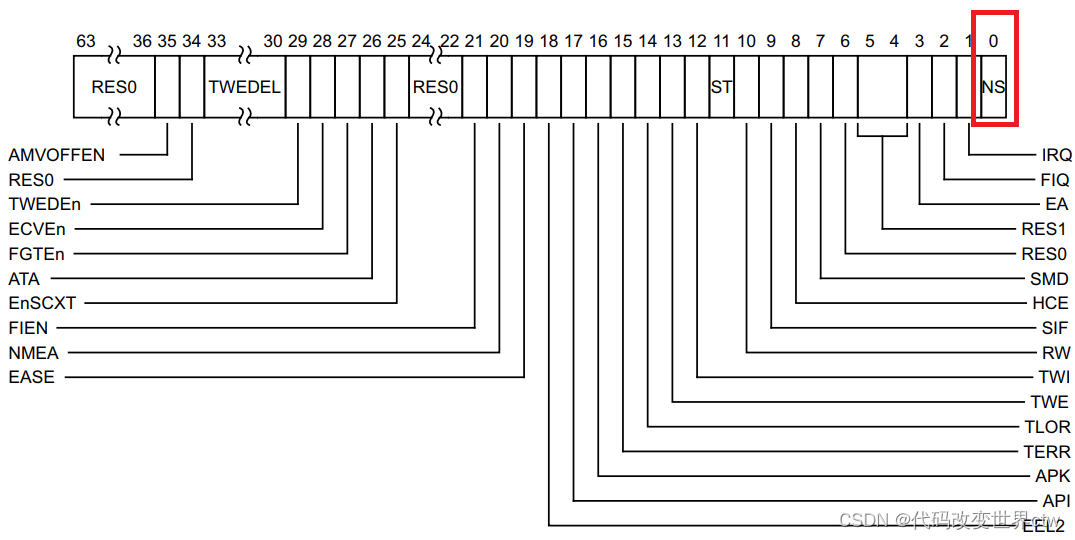

1.4Processor的SCR.NS比特位

SCR_EL3.NS 表示当前processor的安全状态,NS=1表示是non-secure的,NS=0表示是Secure的

2.TZC400和TZPC简介

TZC400接在core和(DMC)DDR之间,相当于一个memory filter。 TZC400一般可以配置8个region(算上特殊region0, 也可以说9个),然后可以对每一个region配置权限。例如讲一块region配置成secure RW的,那么当有non-secure的master来访问这块内存时,将会被TZC挡住。

2.1 MMU对Trustzone的支持

首页,在软件架构的设计中,就分为: Non-secure EL0&1 Transslation Regime 和 Secure EL0&1 Transslation Regime,即normal world和secure world侧使用不同的Transslation Regime;

其实就是使用不同的TTBRx_ELn寄存器,使用不同得页表 其次,在MMU使用的页表中,也有NS比特位。

Non-secure Transslation Regime 只能翻译NS=1的页表项,secure Transslation Regime 可以翻译NS=1和NS=0的页表项。

即secure的页表可以映射non-secure或secure的内存,而non-secure的页表只能去映射non-secure的内存,否则在转换时会发生错误  在Page Descriptor中(页表entry中),有NS比特位(BIT[5]),表示当前的映射的内存属于安全内存还是非安全内存:

在Page Descriptor中(页表entry中),有NS比特位(BIT[5]),表示当前的映射的内存属于安全内存还是非安全内存:

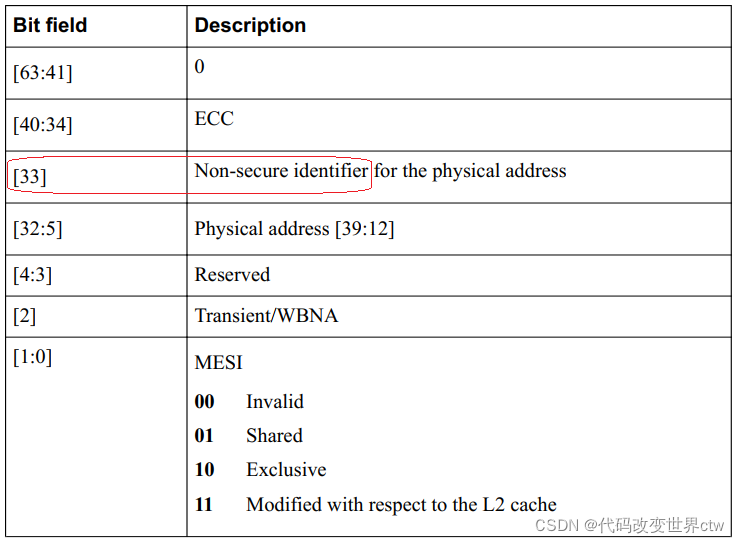

2.2 cache对Trustzone的支持

如下所示,以为cortex-A78为例,L1 Data Cache TAG中 ,有一个NS比特位(BIT[33]),表示当前缓存的cacheline是secure的还是non-secure的

2.3 TLB对Trustzone的支持

网上学习资料一大堆,但如果学到的知识不成体系,遇到问题时只是浅尝辄止,不再深入研究,那么很难做到真正的技术提升。

需要这份系统化的资料的朋友,可以添加V获取:vip204888 (备注鸿蒙)

一个人可以走的很快,但一群人才能走的更远!不论你是正从事IT行业的老鸟或是对IT行业感兴趣的新人,都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!

朋友,可以添加V获取:vip204888 (备注鸿蒙)**

[外链图片转存中…(img-gJNiDoPb-1713555080672)]

一个人可以走的很快,但一群人才能走的更远!不论你是正从事IT行业的老鸟或是对IT行业感兴趣的新人,都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!