- 1WPF 常用控件_wpf 控件

- 2一文带你搞懂AI前沿技术AIGC_aigc检测原理

- 3React Hooks小记(二)_useRef

- 4FPGA时序约束学习笔记(一)理论知识_小梅哥fpga时序约束从遥望到领悟

- 5探索国内大模型AIGC产品

- 6树1----7-3 列出叶结点

- 7[中国近代史] 第五章测验_19世纪末叶,维新派创办的宣传变法维新思想的报刊有:

- 8【Python高级编程】OpenCV库中的Canny边缘检测算法、原理、应用场景

- 9解决普中单核A2开发板更换STC89C52为STC89C52RC芯片,出现无法烧录的问题_stc89c52与stc89c52rc有哪些代码兼容性的问题

- 10Python速成

FPGA时序约束学习笔记(一)理论知识_小梅哥fpga时序约束从遥望到领悟

赞

踩

参考资料:《小梅哥FPGA时序约束从遥望到领悟》

一、时钟设计对FPGA设计的影响

1.外部输入时钟(如 PHY芯片输入时钟),通过普通IO口输入,为以太网通信的许多模块提供时钟源。但是由于输入的引脚为通用的IO引脚,在 FPGA 片上进行走线时,只能使用片上的长线和短线布线资源,有时候甚至要通过 LUT 连接,才能到达各个寄存器。无法通过专用时钟引脚输入,讲时钟信号通过全局时钟布线资源同步到全局时钟中。

不良后果有两点:(1)该时钟信号到达不同寄存器的时间由于经过不同的布线路径,会出现不同的时间延迟,影响建立时间和保持时间;(2)该时钟信号需要经过复杂的布线与经历高速翻转模块的噪声,会导致始终质量变差,例如边沿上升和下降更慢, 占空比发生变化,时钟抖动增大。

解决方法:将由通用IO输入的时钟信号同步到全局时钟资源中。

在 Cyclone IV E 器件中, 有这样的专用缓冲器,该缓冲器可以将普通 IO 或者寄存器产生的时钟信号分配到全局时钟资源上。 该缓冲器对用户以IP 的形式提供, 在 IP 列表的 IO 分组中, 名称叫做 ALTCLKCTRL。

我们这里只需将 mii_tx_clk 接入全局时钟资源,不需要做多时钟切换, 因此我们这里用途设置为“For global clock”, 数量选择 1,设置完成后点击 finish。通过例化便可条用ip核输出的时钟信号,此时已同步到全局时钟。

如此,大大减小了输入非全局时钟的影响。(例如COMS摄像头输入的像素时钟,当传输较高质量的图像时,也需要对像素时钟进行全局时钟化,虽然有些开发板上直接设置连接到专用的时钟引脚上,但还是需要注意保持时钟的质量)

2.在什么时候进行时序约束?

任何时候。

(1)创建时钟:timequset timing analysis,输入外部晶振时钟,

(2)PLL 的参考时钟,经过倍频得到 100MHz 的时钟信号,该 100MHz 的信号再作为整个设计的时钟信号使用。

(3)报告时钟约束。 通过报告时钟约束命令, 可以查看当前系统的所有时钟约束。

(4)查看运行最大频率。 通过报告最大频率命令, 可以查看当前经过布局布线的网表能够运行的最大时钟频率。

pll输出的最大时钟频率仅为68.79Hz,由于未加时钟约束,按照系统自动布局布线优化,导致远低于设置输出100MHz。

(5)解决方法:添加时序约束

使用约束文件指导 Quartus 工程进行编译。

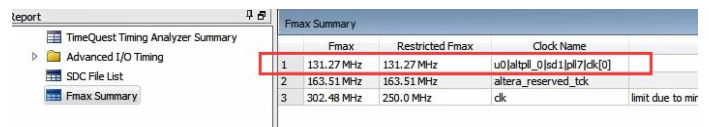

(6)编译添加约束文件后,再次查看最大运行频率(131.27MHz)。

事实证明,不添加时序约束时,按照quartus自动综合的最大运行频率无法到达最优,在所有设计中必须添加约束文件优化时序。

建议:在任何模块中都要添加时序约束文件,在vavido与quartus II中带有自动xdc文件编写,可以多加利用。

因为时钟约束只能约束 FPGA 芯片内的各个路径, 而对 FPGA 和其他芯片的连接,也就是 IO 口上的时序约束根本无能为力, 所以,要想解决这些问题,就涉及到另一个更加重要的约束了——IO 约束。

3.IO约束

在RGB888输出图像数据到ADV7123 芯片中。

直接将FPGA内部的时钟作为CLOCK提供给ADV7123 芯片作为数据同步时钟的具体现象。

不加任何 I/O 约束, 也不对 FPGA 输给 ADV7123 芯片的 CLOCK 时钟进行取反的情况下采集到的图像实拍。

出现严重的重影等现象,这其实是由于输出时钟没有良好的建立时间与保持时间的原因,当对输出时钟取反输出后,输出图像的质量大大提高。

![]()

不对输出时钟做取反处理,对输出信号时序约束,也可到达同样的效果,也可以说是验证了前面说的图像异常问题确实是由 IO 时序不满足导致的。

4FPGA 可编程原理

一个逻辑单元由一个查找表(LUT) 和 D 触发器(DFF) 组成

LUT 里面实际有 16 个1bit 的基于 SRAM 结构的存储器, 能够对应 a、 b、 c、 d 四个输入的逻辑组合的所有可能,Quartus 通过向这 16bit 的存储器里写入不同的初始值,就能使 a、 b、 c、 d 四个输入在不同的状态下输出不同的逻辑结果,从而实现使用一个 LUT 实现各种组合逻辑的功能。

既然 FPGA 已经能够实现各种的基本逻辑门功能了,而且还有 D 触发器能够实现时序逻辑功能,那么,要实现复杂逻辑功能, 无非就是把众多的基本逻辑功能联合起来,从而达到复杂逻辑功能的目的。

5.FPGA 内数据传输模型

(1)建立时间、保持时间及输出延迟

(2)时钟延迟

(3)数据到达时间

(4)数据需求时间

(5)建立时间余量

即为实际数据到达比需要数据(Tsu)到达的时间提前的时间。

(6)最高运行时钟频率

即通过建立保持余量,通过调控缩短reg_ck来提高最高运行频率。即减少最小建立时间余量。

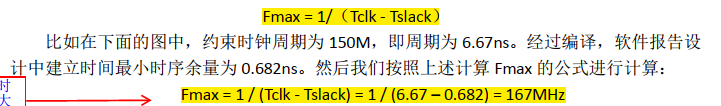

计算最高运行频率:

可以查看时序收敛下的建立保持余量,可以计算出最高运行频率。

(6)时序不收敛的设计 Fmax 计算

(7)保持时间余量

VGA输出噪点的问题,正是因为保持时间余量不够导致的。

这个数据需要保持稳定的时间长度,称为 D 触发器的保持时间(Th), 而保持时间余量,说的正是 D 端的数据在时钟上升沿

之后继续保持稳定的时间长度和 D 触发器的保持时间参数的差值。(即实际保持时间与需求保持时间的差值)

时序收敛与时序非收敛与建立时间想类似。

(7)时钟偏斜

时间偏斜即Tclk1与Tclk2的时间差。

Tskew = Tclk2 – Tclk1。