- 1Windows 键盘按键 测试_按键测试

- 2嵌入式开发之mipi干货_mipi 传输距离

- 3上门按摩APP小程序开发(源码开源,快速搭建)

- 4javaweb集成guacamole在html页面中展示_guacamole-common-js

- 5北京理工大学计算机考研调剂,2019年北京理工大学考研调剂相关规定

- 62024年 (第十届)全国大学生统计建模大赛优秀论文解析——中国经济发展与碳排放库兹涅茨曲线的验证研究_第十届全国大学生统计建模大赛成品论文

- 7【KG】TransE 及其实现_transe pytorch

- 8v11.03 鸿蒙内核源码分析(内存分配) | 内存有哪些分配方式 | 百篇博客分析HarmonyOS源码_鸿蒙系统代码长度

- 9SQLite3 使用基础_sqlite编译后如何作为服务启动

- 10[数据结构]二叉树的实现及应用

异或鉴相器 matlab 数字鉴相器,采用VHDL设计的全数字锁相环电路设计

赞

踩

摘要:叙述了全数字锁相环的工作原理,提出了应用VHDL 技术设计全数字锁相环的方法,并用复杂可编程逻辑器件CPLD 予以实现,给出了系统主要模块的设计过程和仿真结果。

0 引言

全数字锁相环(DPLL) 由于避免了模拟锁相环存在的温度漂移和易受电压变化影响等缺点。从而具备可靠性高、工作稳定、调节方便等优点。在调制解调、频率合成、FM立体声解码、图像处理等各个方面得到广泛的应用。随着电子设计自动化(EDA) 技术的发展,采用大规模可编程逻辑器件(如CPLD 或FPGA) 和VHDL 语言来设计专用芯片ASIC 和数字系统,而且可以把整个系统集成到一个芯片中,实现系统SOC ,构成片内锁相环。下面介绍采用VHDL技术设计DPLL 的一种方案。

1 DPLL 的基本结构

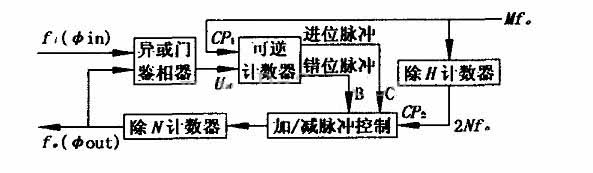

全数字锁相环结构框图如图1 所示, 由数字鉴相器、数字环路滤波器和数控振荡器3 部分组成。

设计中数字鉴相器采用了异或门鉴相器;数字环路滤波器由变模可逆计数器构成(模数K 可预置) ;数控振荡器由加/ 减脉冲控制器和除N 计数器构成。

可逆计数器和加/ 减脉冲控制器的时钟频率分别为Mf0和2Nf0 。这里f0 是环路的中心频率,一般情况下M 和N 为2 的整数幂。时钟2Nf0 经除H( = M/2N) 计数器得到。

2 数字锁相环的原理与实现

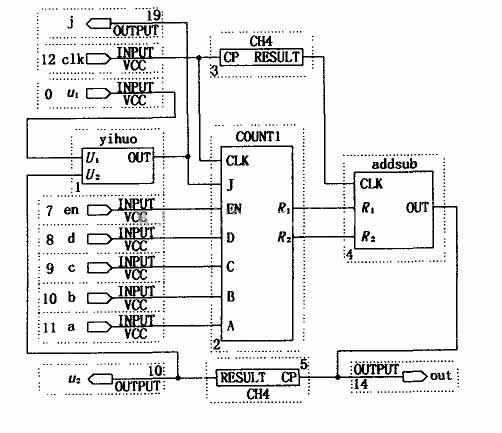

全数字锁相环原理如图2 所示, 其中: clk 为时钟频率,等于32f 0 ; U1 为输入,频率为f0 ; j 为异或门鉴相器的输出,它作为变模可逆计数器的方向控制信号;out 为加/ 减脉冲控制器的输出; U2 为DPLL 的输出,在相位锁定的频率为f0 , 相位与输入U1 相差Π/ 2 ; D、C、B 、A 可预置变模可逆计数器的模数,它在0001 —1111 范围内变化, 相应的模数在2.3 —2. 17 范围内变化; En 为可逆计数器使能端。

图2 数字锁相环原理图

2. 1 鉴相器的设计

异或门鉴相器用于比较输入信号u1 与数控振荡器输出信号u2 的相位差, 其输出信号ud 作为可逆计数器的计数方向控制信号。当ud 为低电平时( u1 和u2 有同极性时) ,可逆计数器作"加"计数。反之,当ud 为高电