- 1用Logisim设计半加器、全加器和四位数二进制补码电路_在logisim下实现4位2进制全加器仿真电路

- 2艺术类大学生搜题软件?学生党都在用的三款搜题工具来了 #笔记#其他_辅导丫网站

- 3怎么获取OpenAI的api-key【人工智能】_openai_api_key

- 4【数据结构大全】你想要的都有,数组、链表、堆栈、二叉树、红黑树、B树、图......_数据结构 所有

- 5[推荐系统] - 多目标排序 MMoE、PLE_多目标排序模型的结构

- 6秋叶StableDiffusion-webUI安装roop插件排雷记_秋叶webui

- 7微信小程序 Springboot 健身房教练私教预约系统_教练预约系统

- 8802.11-2020协议学习__$12-Security__$12.5.2-TKIP__2_802.11 2020

- 9每天一种算法分析-动态规划_算法分析与设计动态规划

- 10解读 GPT 官方最佳实践:6 大策略 17 个技巧_gpt使用技巧

FPGA实现 TCP/IP 协议栈,千兆网服务器版本,纯VHDL代码编写,提供16套vivado工程源码和技术支持_9527华安 csdn

赞

踩

目录

- 1、前言

- 2、相关方案推荐

- 3、详细设计方案

- 4、工程源码1详解:Artix7-35T--RTL8211F--TCP协议栈源码版本

- 5、工程源码2详解:Artix7-35T--RTL8211E--TCP协议栈源码版本

- 6、工程源码3详解:Artix7-35T--KSZ9031--TCP协议栈源码版本

- 7、工程源码4详解:Artix7-100T--B50610--TCP协议栈源码版本

- 8、工程源码5详解:Kintex7-35T--B50610--TCP协议栈源码版本

- 9、工程源码6详解:Kintex7-35T--88E1518--TCP协议栈源码版本

- 10、工程源码7详解:Zynq7020--B50610--TCP协议栈源码版本

- 11、工程源码8详解:Zynq XCZU4EV--RTL8211E--TCP协议栈源码版本

- 12、工程源码9详解:Artix7-35T--RTL8211F--TCP协议栈网表版本

- 13、工程源码10详解:Artix7-35T--RTL8211E--TCP协议栈网表版本

- 14、工程源码11详解:Artix7-35T--KSZ9031--TCP协议栈网表版本

- 15、工程源码12详解:Artix7-100T--B50610--TCP协议栈网表版本

- 16、工程源码13详解:Kintex7-35T--B50610--TCP协议栈网表版本

- 17、工程源码14详解:Kintex7-35T--88E1518--TCP协议栈网表版本

- 18、工程源码15详解:Zynq7020--B50610--TCP协议栈网表版本

- 19、工程源码16详解:Zynq XCZU4EV--RTL8211E--TCP协议栈网表版本

- 20、工程移植说明

- 21、上板调试验证并演示

- 22、福利:工程代码的获取

FPGA实现 TCP/IP 协议栈,千兆网服务器版本,纯VHDL代码编写,提供16套vivado工程源码和技术支持

1、前言

没玩过TCP网络通信都不好意思说自己玩儿过FPGA,这是CSDN某大佬说过的一句话,鄙人深信不疑。。。目前网上fpga实现udp协议的源码满天飞,我这里也有不少,但用FPGA纯源码实现TCP的项目却很少,能上板调试跑通的项目更是少之又少,甚至可以说是凤毛菱角,但很不巧,本人这儿就有一个;一般而言,用FPGA实现TCP并不是一个经济的方案,但对于芯片原型验证、航天可靠通信、水下通信等一些数据传输可靠性极高的领域而言,FPGA实现TCP方案依然占有一席之地;

工程概述

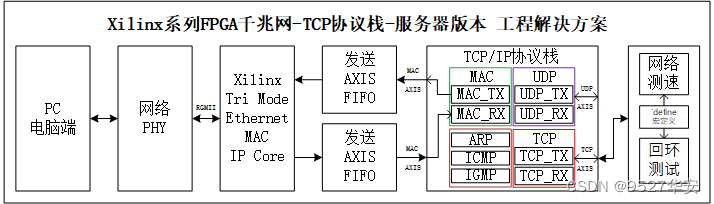

本设采用纯VHDL实现了千兆网TCP/IP协议栈,该协议栈为TCP服务器版本,没有用到任何一个IP核;并在Xilinx系列FPGA上做了部署并验证,由于使用千兆网,所以需要与FPGA开发板上的网络PHY交互,对硬件有一定要求;整个工程处理流程如下:

TCP/IP协议栈接收流程

PC端网络调试助手发送以太网数据包,或者发起ping操作,数据通过网线发送到FPGA开发板;FPGA开发板板载的网络PHY将PC发来的数据进行物理层解析,并以RGMII时序将网络数据发送给FPGA;FPGA调用Xilinx官方的Tri Mode Ethernet MAC IP核实现MAC数据解析,将RGMII时序转换为AXI4-Stream的MAC数据流输出;再调用2个AXI4-Stream Data FIFO做MAC数据跨时钟域处理和数据缓冲处理后依然以AXI4-Stream数据流输出给TCP/IP 协议栈;TCP/IP 协议栈对数据的MAC数据做以太网数据帧解析、IP报文解析等操作,去掉以太网帧头、协议层报文帧头等信息,提取出有效数据段信息和IP、MAC等地址信息,并以AXI4-Stream数据流形式输出有效数据,至此,TCP/IP协议栈接收流程完毕;

TCP/IP协议栈发送流程

用户数据测试模块为数据发起者,可以是测速模式下的单向的给PC端发送数据,也可以是数据回环模式下的将接收数据回环发送出去,两种模式通过define宏定义选择;用户输出发送时序为AXI4-Stream数据流;用户发送数据首先进入TCP/IP协议栈,并做协议层报文封装、以太网帧格式封装等操作,然后以AXI4-Stream数据流输出;再调用2个AXI4-Stream Data FIFO做TCP数据跨时钟域处理和数据缓冲处理后依然以AXI4-Stream数据流输出给MAC层;然后调用Xilinx官方的Tri Mode Ethernet MAC IP核实现MAC数据转换,将AXI4-Stream的MAC数据转换为RGMII时序输出;MAC数据再进入开发板板载的网络PHY进行物理层转换,将RGMII数据转换为差分信号通过网线输出给PC端,至此,TCP/IP协议栈发送流程完毕;

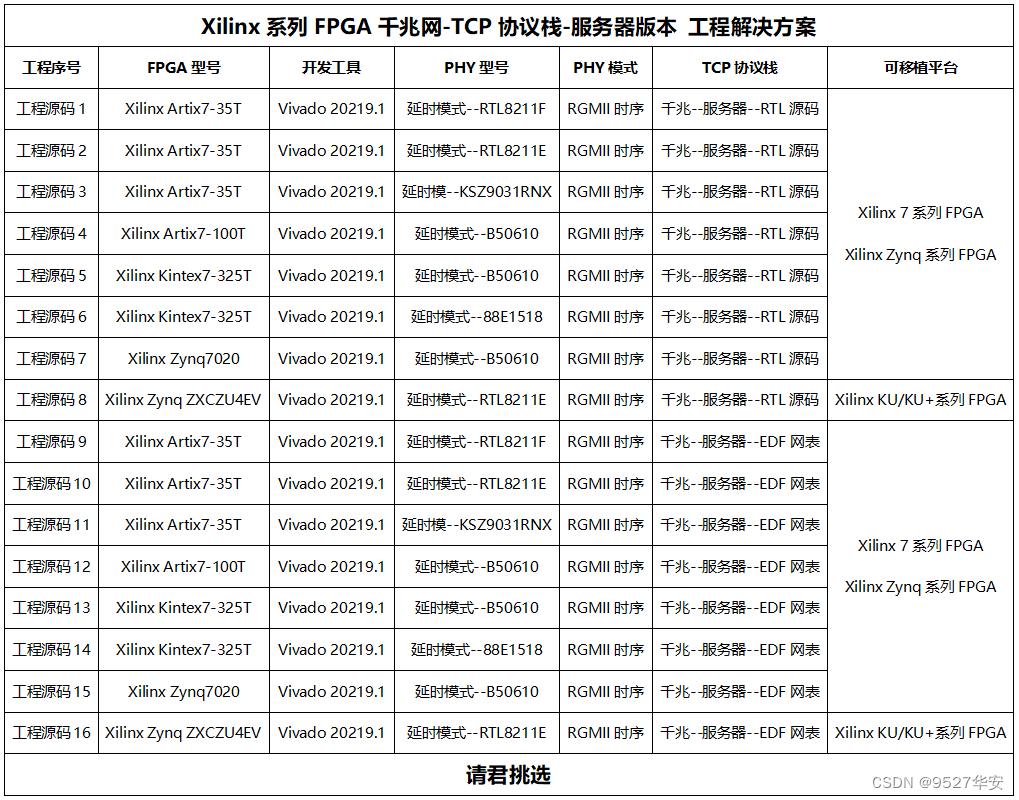

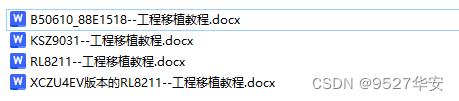

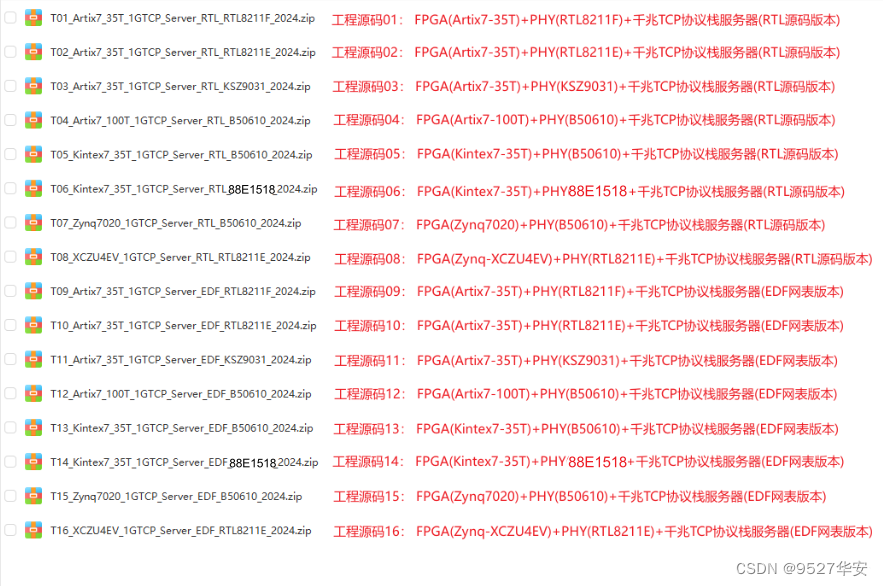

为了通用性和适应性,针对不同FPGA型号与不同网络PHY的差异,一共移植了16套工程源码,详情如下:

16套工程源码的TCP/IP 协议栈分为两种提供方式:

工程1~8提供的是TCP/IP 协议栈源码,即完全看得到并可修改的纯源码;

工程9~16提供的是TCP/IP 协议栈网表,可以正常调用、例化并使用,但看不到TCP/IP 协议栈源码也不能修改;

这里说明一下提供的16套工程源码的作用和价值,如下:

工程源码1

开发板FPGA型号为Xilinx Artix7-35T,板载的网络PHY型号为RTL8211F,工作于RGMII的延时模式下,进行TCP/IP 协议栈千兆网服务器版本的应用部署,其中TCP/IP 协议栈提供的是纯VHDL代码实现的源码,并对源码进行了verilog的顶层例化,对不熟悉VHDL语法的朋友来说是巨大福音,因为在工程中可以直接用verilog当时例化TCP/IP 协议栈,该工程适用于Xilinx 7系列FPGA移植,PHY适用于RTL8211F;

工程源码2

开发板FPGA型号为Xilinx Artix7-35T,板载的网络PHY型号为RTL8211E,工作于RGMII的延时模式下,进行TCP/IP 协议栈千兆网服务器版本的应用部署,其中TCP/IP 协议栈提供的是纯VHDL代码实现的源码,并对源码进行了verilog的顶层例化,对不熟悉VHDL语法的朋友来说是巨大福音,因为在工程中可以直接用verilog当时例化TCP/IP 协议栈,该工程适用于Xilinx 7系列FPGA移植,PHY适用于RTL8211E;

工程源码3

开发板FPGA型号为Xilinx Artix7-35T,板载的网络PHY型号为KSZ9031RNX,工作于RGMII的延时模式下,进行TCP/IP 协议栈千兆网服务器版本的应用部署,其中TCP/IP 协议栈提供的是纯VHDL代码实现的源码,并对源码进行了verilog的顶层例化,对不熟悉VHDL语法的朋友来说是巨大福音,因为在工程中可以直接用verilog当时例化TCP/IP 协议栈,该工程适用于Xilinx 7系列FPGA移植,PHY适用于KSZ9031RNX;

工程源码4

开发板FPGA型号为Xilinx Artix7-100T,板载的网络PHY型号为B50610,工作于RGMII的延时模式下,进行TCP/IP 协议栈千兆网服务器版本的应用部署,其中TCP/IP 协议栈提供的是纯VHDL代码实现的源码,并对源码进行了verilog的顶层例化,对不熟悉VHDL语法的朋友来说是巨大福音,因为在工程中可以直接用verilog当时例化TCP/IP 协议栈,该工程适用于Xilinx 7系列FPGA移植,PHY适用于B50610;

工程源码5

开发板FPGA型号为Xilinx Kintex7-35T,板载的网络PHY型号为B50610,工作于RGMII的延时模式下,进行TCP/IP 协议栈千兆网服务器版本的应用部署,其中TCP/IP 协议栈提供的是纯VHDL代码实现的源码,并对源码进行了verilog的顶层例化,对不熟悉VHDL语法的朋友来说是巨大福音,因为在工程中可以直接用verilog当时例化TCP/IP 协议栈,该工程适用于Xilinx 7系列FPGA移植,PHY适用于B50610;

工程源码6

开发板FPGA型号为Xilinx Kintex7-35T,板载的网络PHY型号为88E1518,工作于RGMII的延时模式下,进行TCP/IP 协议栈千兆网服务器版本的应用部署,其中TCP/IP 协议栈提供的是纯VHDL代码实现的源码,并对源码进行了verilog的顶层例化,对不熟悉VHDL语法的朋友来说是巨大福音,因为在工程中可以直接用verilog当时例化TCP/IP 协议栈,该工程适用于Xilinx 7系列FPGA移植,PHY适用于88E1518;

工程源码7

开发板FPGA型号为Xilinx Zynq7020,板载的网络PHY型号为B50610,工作于RGMII的延时模式下,进行TCP/IP 协议栈千兆网服务器版本的应用部署,其中TCP/IP 协议栈提供的是纯VHDL代码实现的源码,并对源码进行了verilog的顶层例化,对不熟悉VHDL语法的朋友来说是巨大福音,因为在工程中可以直接用verilog当时例化TCP/IP 协议栈,该工程适用于Xilinx Zynq7000系列FPGA移植,PHY适用于B50610;

工程源码8

开发板FPGA型号为Xilinx Zynq UltraScale+MPSoCs XCZU4EV,板载的网络PHY型号为RTL8211E,工作于RGMII的延时模式下,进行TCP/IP 协议栈千兆网服务器版本的应用部署,其中TCP/IP 协议栈提供的是纯VHDL代码实现的源码,并对源码进行了verilog的顶层例化,对不熟悉VHDL语法的朋友来说是巨大福音,因为在工程中可以直接用verilog当时例化TCP/IP 协议栈,该工程适用于Xilinx KU/KU+系列FPGA移植,PHY适用于RTL8211E;

工程源码9

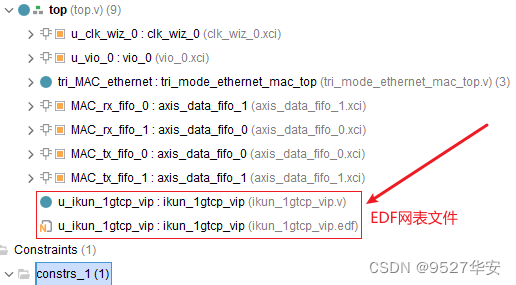

开发板FPGA型号为Xilinx Artix7-35T,板载的网络PHY型号为RTL8211F,工作于RGMII的延时模式下,进行TCP/IP 协议栈千兆网服务器版本的应用部署,其中TCP/IP 协议栈提供的是EDF网表文件,可以正常调用、例化并使用,但看不到TCP/IP 协议栈源码也不能修改,网表文件例化方式依然是verilog方式;该工程适用于Xilinx 7系列FPGA移植,PHY适用于RTL8211F;

工程源码10

开发板FPGA型号为Xilinx Artix7-35T,板载的网络PHY型号为RTL8211E,工作于RGMII的延时模式下,进行TCP/IP 协议栈千兆网服务器版本的应用部署,其中TCP/IP 协议栈提供的是EDF网表文件,可以正常调用、例化并使用,但看不到TCP/IP 协议栈源码也不能修改,网表文件例化方式依然是verilog方式;该工程适用于Xilinx 7系列FPGA移植,PHY适用于RTL8211E;

工程源码11

开发板FPGA型号为Xilinx Artix7-35T,板载的网络PHY型号为KSZ9031RNX,工作于RGMII的延时模式下,进行TCP/IP 协议栈千兆网服务器版本的应用部署,其中TCP/IP 协议栈提供的是EDF网表文件,可以正常调用、例化并使用,但看不到TCP/IP 协议栈源码也不能修改,网表文件例化方式依然是verilog方式;该工程适用于Xilinx 7系列FPGA移植,PHY适用于KSZ9031RNX;

工程源码12

开发板FPGA型号为Xilinx Artix7-100T,板载的网络PHY型号为B50610,工作于RGMII的延时模式下,进行TCP/IP 协议栈千兆网服务器版本的应用部署,其中TCP/IP 协议栈提供的是EDF网表文件,可以正常调用、例化并使用,但看不到TCP/IP 协议栈源码也不能修改,网表文件例化方式依然是verilog方式;该工程适用于Xilinx 7系列FPGA移植,PHY适用于B50610;

工程源码13

开发板FPGA型号为Xilinx Kintex7-35T,板载的网络PHY型号为B50610,工作于RGMII的延时模式下,进行TCP/IP 协议栈千兆网服务器版本的应用部署,其中TCP/IP 协议栈提供的是EDF网表文件,可以正常调用、例化并使用,但看不到TCP/IP 协议栈源码也不能修改,网表文件例化方式依然是verilog方式;该工程适用于Xilinx 7系列FPGA移植,PHY适用于B50610;

工程源码14

开发板FPGA型号为Xilinx Kintex7-35T,板载的网络PHY型号为88E1518,工作于RGMII的延时模式下,进行TCP/IP 协议栈千兆网服务器版本的应用部署,其中TCP/IP 协议栈提供的是EDF网表文件,可以正常调用、例化并使用,但看不到TCP/IP 协议栈源码也不能修改,网表文件例化方式依然是verilog方式;该工程适用于Xilinx 7系列FPGA移植,PHY适用于88E1518;

工程源码15

开发板FPGA型号为Xilinx Zynq7020,板载的网络PHY型号为B50610,工作于RGMII的延时模式下,进行TCP/IP 协议栈千兆网服务器版本的应用部署其中TCP/IP 协议栈提供的是EDF网表文件,可以正常调用、例化并使用,但看不到TCP/IP 协议栈源码也不能修改,网表文件例化方式依然是verilog方式;该工程适用于Xilinx Zynq7000系列FPGA移植,PHY适用于B50610;

工程源码16

开发板FPGA型号为Xilinx Zynq UltraScale+MPSoCs XCZU4EV,板载的网络PHY型号为RTL8211E,工作于RGMII的延时模式下,进行TCP/IP 协议栈千兆网服务器版本的应用部署,其中TCP/IP 协议栈提供的是EDF网表文件,可以正常调用、例化并使用,但看不到TCP/IP 协议栈源码也不能修改,网表文件例化方式依然是verilog方式;该工程适用于Xilinx KU/KU+系列FPGA移植,PHY适用于RTL8211E;

本博客详细描述了Xilinx系列FPGA实现 TCP/IP 协议栈 服务器版本的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做学习提升,可应用于医疗、军工等行业的高速接口或图像处理领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网以及其他开源免费获取渠道等等),若大佬们觉得有所冒犯,请私信批评教育;部分模块源码转载自上述网络,版权归原作者所有,如有侵权请联系我们删除;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

我这里已有的以太网方案

目前我这里有大量UDP协议的工程源码,包括UDP数据回环,视频传输,AD采集传输等,也有TCP协议的工程,对网络通信有需求的兄弟可以去看看:

直接点击前往

1G 千兆网 TCP–>客户端 方案

TCP分为服务器和客户端,两者代码是不一样的,看具体需求,既然本博客介绍的是TCP服务器,那么肯定就有TCP客户端,本来TCP客户端之前一直都有,但一直没有调通,经过两年半的练习调试,总算是调通了;TCP客户端依然是16套工程源码,我另外写了一篇博客介绍TCP客户端,感兴趣的朋友可以去看看:

直接点击前往

10G 万兆网 TCP–>服务器+客户端 方案

我这里也有10G 万兆网 TCP 方案,该方案有服务器和客户端两套代码,在Xilinx KU和KUP等平台测试通过并很稳定,对10G 万兆网 TCP 方案感兴趣的朋友可以去看看:

直接点击前往

3、详细设计方案

设计框图

本设计使用的工程详细设计方案框图如下:

测试用PC端电脑

测试用PC端电脑要求如下:

主板有千兆网口,可以是台式电脑或者笔记本电脑;

网口有网卡驱动;

安装网络调试助手软件,软件已提供在资料包中;

网络PHY

网络PHY市面上一大堆,既有国外的也有国产的,本设计对网络PHY原则上没有要求,但必须是RGMII接口,且工作于延时模式,工程不需要MDIO配置,可在硬件设计中使用电阻上下拉配置为延时模式;

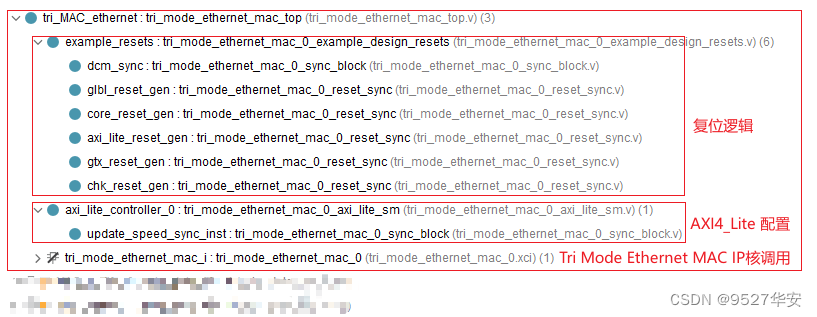

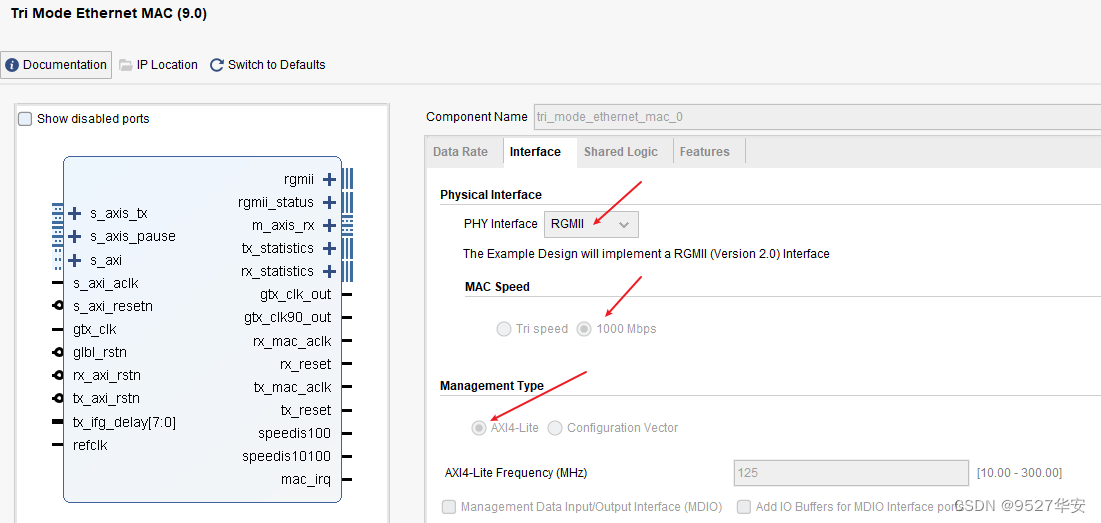

Tri Mode Ethernet MAC

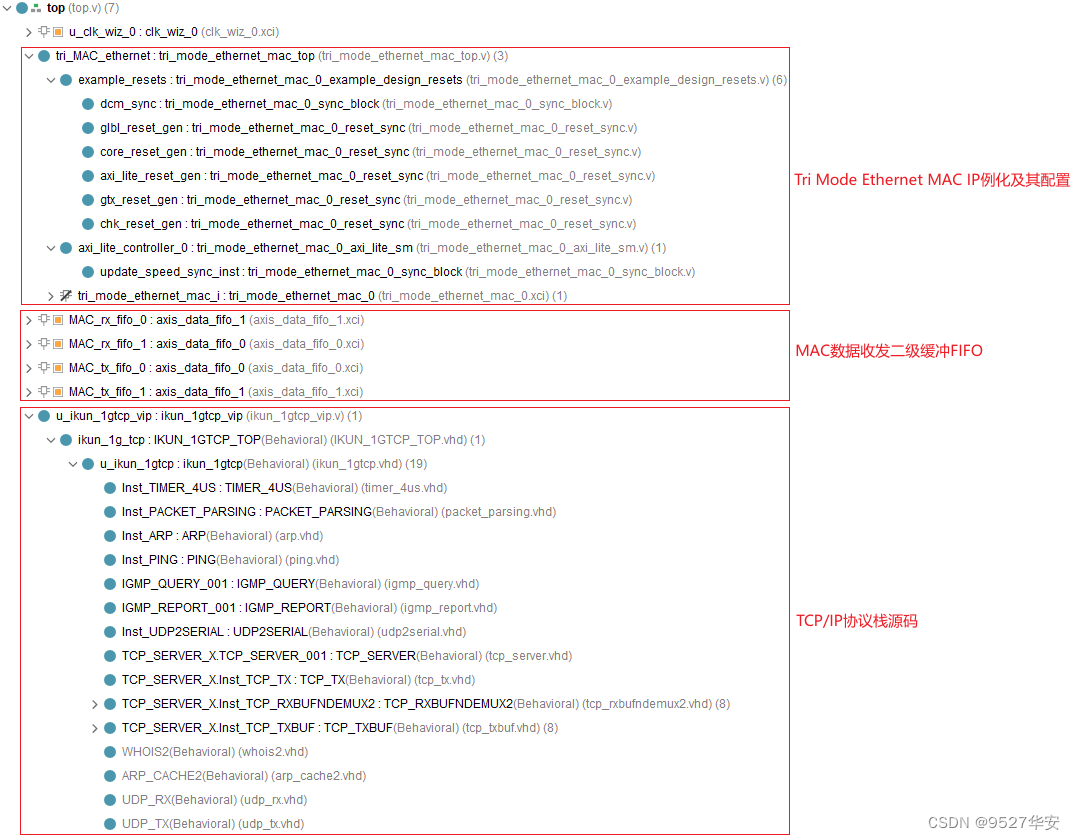

Tri Mode Ethernet MAC是Xilinx官方推出的以太网MAC IP核,可桥接PHY与FPGA用户逻辑,用户侧接口为AXI4-Stream;Tri Mode Ethernet MAC包括IP核调用、复位逻辑、AXI4_Lite配置等,其在工程中的代码架构如下:

Tri Mode Ethernet MAC配置为RGMII模式,固定速率为1000M,IP配置如下:

需要注意的是:

Xilinx 7系列FPGA与KU/KU+系列FPGA的Tri Mode Ethernet MAC在例化、端口、配置上均存在差异,7系列FPGA通过Tri Mode Ethernet MAC内部MMCM源语产生RGMII发送时钟和相位偏移90°时钟来实现RGMII延时模式控制,参考时钟为200M;而KU/KU+系列FPGA则没有这样的机制,而是通过延时源语实现RGMII延时模式的时序控制;此外,为了达到RGMII延时模式的时序控制,需要修改Tri Mode Ethernet MAC内部代码,所以需要对IP进行锁定操作,但在工程移植过程中,又需要对齐进行解锁并升级IP等操作,另外,还需要对IP内部的XDC文件做修改,以适应不同PHY的时序约束;

总之,对Tri Mode Ethernet MAC的操作需要高度的专业性,一般的FPGA开发者很难做到,所以我专门写了针对不同PHY型号和不同系列FPGA对应的Tri Mode Ethernet MAC的使用手册,手册放在了资料包中,全部手册如下:

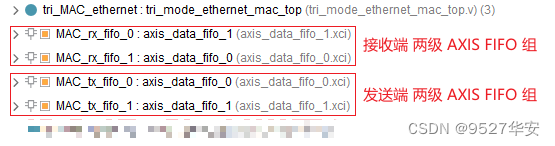

AXI4-Stream Data FIFO 组

调用AXI4-Stream Data FIFO 组实现MAC数据与TCP/IP协议栈之间的数据桥接,其在工程中的代码架构如下:

以接收端为例:

第一级FIFO为异步时钟FIFO,实现MAC数据从Tri Mode Ethernet MAC到TCP/IP协议栈的跨时钟域处理;

第一级FIFO为同步时钟FIFO,实现MAC数据到TCP/IP协议栈的数据缓冲处理;

以发送端为例:

第一级FIFO为异步时钟FIFO,实现MAC数据从TCP/IP协议栈到Tri Mode Ethernet MAC的跨时钟域处理;

第一级FIFO为同步时钟FIFO,实现MAC数据到Tri Mode Ethernet MAC的数据缓冲处理;

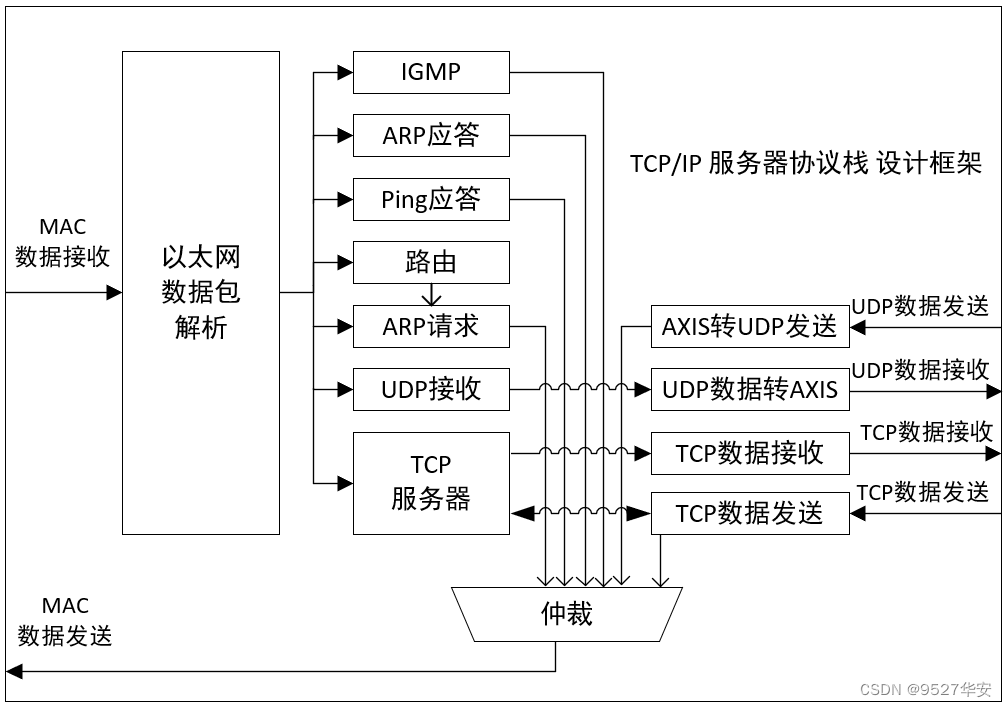

TCP/IP协议栈简介

本TCP/IP协议栈为纯VHDL实现的千兆网速率服务器版本,可实现TCP协议网络通信,针对不同需求,提供两个版本的模块,一种是TCP/IP 协议栈源码,即完全看得到并可修改的纯源码;另一种是TCP/IP 协议栈网表,可以正常调用、例化并使用,但看不到TCP/IP 协议栈源码也不能修改;TCP/IP协议栈基本设计框架如下:

其中的UDP我们没有用到,只用到了TCP;

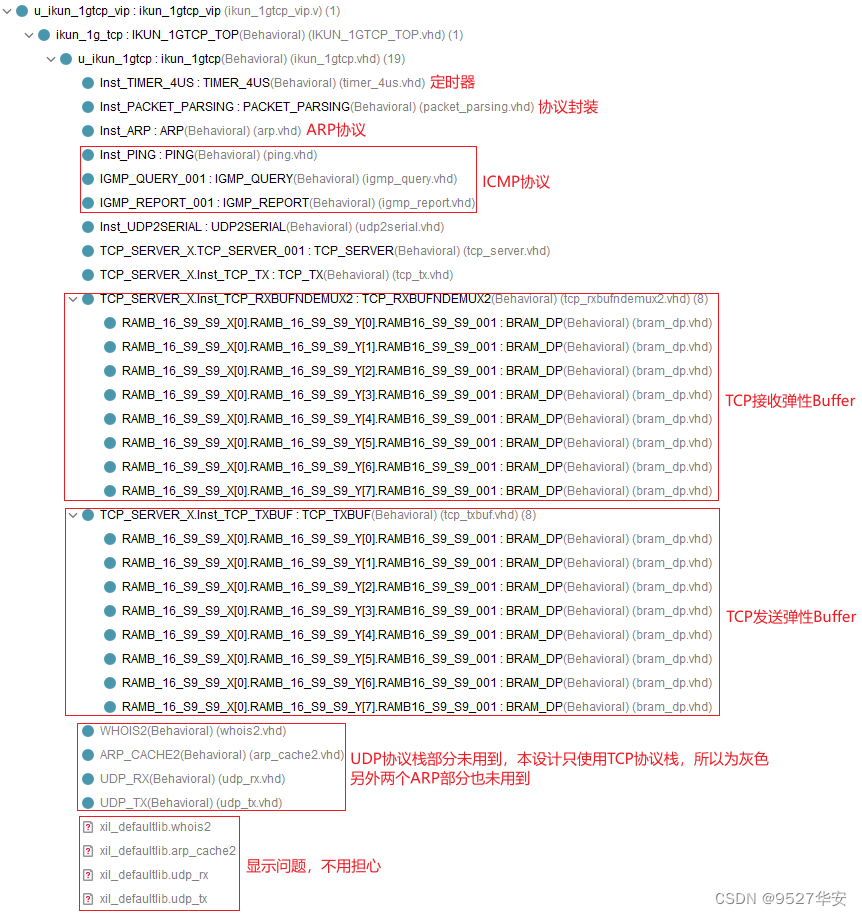

TCP/IP协议栈源码简介

TCP/IP 协议栈源码架构如下:

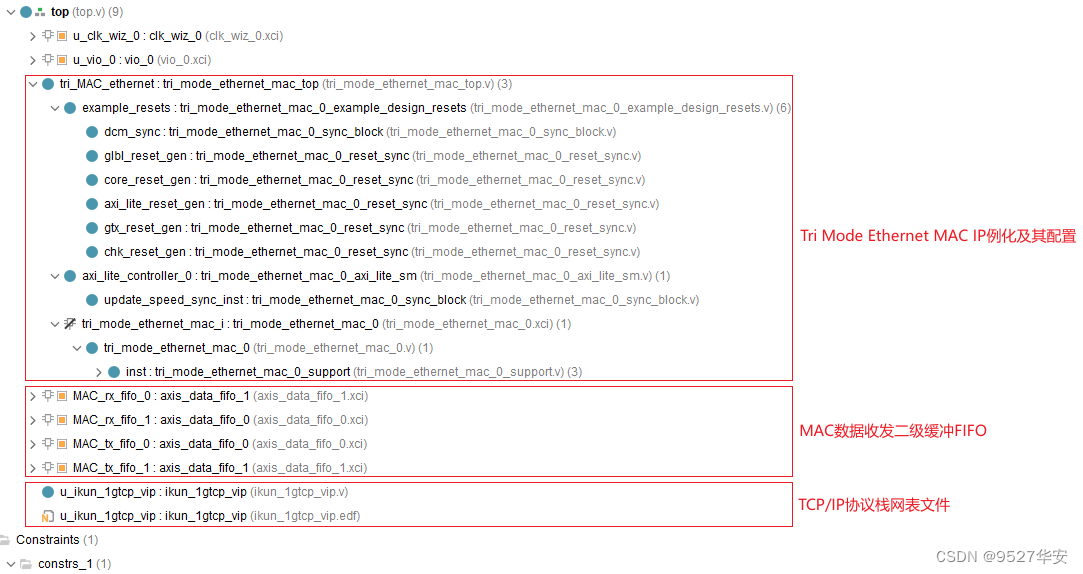

TCP/IP协议栈网表简介

TCP/IP 协议栈网表架是TCP/IP协议栈源码加密封装而来,用户可以正常调用、例化并使用,但看不到TCP/IP 协议栈源码也不能修改;架构如下:

TCP/IP协议栈性能简介

此TCP/IP协议栈是TCP服务器,不是客户端;即FPGA是TCP服务器,远程节点(比如 PC 电脑)是客户端;

常规性能

1:纯VHDL实现,没有用到任何一个IP核;

2:移植性天花板,该协议栈可在Xilinx、Altera、Lattice、国产FPGA等各大FPGA型号之间任意移植,因为是没有任何IP和源语的纯VHDL代码实现;但例如Tri Mode Ethernet MAC这样的PHY侧IP核目前用的Xilinx的;

3:功能齐全,包含了服务器和客户端,客户端目前还在开发中,暂不提供;TCP/IP协议栈本身包含了动态ARP、NDP、PING、IGMP (for multicast UDP)等功能模块;

4:代码符合标准的IEEE 802.3协议,支持IPv4和IPv6;

5:对外接PHY的数据格式要求:RGMII;

6:时序收敛很到位,考虑到TCP协议的复杂性和时序的高要求,所以没有采用时序收敛不强的verilog,而是VHDL,虽然阅读性可能会低一些,但用户只需要知道用户接口即可,并不需要去看内部的复杂代码;

7:动态ARP功能;

8:带ping功能;

9:支持多播;

支持多节点

支持节点数是TCP里面最重要的性能指标之一,这里需要重点讲述:

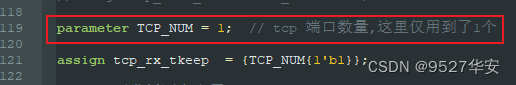

TCP节点数最大支持255个,通过parameter TCP_NUM参数设置,但前提是你的FPGA资源能满足;TCP_NUM参数可以在代码中自由修改,含义和用法,在代码里有详细的注释,为了防止不同编译器下中文注释出现乱码,注释均由英文书写,英语较差的兄弟可以直接某度翻译,位置如下:

本例程只用到了1个节点;

此外,使用TCP/IP 协议栈网表的工程不支持多节点,没有此参数配置;

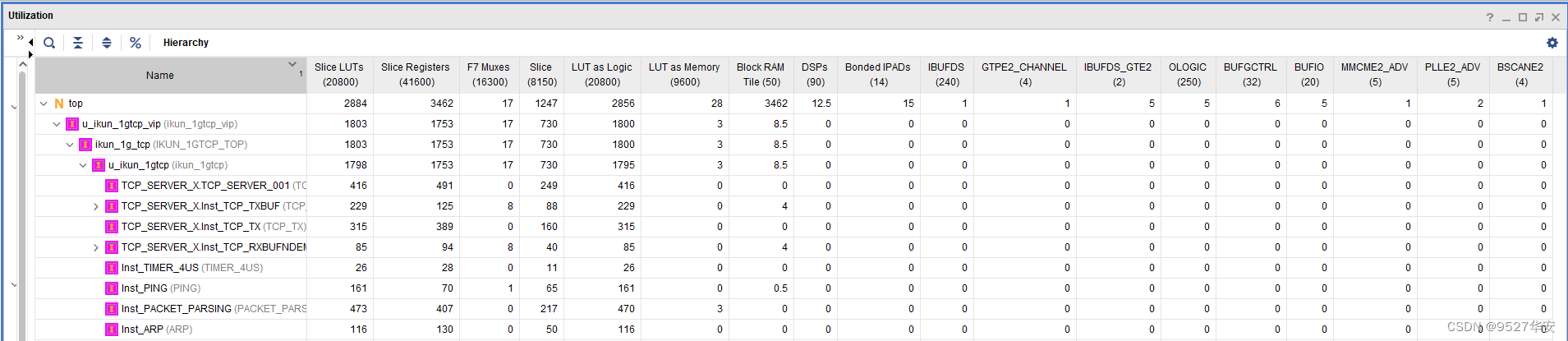

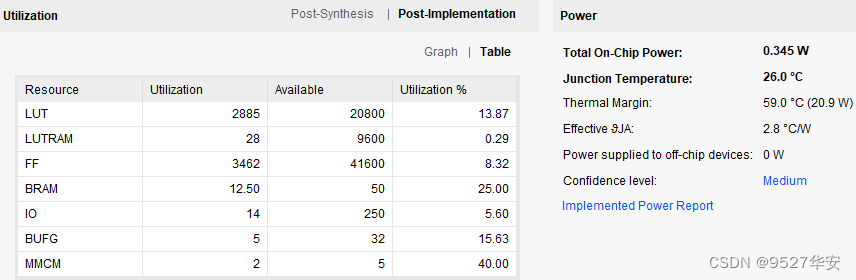

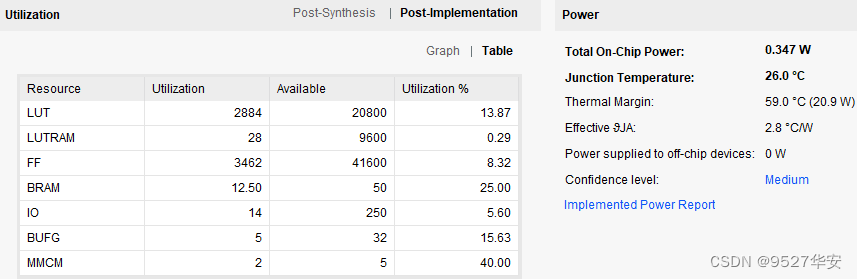

FPGA资源占用少

FPGA资源消耗是TCP里面最重要的性能指标之一,这里需要重点讲述:

FPGA资源消耗很低;以下举例:

以Xilinx系列Artix7-35T平台为例,TCP/IP协议栈的资源消耗如下:

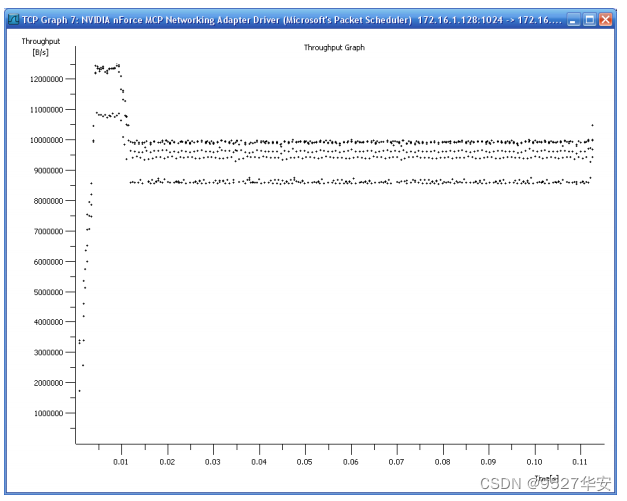

数据吞吐率高

数据吞吐率是TCP里面最重要的性能指标之一,这里需要重点讲述:

下面给出4项测试结果,你可以自己对比评估以下:

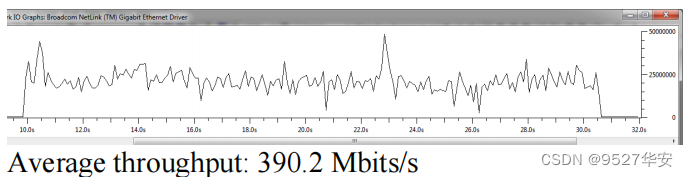

测试1:

通过千兆以太网在TCP服务器和TCP客户端之间双向连接,FPGA参考时钟120 MHz条件下,测量的持续吞吐率为双向并发452 Mbits/s;

测试2:

Xilinx Spartan-6 -2速度等级,FPGA参考时钟120 MHz,512字节的UDP数据包通过局域网点对点发送下测得:

0丢包,吞吐率为878.5 Mbits/s;当用户时钟为125 MHz或以上时,UDP最大帧吞吐率为915 Mbits/s;

测试3:

TCP服务器传输吞吐量在1百兆局域网下PC端测量平均吞吐量为93 Mbps,如下;

测试4:

TCP服务器将8Gbits发送到TCP Java客户端,同时Wireshark收集速度信息。从基于FPGA的TCP服务器到PC的点对点LAN连接平均吞吐率为390.2 Mbits/s;如下:

低延时性能

延时性能是TCP里面最重要的性能指标之一,这里需要重点讲述:

延时与TCP数据包长直接相关,如果你对延时性能性能要求很高,则可以减少包长来有效降低延时,假设你的载包为X bytes,那么你的收发延时关系如下:

发送延时=0.5 + 2X÷125 µs;

接收延时=0.5 + X÷125 µs;

最大帧长度为1460字节,FPGA 时钟125 MHz下的测试结果如下:

发送延时=23.9µs;

接收延时=12.2µs;

TCP/IP协议栈接口描述

由于TCP/IP协议栈主体部分由VHDL代码编写,导致可读性较差,毕竟很多朋友都是直接学的verilog语言,对VHDL并不熟悉,所以我们用verilog模块对VHDL模块做了例化形成verilog的顶层模块接口供用户例化,所以TCP/IP协议栈顶层接口如下:

module ikun_1gtcp_vip #(

parameter TCP_NUM = 1 , // tcp 端口数量,这里仅用到了1个

parameter CLK_FREQUENCY = 125 , // 参考时钟频率,比如输入时钟为125M,则CLK_FREQUENCY=125

parameter TX_IDLE_TIMEOUT = 50 , // 以太网帧发送间隔

parameter IPVX_ADDR_LOOP = 1 , // 目的IP地址回环使能; 1-->不需要指定目的IP地址; 0-->需要指定目的IP地址;

parameter SIMULATION = 1'b0 // 仿真模式; 1-->开启仿真模式; 0-->关闭仿真模式; 默认关闭

)(

// 时钟和复位

input clk , // 参考时钟

input sync_reset , // 同步复位

input async_reset , // 异步复位

// 配置端口

input [ 47:0] fpga_MAC_addr , // FPGA网卡MAC地址

input [ 31:0] fpga_IPV4_addr , // FPGA网卡IPV4地址

input [127:0] fpga_IPV6_addr , // FPGA网卡IPV6地址

input [ 31:0] fpga_multicast_addr, // FPGA网卡组播地址

input [ 31:0] fpga_subnet_addr , // FPGA网卡子网掩码

input [ 31:0] fpga_gaitway_addr , // FPGA网卡网关地址

input [16*TCP_NUM-1:0] fpga_tcp_port , // FPGA网卡端口号

input [ 31:0] PC_IPV4_addr , // 远端网卡IPV4地址

input [ 15:0] PC_tcp_port , // 远端网卡端口号

output [ 15:0] PC_tcp_port_out , // 远端网卡端口号

// MAC层接口信号

output [ 7:0] mac_tx_tdata , // 输出--MAC层发送数据

input mac_tx_tready , // 输入--MAC层发送数据准备好

output mac_tx_tvalid , // 输出--MAC层发送数据有效

output mac_tx_tuser , // 输出--MAC层发送数据开始

output mac_tx_tlast , // 输出--MAC层发送数据结尾

input [ 7:0] mac_rx_tdata , // 输入--MAC层接收数据

input mac_rx_tvalid , // 输入--MAC层接收数据有效

input mac_rx_tuser , // 输入--MAC层接收数据开始

input mac_rx_tlast , // 输入--MAC层接收数据结尾

// UDP协议栈用户接口信号

output [ 7:0] udp_rx_tdata , // 输出--UDP协议栈用户接收数据

output udp_rx_tvalid , // 输出--UDP协议栈用户接收数据有效

output udp_rx_tuser , // 输出--UDP协议栈用户接收数据开始

output udp_rx_tlast , // 输出--UDP协议栈用户接收数据结束

input [ 7:0] udp_tx_tdata , // 输入--UDP协议栈用户发送数据

input udp_tx_tvalid , // 输入--UDP协议栈用户发送数据有效

output udp_tx_tready , // 输入--UDP协议栈用户发送数据准备好

input udp_tx_tuser , // 输入--UDP协议栈用户发送数据开始

input udp_tx_tlast , // 输入--UDP协议栈用户发送数据结束

output udp_tx_ack , // 输入--UDP协议栈用户发送数据应答

output udp_tx_nak , // 输入--UDP协议栈用户发送数据无应答

// TCP协议栈用户接口信号

output [8*TCP_NUM-1:0] tcp_rx_tdata , // 输出--TCP协议栈用户接收数据

output [TCP_NUM-1:0] tcp_rx_tvalid , // 输出--TCP协议栈用户接收数据有效

output [TCP_NUM-1:0] tcp_rx_tready , // 输出--TCP协议栈用户接收数据准备好

input [TCP_NUM-1:0] tcp_rx_tkeep , // 输入--TCP协议栈用户接收数据选通

input [8*TCP_NUM-1:0] tcp_tx_tdata , // 输入--TCP协议栈用户发送数据

input [TCP_NUM-1:0] tcp_tx_tvalid , // 输入--TCP协议栈用户发送数据有效

output [TCP_NUM-1:0] tcp_tx_tkeep // 输出--TCP协议栈用户发送数据选通

);

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

TCP/IP协议栈接口是用户逻辑与TCP/IP协议栈对接的,所以这部分非常重要,用户想要把TCP/IP协议栈用起来,理论上只需要掌握其用户接口的使用即可;

其中的parameter参数有详细注释;

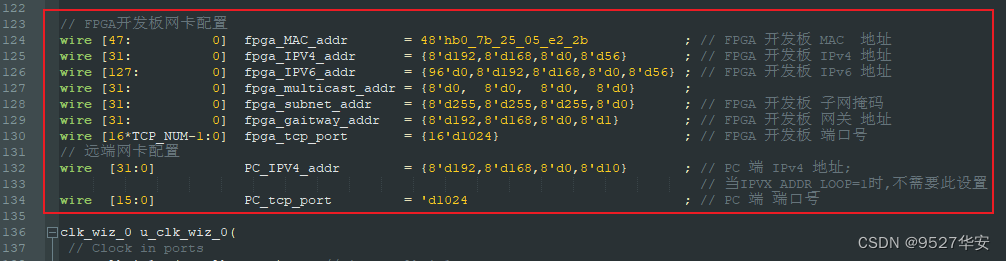

配置端口用户对FPGA开发板做网卡级别的配置,包括IP、MAC地址等;

MAC层接口与Tri Mode Ethernet MAC IP核对接;

UDP协议栈用户接口暂时用不到;

TCP协议栈用户接口是用户逻辑直接对接的接口;

具体可参考工程源码中对该模块的调用;

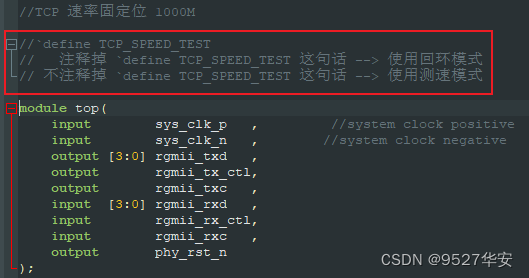

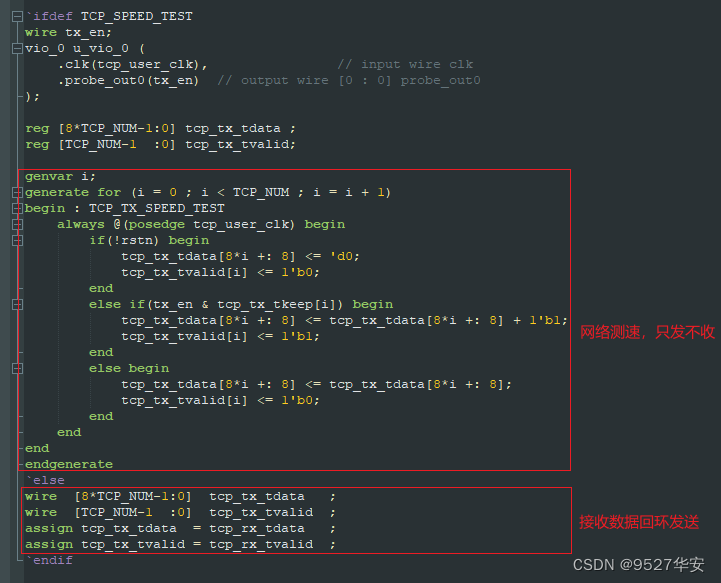

TCP用户数据测试模块

TCP用户数据测试模块集成了接收数据回环和数据测速功能,通过define宏定义选择,如下:

接收数据回环功能:

将接收数据回环发送出去,即形成发送=接收的自回环功能;该功能的作用是配合网络调试助手进行数据收发测试、数据丢包测试、数据正确性测试等;

数据数据测速:

FPGA自动循环向TCP/IP 协议栈发送累加的数据,数据内容从0开始累加,即形成连续发送数据功能;该功能的作用是配合PC端测试网络极限速率,打开电脑端的资源管理器,查看网卡,即可看到通信速率;值得注意的是,该方法并不能真实反映网速,用更为专业的网速测试软件为佳;

IP地址修改

每套工程均可修改FPGA开发板的IP地址、MAC地址、端口号等信息,同时也可以修改远程节点的IP地址、端口号等信息,当IPVX_ADDR_LOOP设置为1时,不需要指定远程节点的IP地址,这也是默认的工作方式,代码里有注释,如下:

TCP/IP 协议栈RTL源码版本–>工程源码架构

工程源码1~8为TCP/IP 协议栈源码版本,以工程源码1为例工程源码架构截图如下,其他工程与之类似:

TCP/IP 协议栈EDF网表版本–>工程源码架构

工程源码9~16为TCP/IP 协议栈源码版本,以工程源码9为例工程源码架构截图如下,其他工程与之类似:

4、工程源码1详解:Artix7-35T–RTL8211F–TCP协议栈源码版本

开发板FPGA型号:Xilinx–Artix7-35T–xc7a35tfgg484-2;

开发环境:Vivado2019.1;

输入输出:以太网帧,TCP网络数据;

接口:1路JR45千兆网口,1000M线速率;

网络PHY方案:RTL8211F–延时模式–RGMII时序;

MAC方案:Xilinx–Tri Mode Ethernet MAC方案;

协议层方案:1000M–TCP协议栈–服务器;

TCP协议栈是否提供源码?–>提供完整的源码;

工程源码架构请参考前面第3章节中的《TCP/IP 协议栈RTL源码版本–>工程源码架构》小节;

工程作用:此工程目的是让读者掌握FPGA实现 TCP/IP 协议栈 服务器版本的设计能力,以便能够移植和设计自己的项目;

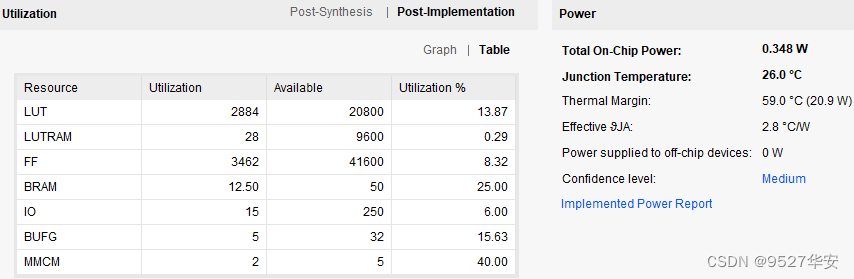

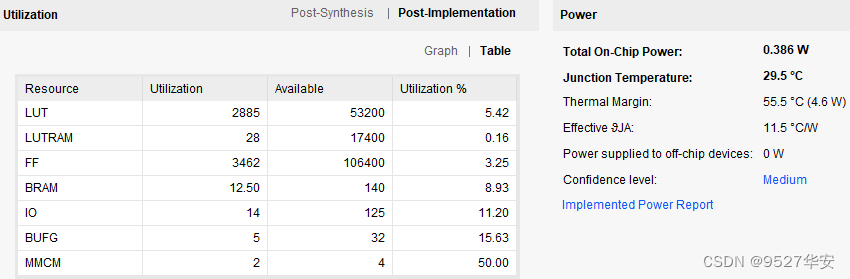

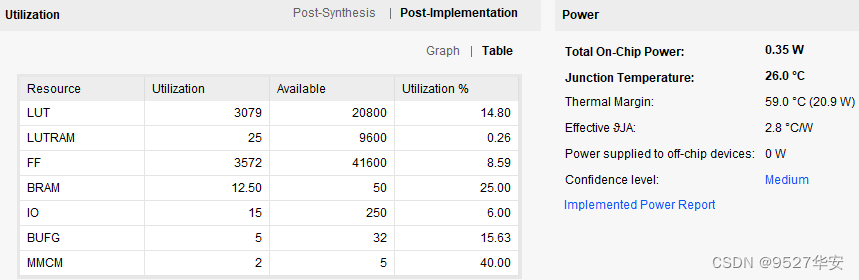

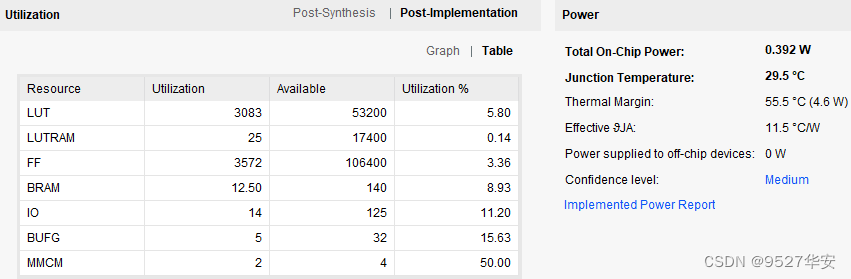

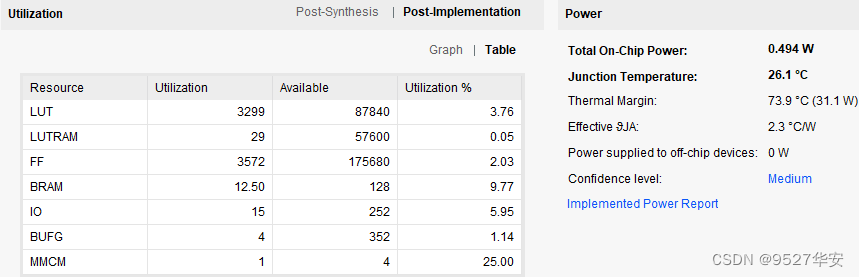

工程的资源消耗和功耗如下:

5、工程源码2详解:Artix7-35T–RTL8211E–TCP协议栈源码版本

开发板FPGA型号:Xilinx–Artix7-35T–xc7a35tfgg484-2;

开发环境:Vivado2019.1;

输入输出:以太网帧,TCP网络数据;

接口:1路JR45千兆网口,1000M线速率;

网络PHY方案:RTL8211E–延时模式–RGMII时序;

MAC方案:Xilinx–Tri Mode Ethernet MAC方案;

协议层方案:1000M–TCP协议栈–服务器;

TCP协议栈是否提供源码?–>提供完整的源码;

工程源码架构请参考前面第3章节中的《TCP/IP 协议栈RTL源码版本–>工程源码架构》小节;

工程作用:此工程目的是让读者掌握FPGA实现 TCP/IP 协议栈 服务器版本的设计能力,以便能够移植和设计自己的项目;

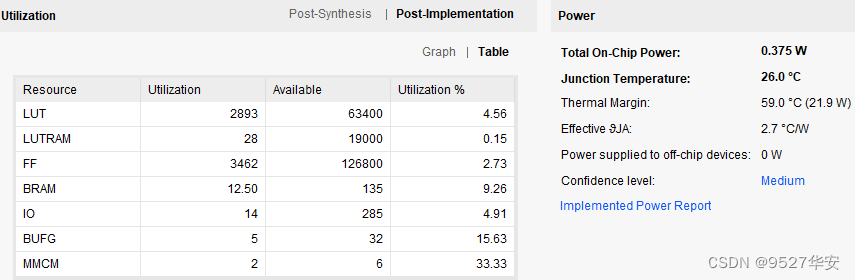

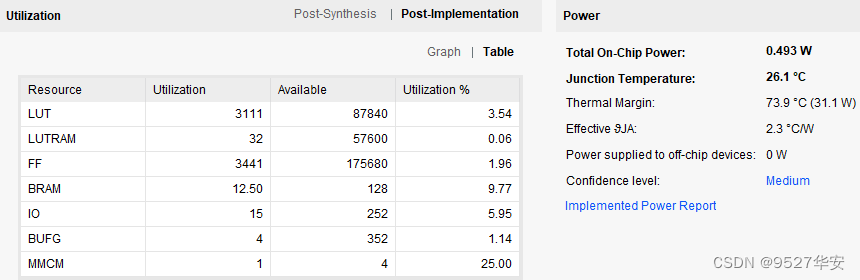

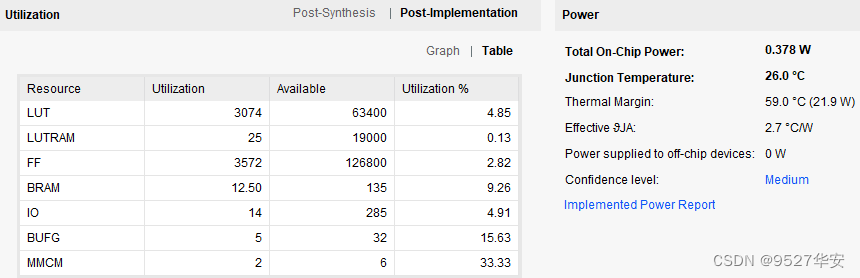

工程的资源消耗和功耗如下:

6、工程源码3详解:Artix7-35T–KSZ9031–TCP协议栈源码版本

开发板FPGA型号:Xilinx–Artix7-35T–xc7a35tfgg484-2;

开发环境:Vivado2019.1;

输入输出:以太网帧,TCP网络数据;

接口:1路JR45千兆网口,1000M线速率;

网络PHY方案:KSZ9031–延时模式–RGMII时序;

MAC方案:Xilinx–Tri Mode Ethernet MAC方案;

协议层方案:1000M–TCP协议栈–服务器;

TCP协议栈是否提供源码?–>提供完整的源码;

工程源码架构请参考前面第3章节中的《TCP/IP 协议栈RTL源码版本–>工程源码架构》小节;

工程作用:此工程目的是让读者掌握FPGA实现 TCP/IP 协议栈 服务器版本的设计能力,以便能够移植和设计自己的项目;

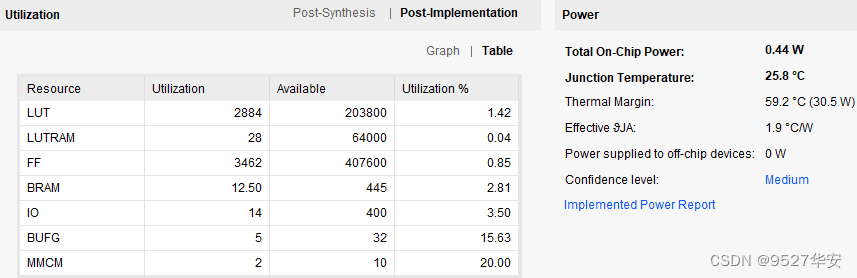

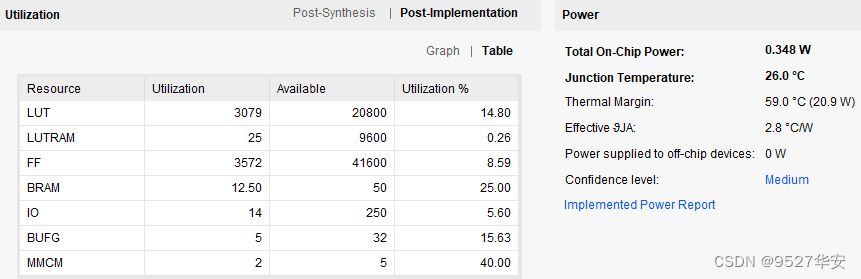

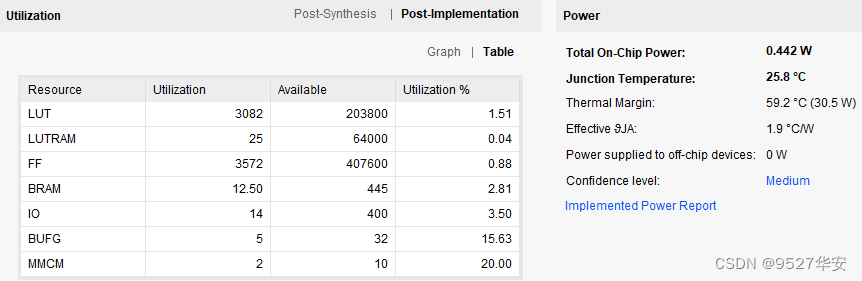

工程的资源消耗和功耗如下:

7、工程源码4详解:Artix7-100T–B50610–TCP协议栈源码版本

开发板FPGA型号:Xilinx–Artix7-100T–xc7a100tfgg484-2;

开发环境:Vivado2019.1;

输入输出:以太网帧,TCP网络数据;

接口:1路JR45千兆网口,1000M线速率;

网络PHY方案:B50610–延时模式–RGMII时序;

MAC方案:Xilinx–Tri Mode Ethernet MAC方案;

协议层方案:1000M–TCP协议栈–服务器;

TCP协议栈是否提供源码?–>提供完整的源码;

工程源码架构请参考前面第3章节中的《TCP/IP 协议栈RTL源码版本–>工程源码架构》小节;

工程作用:此工程目的是让读者掌握FPGA实现 TCP/IP 协议栈 服务器版本的设计能力,以便能够移植和设计自己的项目;

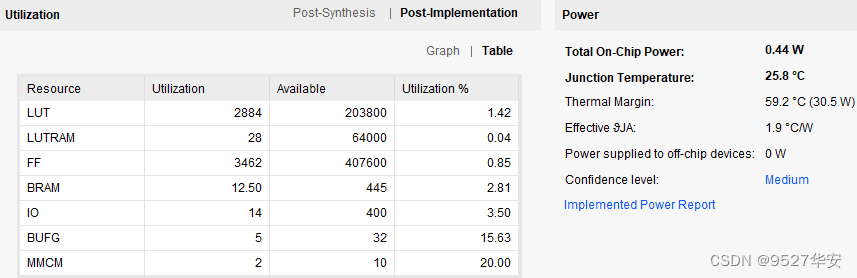

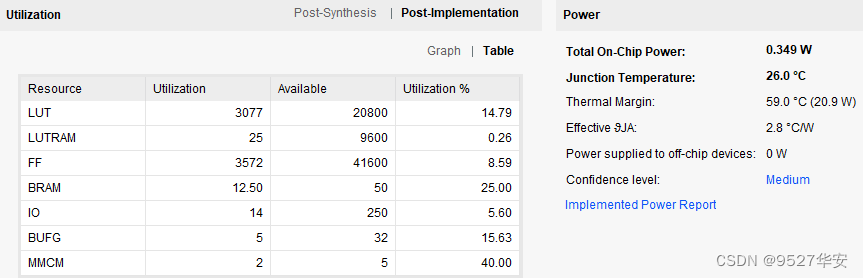

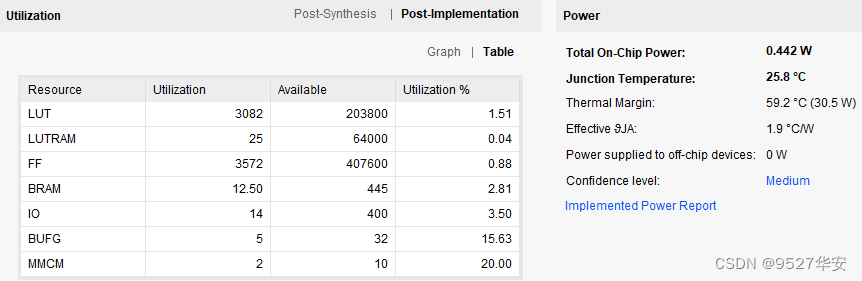

工程的资源消耗和功耗如下:

8、工程源码5详解:Kintex7-35T–B50610–TCP协议栈源码版本

开发板FPGA型号:Xilinx–Kintex7–35T–xc7k325tffg676-2;

开发环境:Vivado2019.1;

输入输出:以太网帧,TCP网络数据;

接口:1路JR45千兆网口,1000M线速率;

网络PHY方案:B50610–延时模式–RGMII时序;

MAC方案:Xilinx–Tri Mode Ethernet MAC方案;

协议层方案:1000M–TCP协议栈–服务器;

TCP协议栈是否提供源码?–>提供完整的源码;

工程源码架构请参考前面第3章节中的《TCP/IP 协议栈RTL源码版本–>工程源码架构》小节;

工程作用:此工程目的是让读者掌握FPGA实现 TCP/IP 协议栈 服务器版本的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

9、工程源码6详解:Kintex7-35T–88E1518–TCP协议栈源码版本

开发板FPGA型号:Xilinx–Kintex7–35T–xc7k325tffg676-2;

开发环境:Vivado2019.1;

输入输出:以太网帧,TCP网络数据;

接口:1路JR45千兆网口,1000M线速率;

网络PHY方案:88E1518–延时模式–RGMII时序;

MAC方案:Xilinx–Tri Mode Ethernet MAC方案;

协议层方案:1000M–TCP协议栈–服务器;

TCP协议栈是否提供源码?–>提供完整的源码;

工程源码架构请参考前面第3章节中的《TCP/IP 协议栈RTL源码版本–>工程源码架构》小节;

工程作用:此工程目的是让读者掌握FPGA实现 TCP/IP 协议栈 服务器版本的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

10、工程源码7详解:Zynq7020–B50610–TCP协议栈源码版本

开发板FPGA型号:Xilinx–Zynq7020–xc7z020clg400-2;

开发环境:Vivado2019.1;

输入输出:以太网帧,TCP网络数据;

接口:1路JR45千兆网口,1000M线速率;

网络PHY方案:B50610–延时模式–RGMII时序;

MAC方案:Xilinx–Tri Mode Ethernet MAC方案;

协议层方案:1000M–TCP协议栈–服务器;

TCP协议栈是否提供源码?–>提供完整的源码;

工程源码架构请参考前面第3章节中的《TCP/IP 协议栈RTL源码版本–>工程源码架构》小节;

工程作用:此工程目的是让读者掌握FPGA实现 TCP/IP 协议栈 服务器版本的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

11、工程源码8详解:Zynq XCZU4EV–RTL8211E–TCP协议栈源码版本

开发板FPGA型号:Xilinx- Zynq UltraScale+MPSoCs XCZU4EV–xczu4ev-sfvc784-2-i;

开发环境:Vivado2019.1;

输入输出:以太网帧,TCP网络数据;

接口:1路JR45千兆网口,1000M线速率;

网络PHY方案:RTL8211E–延时模式–RGMII时序;

MAC方案:Xilinx–Tri Mode Ethernet MAC方案;

协议层方案:1000M–TCP协议栈–服务器;

TCP协议栈是否提供源码?–>提供完整的源码;

工程源码架构请参考前面第3章节中的《TCP/IP 协议栈RTL源码版本–>工程源码架构》小节;

工程作用:此工程目的是让读者掌握FPGA实现 TCP/IP 协议栈 服务器版本的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

12、工程源码9详解:Artix7-35T–RTL8211F–TCP协议栈网表版本

开发板FPGA型号:Xilinx–Artix7-35T–xc7a35tfgg484-2;

开发环境:Vivado2019.1;

输入输出:以太网帧,TCP网络数据;

接口:1路JR45千兆网口,1000M线速率;

网络PHY方案:RTL8211F–延时模式–RGMII时序;

MAC方案:Xilinx–Tri Mode Ethernet MAC方案;

协议层方案:1000M–TCP协议栈–服务器;

TCP协议栈是否提供源码?–>否,提供TCP协议栈网表文件;

工程源码架构请参考前面第3章节中的《TCP/IP 协议栈EDF网表版本–>工程源码架构》小节;

工程作用:此工程目的是让读者掌握FPGA实现 TCP/IP 协议栈 服务器版本的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

13、工程源码10详解:Artix7-35T–RTL8211E–TCP协议栈网表版本

开发板FPGA型号:Xilinx–Artix7-35T–xc7a35tfgg484-2;

开发环境:Vivado2019.1;

输入输出:以太网帧,TCP网络数据;

接口:1路JR45千兆网口,1000M线速率;

网络PHY方案:RTL8211E–延时模式–RGMII时序;

MAC方案:Xilinx–Tri Mode Ethernet MAC方案;

协议层方案:1000M–TCP协议栈–服务器;

TCP协议栈是否提供源码?–>否,提供TCP协议栈网表文件;

工程源码架构请参考前面第3章节中的《TCP/IP 协议栈EDF网表版本–>工程源码架构》小节

工程作用:此工程目的是让读者掌握FPGA实现 TCP/IP 协议栈 服务器版本的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

14、工程源码11详解:Artix7-35T–KSZ9031–TCP协议栈网表版本

开发板FPGA型号:Xilinx–Artix7-35T–xc7a35tfgg484-2;

开发环境:Vivado2019.1;

输入输出:以太网帧,TCP网络数据;

接口:1路JR45千兆网口,1000M线速率;

网络PHY方案:KSZ9031–延时模式–RGMII时序;

MAC方案:Xilinx–Tri Mode Ethernet MAC方案;

协议层方案:1000M–TCP协议栈–服务器;

TCP协议栈是否提供源码?–>否,提供TCP协议栈网表文件;

工程源码架构请参考前面第3章节中的《TCP/IP 协议栈EDF网表版本–>工程源码架构》小节

工程作用:此工程目的是让读者掌握FPGA实现 TCP/IP 协议栈 服务器版本的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

15、工程源码12详解:Artix7-100T–B50610–TCP协议栈网表版本

开发板FPGA型号:Xilinx–Artix7-100T–xc7a100tfgg484-2;

开发环境:Vivado2019.1;

输入输出:以太网帧,TCP网络数据;

接口:1路JR45千兆网口,1000M线速率;

网络PHY方案:B50610–延时模式–RGMII时序;

MAC方案:Xilinx–Tri Mode Ethernet MAC方案;

协议层方案:1000M–TCP协议栈–服务器;

TCP协议栈是否提供源码?–>否,提供TCP协议栈网表文件;

工程源码架构请参考前面第3章节中的《TCP/IP 协议栈EDF网表版本–>工程源码架构》小节

工程作用:此工程目的是让读者掌握FPGA实现 TCP/IP 协议栈 服务器版本的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

16、工程源码13详解:Kintex7-35T–B50610–TCP协议栈网表版本

开发板FPGA型号:Xilinx–Kintex7–35T–xc7k325tffg676-2;

开发环境:Vivado2019.1;

输入输出:以太网帧,TCP网络数据;

接口:1路JR45千兆网口,1000M线速率;

网络PHY方案:B50610–延时模式–RGMII时序;

MAC方案:Xilinx–Tri Mode Ethernet MAC方案;

协议层方案:1000M–TCP协议栈–服务器;

TCP协议栈是否提供源码?–>否,提供TCP协议栈网表文件;

工程源码架构请参考前面第3章节中的《TCP/IP 协议栈EDF网表版本–>工程源码架构》小节

工程作用:此工程目的是让读者掌握FPGA实现 TCP/IP 协议栈 服务器版本的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

17、工程源码14详解:Kintex7-35T–88E1518–TCP协议栈网表版本

开发板FPGA型号:Xilinx–Kintex7–35T–xc7k325tffg676-2;

开发环境:Vivado2019.1;

输入输出:以太网帧,TCP网络数据;

接口:1路JR45千兆网口,1000M线速率;

网络PHY方案:88E1518–延时模式–RGMII时序;

MAC方案:Xilinx–Tri Mode Ethernet MAC方案;

协议层方案:1000M–TCP协议栈–服务器;

TCP协议栈是否提供源码?–>否,提供TCP协议栈网表文件;

工程源码架构请参考前面第3章节中的《TCP/IP 协议栈EDF网表版本–>工程源码架构》小节

工程作用:此工程目的是让读者掌握FPGA实现 TCP/IP 协议栈 服务器版本的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

18、工程源码15详解:Zynq7020–B50610–TCP协议栈网表版本

开发板FPGA型号:Xilinx–Zynq7020–xc7z020clg400-2;

开发环境:Vivado2019.1;

输入输出:以太网帧,TCP网络数据;

接口:1路JR45千兆网口,1000M线速率;

网络PHY方案:B50610–延时模式–RGMII时序;

MAC方案:Xilinx–Tri Mode Ethernet MAC方案;

协议层方案:1000M–TCP协议栈–服务器;

TCP协议栈是否提供源码?–>否,提供TCP协议栈网表文件;

工程源码架构请参考前面第3章节中的《TCP/IP 协议栈EDF网表版本–>工程源码架构》小节

工程作用:此工程目的是让读者掌握FPGA实现 TCP/IP 协议栈 服务器版本的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

19、工程源码16详解:Zynq XCZU4EV–RTL8211E–TCP协议栈网表版本

开发板FPGA型号:Xilinx- Zynq UltraScale+MPSoCs XCZU4EV–xczu4ev-sfvc784-2-i;

开发环境:Vivado2019.1;

输入输出:以太网帧,TCP网络数据;

接口:1路JR45千兆网口,1000M线速率;

网络PHY方案:RTL8211E–延时模式–RGMII时序;

MAC方案:Xilinx–Tri Mode Ethernet MAC方案;

协议层方案:1000M–TCP协议栈–服务器;

TCP协议栈是否提供源码?–>否,提供TCP协议栈网表文件;

工程源码架构请参考前面第3章节中的《TCP/IP 协议栈EDF网表版本–>工程源码架构》小节

工程作用:此工程目的是让读者掌握FPGA实现 TCP/IP 协议栈 服务器版本的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

20、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

21、上板调试验证并演示

准备工作

试验需要准备以下设备:

FPGA开发板,可以自行购买,也可以找本博主购买同款开发板;

测试电脑;

千兆网线;

网络调试助手;

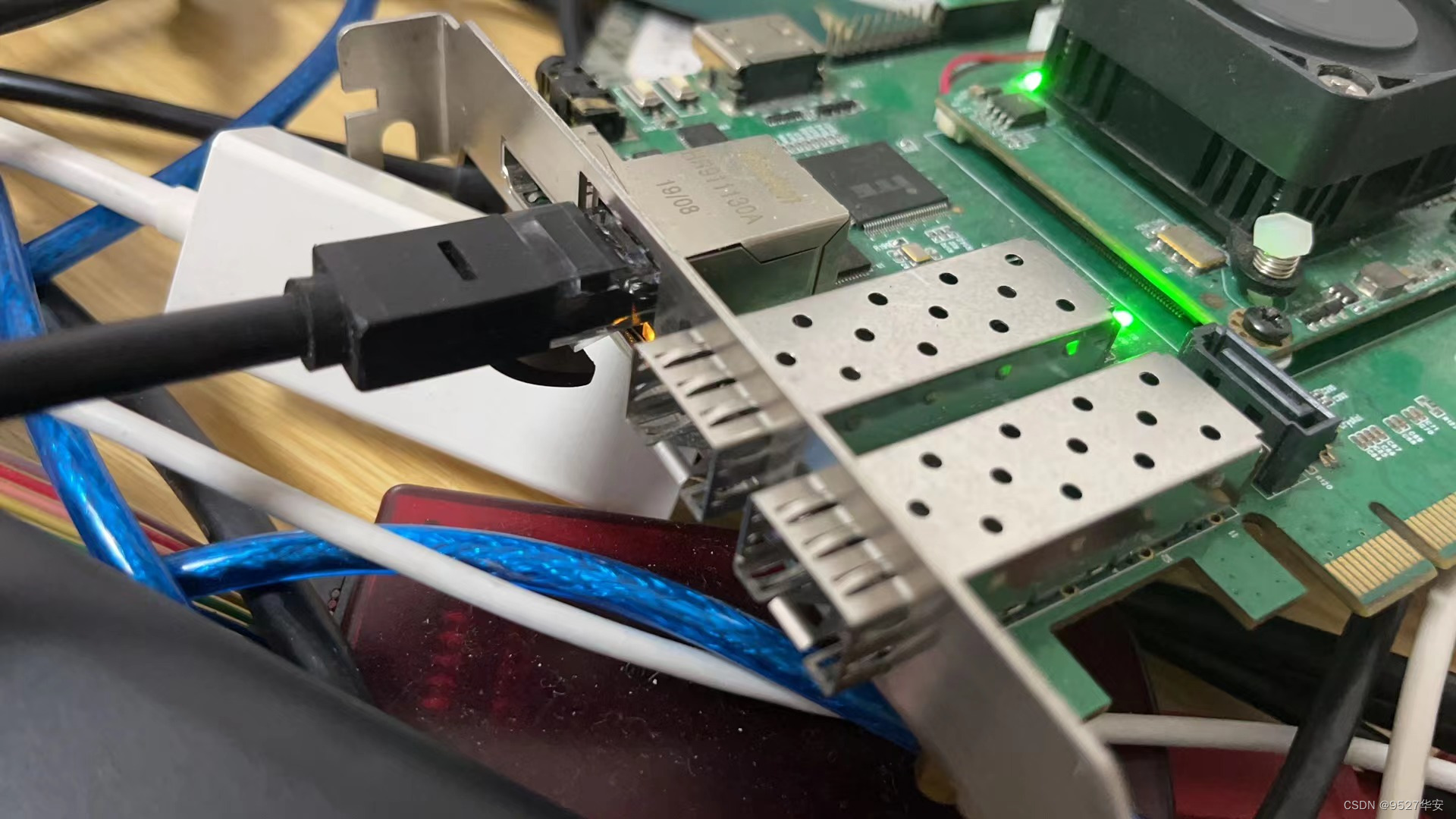

以工程源码5的开发板为例进行上板调试;

连接如下:

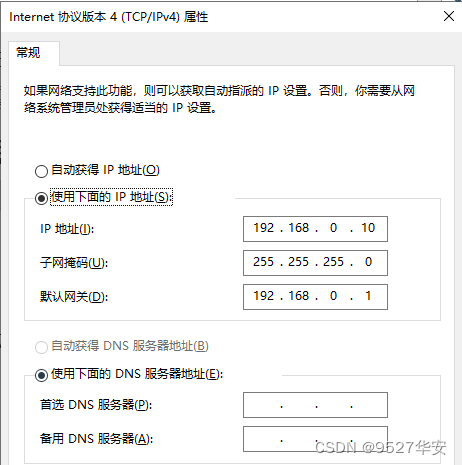

首先设置电脑端IP如下:

注意!!!

注意!!!

由于代码里设置了远端IP地址自回环,所以只需要将电脑端IP地址设为与FPGA网卡IP地址同网段且不重合即可,比如这里不仅可以设置微192.168.0.10,还可以设为192.168.0.100、192.168.0.101、192.168.0.102等,但不可设置为192.168.0.56,因为这是FPGA网卡的IP地址;

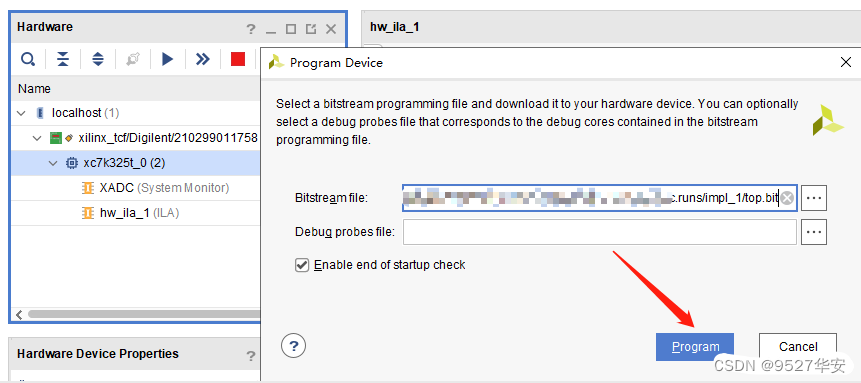

然后下载bit,如下:

ping测试

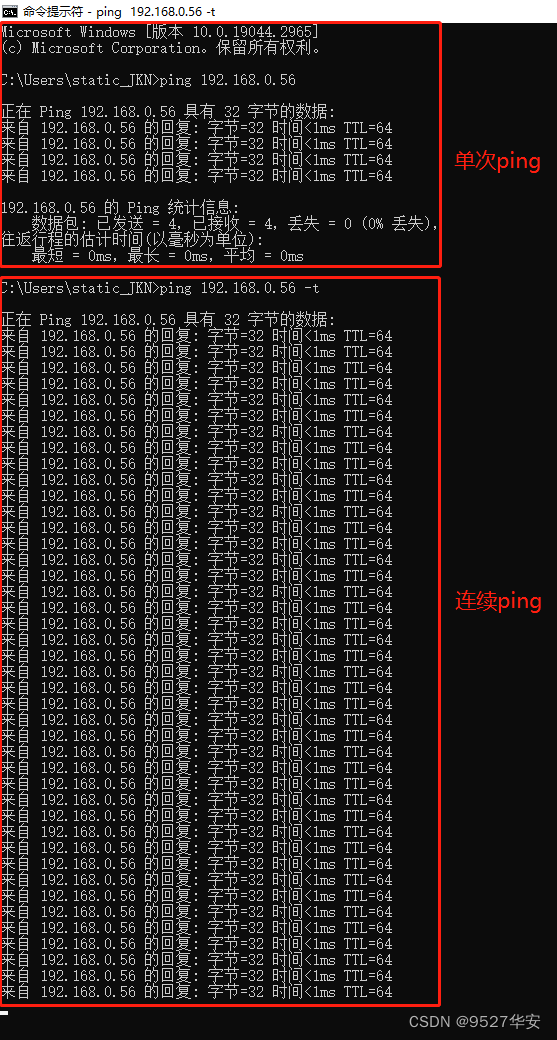

打开cdm,输入 ping 192.168.0.56,如下:

ping测试视频演示如下,请点击观看:

千兆网TCP协议栈ping操作

TCP数据回环测试

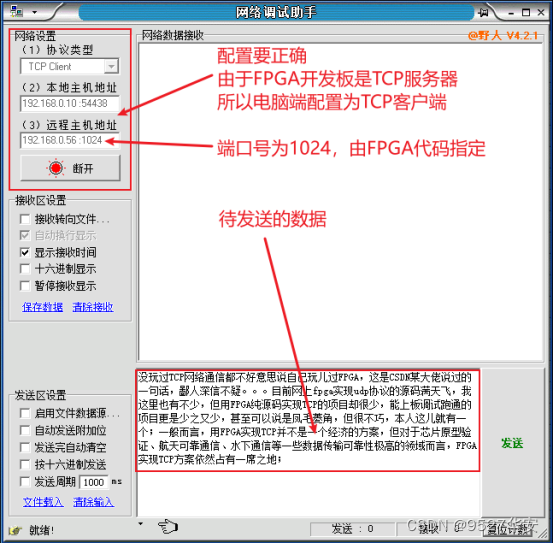

打开网络调试助手并配置,如下:

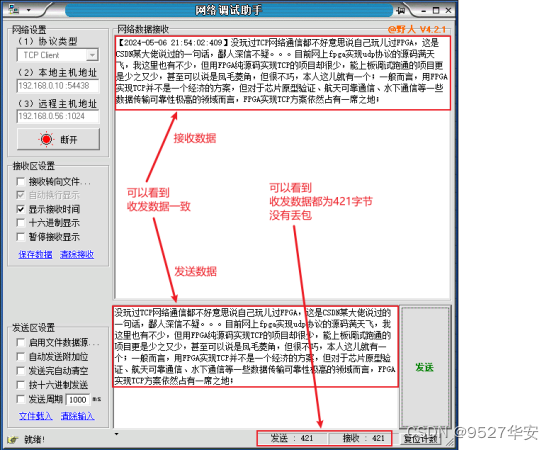

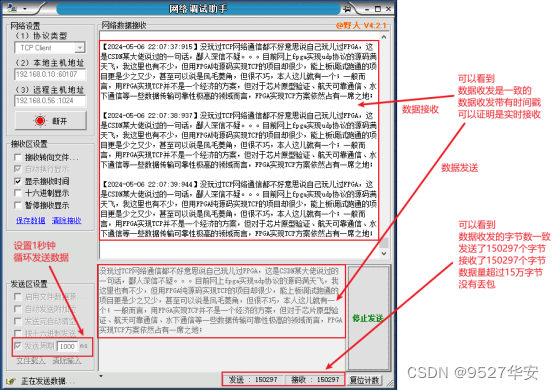

单次发送数据测试结果如下:

循环发送数据测试结果如下,1秒时间间隔循环:可以看到,数据收发量超过15万字节,没有丢包,足以证明其稳定性;

TCP数据回环测试视频演示如下,请点击观看:

千兆网TCP协议栈服务器数据收发测试

22、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

此外,有很多朋友给本博主提了很多意见和建议,希望能丰富服务内容和选项,因为不同朋友的需求不一样,所以本博主还提供以下服务: