热门标签

热门文章

- 1听GPT 讲Rust源代码--compiler(19)

- 2android日历价格控件,Android 自定义价格日历控件

- 3pythoncount函数怎么用_python中count函数简单的实例讲解

- 4Pandas数据处理(一)_df.head()函数作用

- 5刷新多个SOTA!最新Mamba魔改版本超越transformer,GPU内存消耗减少74%_graph-mamba

- 6多模态学习 - 视觉语言预训练综述-2023-下游任务、数据集、基础知识、预训练任务、模型_视频多模态下游任务

- 7【anaconda报错】CondaSSLError: OpenSSL appears to be unavailable on this machine.问题记录与解决方法

- 8【JPA】@OneToOne 一对一双向关联注解_@onetoone注解

- 9[python] 使用sqlparse 解析和美化SQL_python sqlparse

- 10python数据可视化seaborn_Python数据可视化matplotlib和seaborn

当前位置: article > 正文

Vivado VIO IP核(Virtual Input/Output)的使用_vivado vio数据输出

作者:Gausst松鼠会 | 2024-05-06 09:25:34

赞

踩

vivado vio数据输出

前言

在Aurora通信工程中,有一个专门产生Aurora数据包的模块,该模块在Aurora ip准备好后会自动根据计数器产生发送的数据包。

但现在希望能实时地控制数据包的发送以及中断,这时候可以采用vivado的vio ip核处理。

VIO IP

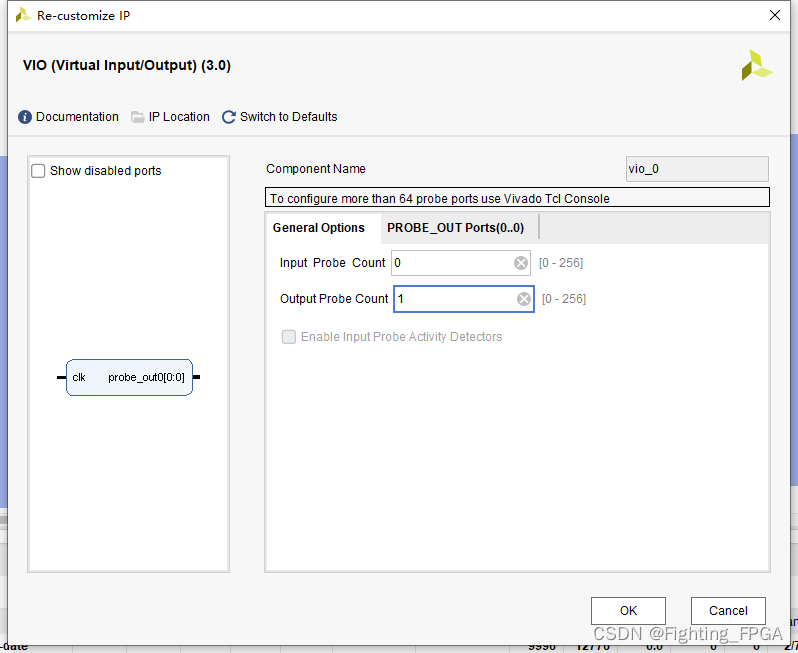

调用VIO IP核可以实时监控和驱动FPGA内部的信号,另外输入和输出端口的数量和宽度是可以设置的,其中输入输出端口的数量支持0-256;位宽支持1-256。

注意VIO IP核时钟与被监控或驱动信号的同步,即时钟应该连接被监控或驱动信号的时钟域。

比如我们输出一个监控信号package_vio,用于驱动实时发包。因此在IP核中配置输出数量=1.

在Probe width配置该信号的位宽 = 1.

在vio ip核模板上进行实例化,其时钟与Aurora发包时钟域相同,输出的package_vio作用发包的使能信号即可。

//vio_0 u_vio_0

// (

// .clk (sCLK_50M ),

// .probe_out0 (package_vio )

// );

- 1

- 2

- 3

- 4

- 5

至此,即可生成bit文件,并下载到板卡中,然后手动调节package_vio信号,来实现数据包的实时发送和关闭。默认为0,调至1表示发包,调回0表示结束发包。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Gausst松鼠会/article/detail/543570

推荐阅读

相关标签