- 1Day81.Git: 常用命令、分支、Gitee远程库、团队冲突、SSH公钥、IDEA集成Git_gitee ssh

- 2iconify的使用_@iconify

- 3【C语言】GCC相关常识

- 4IDEA远程DeBug调试_idea 远程调试_idea 远程debug

- 52022 年,中国光伏走入 “ 平价时代 “_光伏平价化

- 6MySQL基础(2)----DDL DML DQL语言完成数据库的增删改查操作 数据备份(导入导出sql包) 单表查询_熟练掌握mysql数据库ddl,del语句,对数据表进行增删改查。

- 7不要为鸿蒙的Http访问发愁了,因为我为你封装了工具类~

- 8中国蚁剑(antSword)下载、安装、使用教程

- 9Bert模型输入输出大揭秘_bert模型的输入输出

- 10四足仿生机器人--基本原理及开发教程习题答案_四足仿生机器人基本原理及开发教程

BRAM底层原理详细解释(1)

赞

踩

目录

3.1 字节写使能(Byte-Write Enable)- WEA and WEBWE:

3.2 地址总线—ADDRARDADDR and ADDRBWRADDR

3.3 数据总线—DIADI, DIPADIP, DIBDI, and DIPBDIP & DOADO, DOPADOP, DOBDO, and DOPBDOP

3.4 级联—CASCADEINA, CASCADEINB, CASCADEOUTA, and CASCADEOUTB

在阅读本文之前,建议对BRAM有一个基本的了解,可以先阅读:

FPGA原理与结构(8)——块RAM(Block RAM,BRAM)![]() https://ztzhang.blog.csdn.net/article/details/132253916

https://ztzhang.blog.csdn.net/article/details/132253916

一、原语

在xilinx 7 系列的FPGA中,有2个BRAM的原语:RAMB18E1,RAMB36E1。这两个就是所有BRAM配置的基本块,其他的BRAM原语和宏模块都是基于这两个原语的。

我们以RAMB36E1为例,下图展示了这个原语对应模块的具体结构:

二、端口简述

2.1 端口简介

RAMB36E1的输入输出端口含义如下:

| 端口名称 | 描述 | 在SDP模式下的映射 |

| DIADI[31:0] | 端口A的输入数据总线 | 详见下文SDP端口映射 |

|

DIPADIP[3:0]

| 端口A的输入校验总线 | 详见下文SDP端口映射 |

| DIBDI[31:0] | 端口B的输入数据总线 | 详见下文SDP端口映射 |

|

DIPBDIP[3:0]

| 端口B的输入校验总线 | 详见下文SDP端口映射 |

|

ADDRARDADDR [15:0]

| 端口A的地址总线 | 读地址总线 |

|

ADDRBWRADDR[15:0]

| 端口B的地址总线 | 写地址总线 |

|

WEA[3:0]

| 端口A的字节位写使能 | 不使用 |

|

WEBWE[7:0]

| 端口B的字节位写使能 | 字节位写使能 |

|

ENARDEN

| 端口A使能信号 | 写使能 |

|

ENBWREN

| 端口B使能信号 | 读使能 |

|

RSTREGARSTREG

| 同步输出寄存器A置位/复位 | 同步输出寄存器置位/复位 |

|

RSTREGB

| 同步输出寄存器B置位/复位 | |

|

RSTRAMARSTRAM

| 同步输出锁存器A置位/复位 | 同步输出锁存器置位/复位 |

|

RSTRAMB

| 同步输出锁存器B置位/复位 | |

|

CLKARDCLK

| 端口A时钟输入 | 读时钟 |

|

CLKBWRCLK

| 端口B时钟输入 | 写时钟 |

|

REGCEAREGCE

| 端口A输出寄存器时钟使能 | 输出寄存器时钟使能 |

|

REGCEB

| 端口B输出寄存器时钟使能 | |

|

CASCADEINA

| 端口A级联输入 | 不使用 |

|

CASCADEINB

| 端口B级联输入 | 不使用 |

|

CASCADEOUTA

| 端口A级联输出 | 不使用 |

|

CASCADEOUTB

| 端口B级联输出 | 不使用 |

|

DOADO[31:0]

| 端口A输出数据总线 | 详见下文SDP端口映射 |

|

DOPADOP[3:0]

| 端口A输出校验总线 | 详见下文SDP端口映射 |

|

DOBDO[31:0]

| 端口B输出数据总线 | 详见下文SDP端口映射 |

|

DOPBDOP[3:0]

| 端口B输出校验总线 | 详见下文SDP端口映射 |

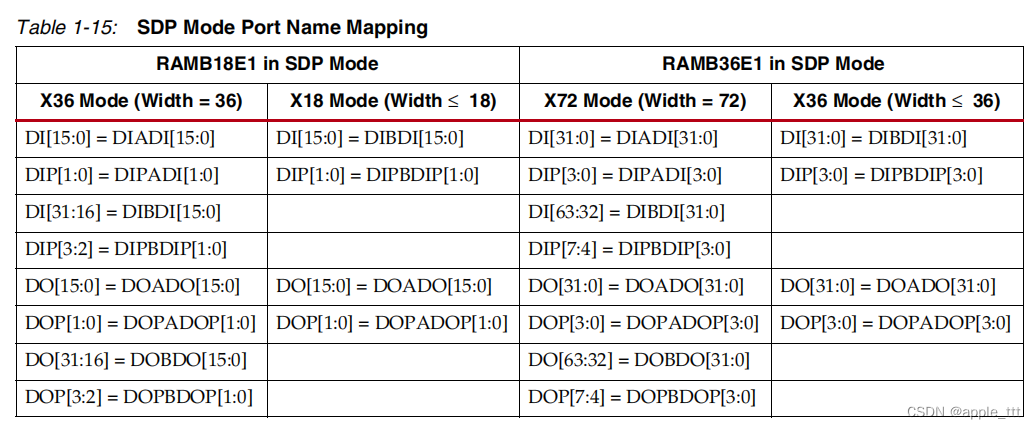

2.2 SDP端口映射

三、端口信号含义补充说明

3.1 字节写使能(Byte-Write Enable)- WEA and WEBWE:

字节写使能信号,表示了写操作时的哪个(或多个)字节是有效的,这个信号的极性不可配置(高有效)。

同时,写使能信号(WE)经常和使能信号(EN)配合使用。使能信号(EN)有效的情况下,写使能(WE)有效,进行写操作;写使能(WE)无效,进行读操作。这是针对单个端口而言的,对于单个端口,不可能同时发生读写,但是对一个BRAM的两个端口,就可能会发生读写冲突,因此需要考虑工作模式。

工作模式:根据工作模式(WRITE_FIRST, READ_FIRST, NO_CHANGE),输出锁存器(output latches)将被加载或不加载。这决定了在写操作中数据是如何被处理的:

- WRITE_FIRST:写操作首先发生,之后可能跟着一个读取操作。

- READ_FIRST:首先读取当前存储器内容,然后写入新的数据。

- NO_CHANGE:如果没有写入操作,则输出保持不变。

3.2 地址总线—ADDRARDADDR and ADDRBWRADDR

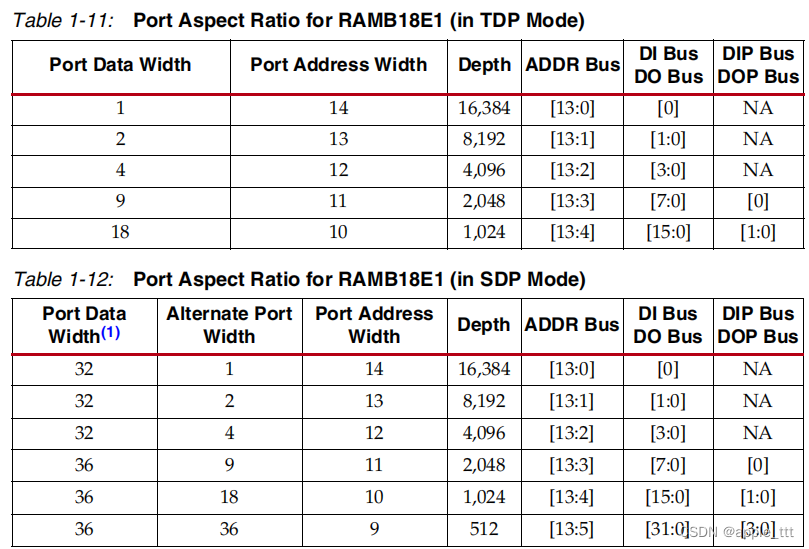

对于RAMB18E1来说,地址总线的设置如下:

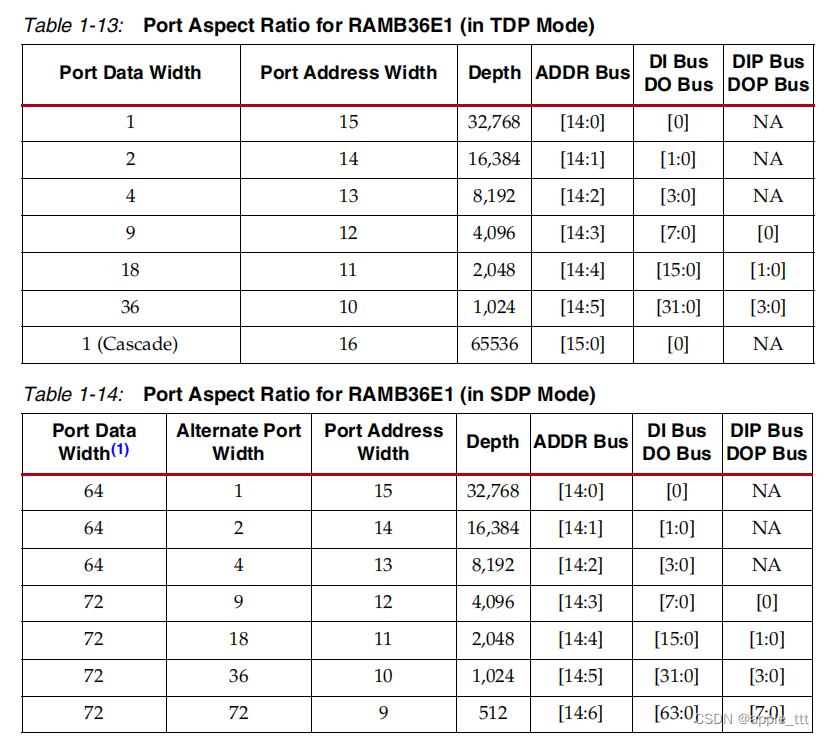

对于RAMB36E1来说,地址总线的设置如下:

值得注意的是,我们以RAMB18E1为例,它的地址总线的位宽为14bit,当端口的宽度被设置为1,地址总线位宽为14。这时,地址深度可以达到 = 16384 = 16Kb(K代表1024)。这就解释了为什么一个18Kb的BRAM根据深度和位宽的不同,可以配置成如下形式(深度×位宽):16K x 1, 8K x2 , 4K x 4, 2K x 9, 1K x 18 or 512 x 36。这里的16K × 1 ≠ 18K。同理,可以解释其他一系列的情况。

3.3 数据总线—DIADI, DIPADIP, DIBDI, and DIPBDIP & DOADO, DOPADOP, DOBDO, and DOPBDOP

我们当就一个端口来看,例如A端口,和数据有关的总线总共有4条,分别是DIADI,DIPADIP,DOPDO,DOPADOP。这又可以分成:

- 输入:DIADI,DIPADIP

- 输出:DOPDO,DOPADOP

单独就输入进行分析,DIADI[31:0]代表的是常规数据输入总线,DIPADIP[3:0]代表的是奇偶校验数据输入总线。但是其实,DIPADIP[3:0]是可以灵活配置实现的,它可以存储奇偶校验/纠错位或作为额外的数据位。这也就是为什么在使用RAMB36E1时,输入位宽可以被配置为36bit,而不是DIADI的32bit。

这样做有很多的好处:

- 数据和校验位的分离:通过为数据位和奇偶校验位(或错误校正位)提供独立的总线,设计可以更灵活地处理数据和校验信息。这对于某些需要高数据完整性和错误检测能力的应用尤其重要。

- 合并数据总线和校验总线:在一些设计中,常规数据总线与校验位总线可以合并,这样做可以简化设计并可能减少所需的硬件资源。无论是独立的还是合并的配置,读/写和存储操作对所有位来说都是相同的,包括奇偶校验位。

- 灵活性和可靠性:提供不同的数据宽度和校验配置增加了设计的灵活性,使设计师能够根据具体的应用需求和性能目标来优化存储器的结构。同时,包含奇偶校验或错误校正位的设计能够提高数据传输和存储过程中的可靠性。

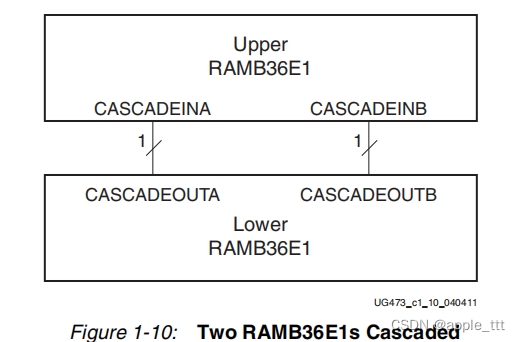

3.4 级联—CASCADEINA, CASCADEINB, CASCADEOUTA, and CASCADEOUTB

使用 CASCADEIN/CASCADEOUT 引脚将两个块 RAM (Block RAM,BRAM)连接起来,形成 64K x 1 模式,是一种扩展存储容量和功能的方法。这种配置允许两个BRAM单元串联工作,通过将一个BRAM的CASCADEOUT引脚连接到另一个BRAM的CASCADEIN引脚上实现。在这种模式下,上面的BRAM单元接收来自下面BRAM单元的数据输出,使得两个BRAM单元可以作为一个更大的存储器单元来使用。

当不使用级联模式时,CASCADEIN/CASCADEOUT引脚不需要连接。这种配置提供了灵活性,允许设计师根据需要启用或禁用级联功能。值得注意的是,级联功能仅在双端口(TDP)模式下可用,这意味着每个BRAM单元可以独立地支持读写操作,使得级联配置在处理复杂数据结构或增加存储容量时非常有用。

级联BRAM提供了一种有效的方法来增加FPGA设计中的存储密度和灵活性,特别是在需要大量存储空间但又希望保持高速数据访问的应用中。通过使用级联技术,设计师可以创建更大、更复杂的存储解决方案,以满足特定的系统需求。