- 1中国跨过数据库这座大山了吗?

- 2垂直起降飞行器的设计与控制:固定翼和四旋翼整合自主飞行研究(Matlab代码实现)_vtol matlab

- 3springboot校园便利平台

- 4好程序员:学Java真的找不到工作吗?2023年Java就业情况如何?_java还能找到工作吗

- 5python中tkinter使用text组件添加多行文本并自动换行、添加多行文字、添加按钮、添加图片_tkinter 文本框添加按钮

- 6RocketMQ消息发送常见错误与解决方案_defaultmqproducer send exception

- 7Java使用POI导出Excel_java poi导出excel

- 8在无字体时使用word样式,并设置字体样式_xwpfstyles

- 9苹果iOS设备解锁软件:iToolab UnlockGo_强制解除苹果监管锁的软件

- 107 年+积累、 Elastic 创始人Shay Banon 等 15 位专家推荐的 Elasticsearch 8.X新书已上线...

基于FPGA的ALU计算器verilog实现_verilog实现alu

赞

踩

欢迎订阅《FPGA学习入门100例教程》、《MATLAB学习入门100例教程》

目录

一、理论基础

Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。 Verilog HDL和VHDL是世界上最流行的两种硬件描述语言,都是在20世纪80年代中期开发出来的。前者由Gateway Design Automation公司(该公司于1989年被Cadence公司收购)开发。两种HDL均为IEEE标准。

Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。

Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。所有这些都使用同一种建模语言。此外,Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。

Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。语言从C编程语言中继承了多种操作符和结构。Verilog HDL提供了扩展的建模能力,其中许多扩展最初很难理解。但是,Verilog HDL语言的核心子集非常易于学习和使用,这对大多数建模应用来说已经足够。当然,完整的硬件描述语言足以对从最复杂的芯片到完整的电子系统进行描述。

利用verilog语言设计微处理器的算术逻辑电路,对电路进行合理规划和尽可能的优化。

(1) 能够完成16位有符号数的算术逻辑运算。

(2)设计独立矩阵键盘和功能键,辅助完成功能验证。

(3) 采用适当的形式显示结果。

二、核心程序

- module keys(

- s0,//1

- s1,//2

- s2,//3

- s3,//+

- s4,//4

- s5,//5

- s6,//6

- s7,//-

- s8,//7

- s9,//8

- s10,//9

- s11,//*

- s12,//0

- s13,//=

- s14,//SIGN

- s15,///

- num,

- fadd,

- fsub,

- fmult,

- fdiv,

- fsig,

- fequ

- );

-

- input s0;

- input s1;

- input s2;

- input s3;

-

- input s4;

- input s5;

- input s6;

- input s7;

-

- input s8;

- input s9;

- input s10;

- input s11;

-

- input s12;

- input s13;

- input s14;

- input s15;

-

-

-

- output[3:0]num;

- output fadd;

- output fsub;

- output fmult;

- output fdiv;

- output fsig;

- output fequ;

-

- reg[3:0]num =4'b0000;

- reg fadd =1'b0;

- reg fsub =1'b0;

- reg fmult=1'b0;

- reg fdiv =1'b0;

- reg fsig =1'b0;

- reg fequ =1'b0;

- wire[15:0] control;

- assign control={s15,s14,s13,s12,s11,s10,s9,s8,s7,s6,s5,s4,s3,s2,s1,s0};

- always @(s0 or s1 or s2 or s3 or s4 or s5 or s6 or s7 or s8 or s9 or s10 or s11 or s12 or s13 or s14 or s15)

- begin

- case(control)

- 16'b0000_0000_0000_0001:begin

- num =4'd1;

- fadd =1'b0;

- fsub =1'b0;

- fmult=1'b0;

- fdiv =1'b0;

- fsig =1'b0;

- fequ =1'b0;

- end

- 16'b0000_0000_0000_0010:begin

- num =4'd2;

- fadd =1'b0;

- fsub =1'b0;

- fmult=1'b0;

- fdiv =1'b0;

- fsig =1'b0;

- fequ =1'b0;

- end

- 16'b0000_0000_0000_0100:begin

- num =4'd3;

- fadd =1'b0;

- fsub =1'b0;

- fmult=1'b0;

- fdiv =1'b0;

- fsig =1'b0;

- fequ =1'b0;

- end

- 16'b0000_0000_0000_1000:begin

- num =4'd0;

- fadd =1'b1;

- fsub =1'b0;

- fmult=1'b0;

- fdiv =1'b0;

- fsig =1'b0;

- fequ =1'b0;

- end

- 16'b0000_0000_0001_0000:begin

- num =4'd4;

- fadd =1'b0;

- fsub =1'b0;

- fmult=1'b0;

- fdiv =1'b0;

- fsig =1'b0;

- fequ =1'b0;

- end

- 16'b0000_0000_0010_0000:begin

- num =4'd5;

- fadd =1'b0;

- fsub =1'b0;

- fmult=1'b0;

- fdiv =1'b0;

- fsig =1'b0;

- fequ =1'b0;

- end

- 16'b0000_0000_0100_0000:begin

- num =4'd6;

- fadd =1'b0;

- fsub =1'b0;

- fmult=1'b0;

- fdiv =1'b0;

- fsig =1'b0;

- fequ =1'b0;

- end

- 16'b0000_0000_1000_0000:begin

- num =4'd0;

- fadd =1'b0;

- fsub =1'b1;

- fmult=1'b0;

- fdiv =1'b0;

- fsig =1'b0;

- fequ =1'b0;

- end

-

- 16'b0000_0001_0000_0000:begin

- num =4'd7;

- fadd =1'b0;

- fsub =1'b0;

- fmult=1'b0;

- fdiv =1'b0;

- fsig =1'b0;

- fequ =1'b0;

- end

- 16'b0000_0010_0000_0000:begin

- num =4'd8;

- fadd =1'b0;

- fsub =1'b0;

- fmult=1'b0;

- fdiv =1'b0;

- fsig =1'b0;

- fequ =1'b0;

- end

- 16'b0000_0100_0000_0000:begin

- num =4'd9;

- fadd =1'b0;

- fsub =1'b0;

- fmult=1'b0;

- fdiv =1'b0;

- fsig =1'b0;

- fequ =1'b0;

- end

- 16'b0000_1000_0000_0000:begin

- num =4'd0;

- fadd =1'b0;

- fsub =1'b0;

- fmult=1'b1;

- fdiv =1'b0;

- fsig =1'b0;

- fequ =1'b0;

- end

-

-

-

-

- 16'b0001_0000_0000_0000:begin

- num =4'd0;

- fadd =1'b0;

- fsub =1'b0;

- fmult=1'b0;

- fdiv =1'b0;

- fsig =1'b0;

- fequ =1'b0;

- end

- 16'b0010_0000_0000_0000:begin

- num =4'd0;

- fadd =1'b0;

- fsub =1'b0;

- fmult=1'b0;

- fdiv =1'b0;

- fsig =1'b0;

- fequ =1'b1;

- end

- 16'b0100_0000_0000_0000:begin

- num =4'd0;

- fadd =1'b0;

- fsub =1'b0;

- fmult=1'b0;

- fdiv =1'b0;

- fsig =1'b1;

- fequ =1'b0;

- end

- 16'b1000_0000_0000_0000:begin

- num =4'd0;

- fadd =1'b0;

- fsub =1'b0;

- fmult=1'b0;

- fdiv =1'b1;

- fsig =1'b0;

- fequ =1'b0;

- end

-

- default:begin

- num =4'd0;

- fadd =1'b0;

- fsub =1'b0;

- fmult=1'b0;

- fdiv =1'b0;

- fsig =1'b0;

- fequ =1'b0;

- end

- endcase

- end

-

-

- endmodule

三、测试结果

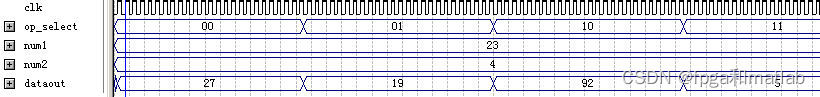

加法器的仿真:

其效果如下所示:

减法器的仿真:

乘法器的仿真:

除法器的仿真:

以上是四个运算器的设计,下面要将其整合,得到ALU控制器。

我们需要设计一个输入选择器用来识别我们输入的指令。

这个就是ALU控制器的核心模块,下面要对外部接口进行设计。

键盘我们在本系统设计的布局如下所示:

| 1 | 2 | 3 | + |

| 4 | 5 | 6 | - |

| 7 | 8 | 9 | * |

| 0 | = | Sign | / |

这个是典型的矩阵键盘。

0:1

1:2

2:3

3:+

4:4

5:5

6:6

7:-

8:7

9:8

10:9

11:*

12:0

13:=

14:sign

15:/

键盘的主要识别采用状态机来实现。

状态1:输入第一个数字

状态2:输入操作符号

状态3:输入第二个数字

状态4:等于

A02-39