- 1如何使用zxing扫描QR code(二维码)

- 2优设AI导航

- 3Awk by Example--转载

- 4计算机视觉实战项目2(单目测距+图像处理+路径规划+车牌识别)_图像识别 寻路

- 5豆瓣评分预测(如何用自己的数据集进行文本分类)——基于pytorch的 BERT中文文本分类,超详细教程必会_bert做中文文本分类的具体过程

- 6使用Pytorch搭建CNN

- 7数据结构与算法分析(六)--- 分治与减治 + 分治排序与二分查找_分治和减治

- 8spring-cloud-kubernetes与SpringCloud Gateway_kubernates gateway spring cloud gateway

- 9多进程并发服务器

- 10双向bfs-leetcode127.单词接龙_双向bfs leetcode 127

Xilinx FPGA 学习笔记一-chipscope 无法观察信号 BUFG_chipscope 时钟 观测

赞

踩

转载请注明出处:http://blog.csdn.net/lg2lh/article/details/45323361

今天开始试着使用chipscope,写了一个简单的流水灯的例程,开始综合布线的时候没有问题,但是加上chipscope 以后,综合就总报错。

第一种情况:用chipscope不可以直接观察全局时钟信号,即BUFG信号-----X

错误如下:

ERROR:Place:1136 - This design contains a global buffer instance,

<PLL_u0/clkout1_buf>, driving the net, <CLK_OUT1>, that is driving the

following (first 30) non-clock load pins.

< PIN: CLK_OUT1_INV_1_o1_INV_0.A6; >

< PIN: U_ila_pro_0/U0/I_TQ0.G_TW[0].U_TQ.D; >

This is not a recommended design practice in Spartan-6 due to limitations in

the global routing that may cause excessive delay, skew or unroutable

situations. It is recommended to only use a BUFG resource to drive clock

loads. If you wish to override this recommendation, you may use the

CLOCK_DEDICATED_ROUTE constraint (given below) in the .ucf file to demote

this message to a WARNING and allow your design to continue.

< PIN "PLL_u0/clkout1_buf.O" CLOCK_DEDICATED_ROUTE = FALSE; >

ERROR:Pack:1654 - The timing-driven placement phase encountered an error.

这个错误找了一晚上,看到http://xilinx.eetrend.com/forum/6884 专家回复如下:

这个错误是提示你设计中将BUFG的输出连到了非时钟管脚,也就是ILA逻辑。在S6中,建议全局时钟输出只接时钟管脚,否则很难容易造成布线问题。 加CLOCK_DEDICATED_ROUTE的约束可以把这个错误降为告警,继续跑布局布线。需要注意的是,这个约束的作用并不是强制clk_we信号不通过BUFG,而是告诉工具忽略这类非优化的时钟资源使用问题。你可以通过FPGA Editor看到,clk_we还是上BUFG的。

意思就是正常情况下chipscope无法观察BUFG后的信号,但也并不是真的就不可以,专家说: 加CLOCK_DEDICATED_ROUTE的约束可以把这个错误降为告警

网友博客http://blog.163.com/unregistered@yeah/blog/static/88629551201452611949339中描述了具体这种方法的实现:

ERROR:Place:1136 - This design contains a global buffer instance,

<U_SYS_CLK/U_CLK/BUFG3>, driving the net, <clk100K>, that is driving the

following (first 30) non-clock load pins.

< PIN: U_ila_pro_0/U0/I_TQ0.G_TW[0].U_TQ.D; >

This is not a recommended design practice in Spartan-6 due to limitations in

the global routing that may cause excessive delay, skew or unroutable

situations. It is recommended to only use a BUFG resource to drive clock

loads. If you wish to override this recommendation, you may use the

CLOCK_DEDICATED_ROUTE constraint (given below) in the .ucf file to demote

this message to a WARNING and allow your design to continue.

< PIN "U_SYS_CLK/U_CLK/BUFG3.O" CLOCK_DEDICATED_ROUTE = FALSE; >

处理过程:

1.按照提示 在ucf文件中加入:

PIN "U_SYS_CLK/U_CLK/BUFG3.O" CLOCK_DEDICATED_ROUTE = FALSE;

但是抓取信号是,感觉这个时钟是50MHz时钟,而不我分频的100KHz时钟,抓取100KHz的信号竟然相同数据点出现了500个,果断怀疑有问题;

2.用ue打开chipscope.cdc文件,发现其中一行为:

Project.unit<0>.clockChannel=clk50M

而我并未在chipscope中加clk50M时钟,于是上面一条修改为:

Project.unit<0>.clockChannel=U_SYS_CLK clk100K

3.结果测试正常。

另外:bufg输出的时钟可以作为chipscope 时钟,但是不能作为数据监控,我们可以assign clk_temp=clk_bufg,监控clk_temp。这个我试了,好像不行

总之,chipscope不能直接观察BUFG的输出的全局时钟信号。

第二种情况 :FPGA的IO无法直接作为chipscope的采样时钟,否则会报如下入错,必须采用输入IBUF后的信号作为采样时钟,才不会报错。

ERROR:NgdBuild:924 - input pad net 'i_clk' is driving non-buffer primitives:

先看我的源码,其中i_clk和i_ip是不能直接做采样时钟的

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 19:26:57 04/11/2015

// Design Name:

// Module Name: TOP

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TOP(

i_clk,

i_ip,

o_clk,

o_led

);

input i_clk,i_ip;

output o_clk;

output reg o_led;

reg [7:0] delay_cnt;

wire CLK_OUT1;

(* KEEP="TRUE"*) wire CLK_OUT2;

always @(posedge i_clk)

begin

if(!i_ip)

delay_cnt <= 8'h00;

else if(delay_cnt==8'hff)

begin

delay_cnt <= 8'h00;

end

else

begin

delay_cnt <= delay_cnt+1'b1;

end

end

always @(posedge i_clk )

begin

if(delay_cnt==8'hff)

o_led <= ~o_led;

else

o_led <= o_led;

end

endmodule<span style="color:#ff0000;"><span style="background-color: rgb(255, 255, 255);">

</span></span>

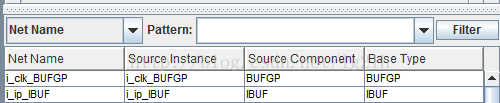

可以用

i_clk的IBUF信号i_clk_BUFGP或者ip的IBUF后的信号i_ip_IBUF.就不会报警了。

i_clk的IBUF信号i_clk_BUFGP或者ip的IBUF后的信号i_ip_IBUF.就不会报警了。

第三种情况:用chipscope不可以直接观察FPGA的IO,与第二种情况类似,第二种情况不可用于采样,这里是不可以用于观察和触发。报错也是一样的:

ERROR:NgdBuild:924 - input pad net 'i_ip' is driving non-buffer primitives:

同理观察相应的IBUF信号是可以的。但是如果这个IO为逻辑模块的时钟信号,其对应的IBUF也不能被观察。也就是i_ip_IBUF可以被观察,而i_clk_BUFGP不可以!!!