- 1Manjaro的安装与配置_manjaro哪个桌面环境好

- 2PCB设计时铜箔厚度,走线宽度和电流的关系_2oz铜厚可以多少电流

- 3在Git存储库中查找并恢复已删除的文件_为什么推送到git远程仓库的文件会显示被delete了

- 4【vue-2】v-on、v-show、v-if及按键修饰符

- 5【AIGC调研系列】通义千问、文心一言、抖音云雀、智谱清言、讯飞星火的特点分析_通义千问和文心一言哪个更好用

- 6Host头攻击-使用加密和身份验证机制

- 7欠薪6个月:外包公司干(混)了4年,我决定换个活法

- 8数字温度传感器-DS18B20_ds18b20温度传感器csdn

- 9使用cloudreve搭建个人网盘

- 10idea所有子模块启动都出现Error:Kotlin: Module was compiled with an incompatible version of Kotlin.报错

FPGA设计时序约束六、设置最大/最小时延_fpga net delay过大

赞

踩

目录

一、背景

在设计中,有时需要限定路径的最大时延和最小时延,如没有特定时钟关系的异步信号,但需要限制最大时延和最小时延,也可以对端口到端口(中间无寄存器)的路径设置最大时延和最小时延,设置最大时延和最小时延会影响当前的setup和hold时序分析。

二、Max/Min_delay约束

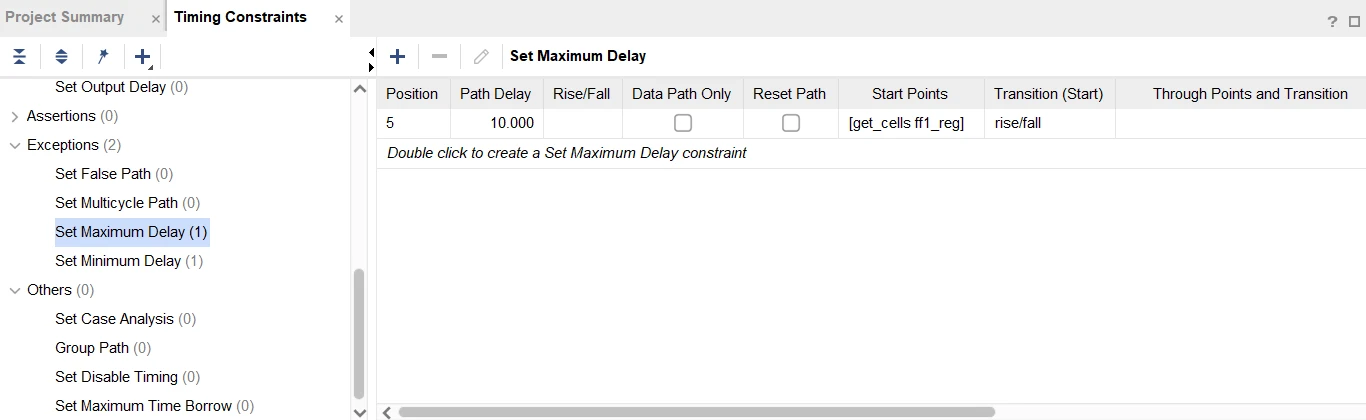

设置路径最大时延和最小时延的命令为set_max_delay,set_min_delay,可在Timing Constraints窗口进入Exceptions中,选择Set Maximum Delay或Set Minimum Delay,即为选择最大时延或最小时延。

2.1 约束设置参数

以设置最大时延为例,双击Set Maximum Delay进入设置窗口

Targets设置

Specify path delay:设置路径最大时延值,可为正整数或负整数

From:设置路径的起点,对象可以是Clocks,Cells,Cell pins,I/O ports

Through:设置路径的中间经过点,对象可以是Net,Cells,Cell pins

To:设置路径的终点,对象可以是Clocks,Cells,Cell pins,I/O ports

Options设置

Rise/Fall:勾选后可设置最大时延只对上升沿触发或下降沿触发的路径有效,未勾选时不区分边沿触发。

Set Maximum...ignored):勾选后设置的时延约束只对数据路径有效,时钟偏斜和hold检查会被忽略,即等效于该路径也设置了set_false_path -hold约束,此时如果约束中设置了set_min_delay约束也不会生效。并且该设置不能用于set_min_delay约束中。

Remove...path delays:勾选后,如果设置的约束路径上有其他时例外约束(如false_path,multicycle约束,最大最小时延约束都将被移除)

2.2 约束说明

对于输入输出逻辑的约束,将不会使用set_max_delay/set_min_delay,对于输入端口到第一级寄存器或最后一级寄存器到输出端口的逻辑路径,通常使用set_input_delay

/set_output_delay约束,set_max_delay/set_min_delay通常用于约束输入端口和输出端口间的纯组合逻辑路径。

set_max_delay另一个常用的场景是没有时钟关系的异步信号,但需要设置最大时延。两个异步时钟路径可以使用set_clock_group或set_false_path,从而不会进行时序分析。当异步时钟间的设计合理,如FIFO中的两级同步寄存器,要放宽约束,保证两个时钟间的路径延时符合实际情况,就需要使用set_max_delay。

在多比特跨时钟域(CDC)场景中,比特之间的偏斜必须在一定要求时间内,虽然偏斜可以通过set_bus_skew来约束,但必须确保两个时钟域间的时延不能太大。此时可以通过约束set_max_delay -datapath_only代替set_false_path/set_clock_groups。

如果对于两个时钟域间的部分路径或全部路径的最大时延必须明确时,就必须使用set_max_delay -datapath_only约束。这种场景下,set_clock_groups不能用来定义两个时钟作为异步时钟,因为从约束的优先级角度看它将取代set_max_delay。其他跨时钟域路径就必须联合约束set_false_path或set_max_delay constraints.

2.3 路径分段

不同于约束文件XDC中的其他约束,在设置最大时延和最小时延中,参数-from和-to选项为设置约束的起点和终点,在设置时,有些起点和终点对于约束来说是无效的。当设置了一个无效的起点时,为了让节点成为一个有效的起点,时序分析工具会阻止时序路径通过该节点。

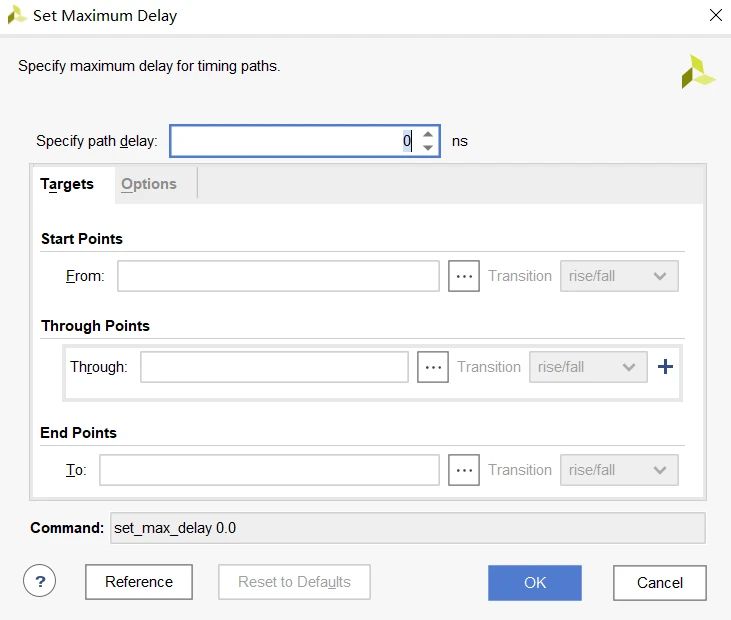

以如下约束为例,最大延时约束的起点为有效起点

set_max_delay 5 -from [get_pins FD1/C]

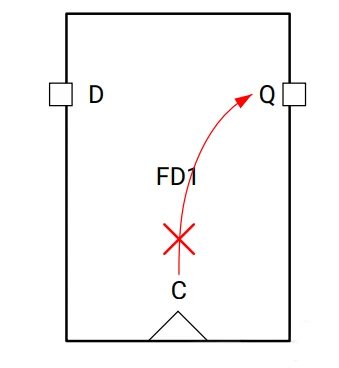

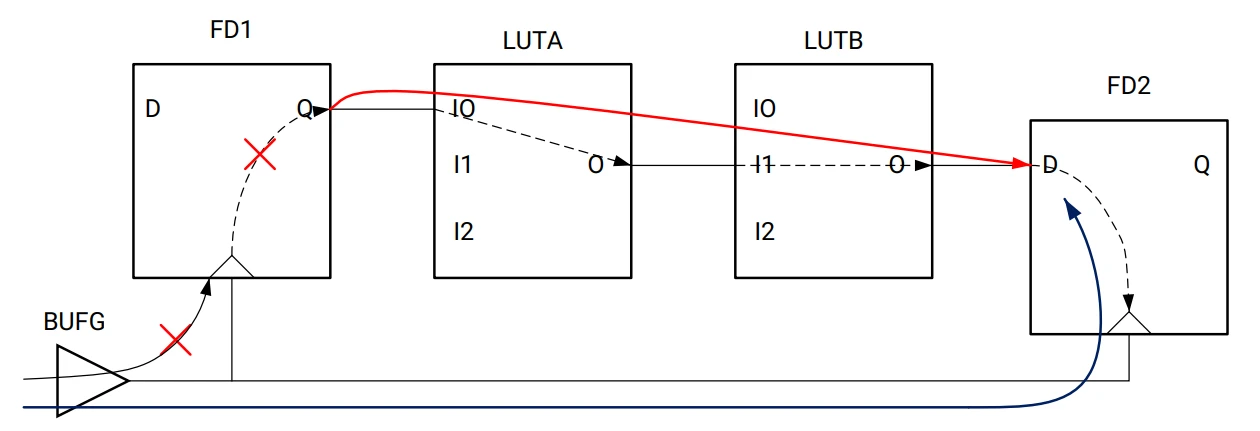

如果约束设置到FD1/Q,时序分析工具将会断开从C->Q的路径,从而使得引脚Q为有效的起点。这种为了创建有效的起点而将时序路径断开的做法称为路径分段,路径分段对最大时延和最小时延都会有影响,同时也会影响经过这些节点(FD1/Q,FD1/C)的时序约束。

set_max_delay 5 -from [get_pins FD1/Q]

路径分段的影响

有序设置最大/最小时延导致路径分段,对于从起点FD1/Q的时序路径将无启动时钟,因为终点的时钟偏斜将会考进来。因此,将有可能导致大的时钟偏斜,如下图所示。

在路径分段后,将没有默认的hold要求时间,如果没有选择-datapath_only选项,使用set_min_delay命令设置hold要求时间。正式由于分段带来风险,出现路径分段时将会有告警提示。

如果一定要将输出FD1/Q最为约束的起点,而又不想去考虑时钟偏斜的影响,则可以勾选-datapath_only来解决。

set_max_delay 5 -from [get_pins FD1/C] -datapath_only类似的,如果设置了一个无效的终点时,为了该节点成为有效的终点,也会出现路径分段,

以LUTA/O为终点为例

set_max_delay 5 -from [get_pins LUTA/O]

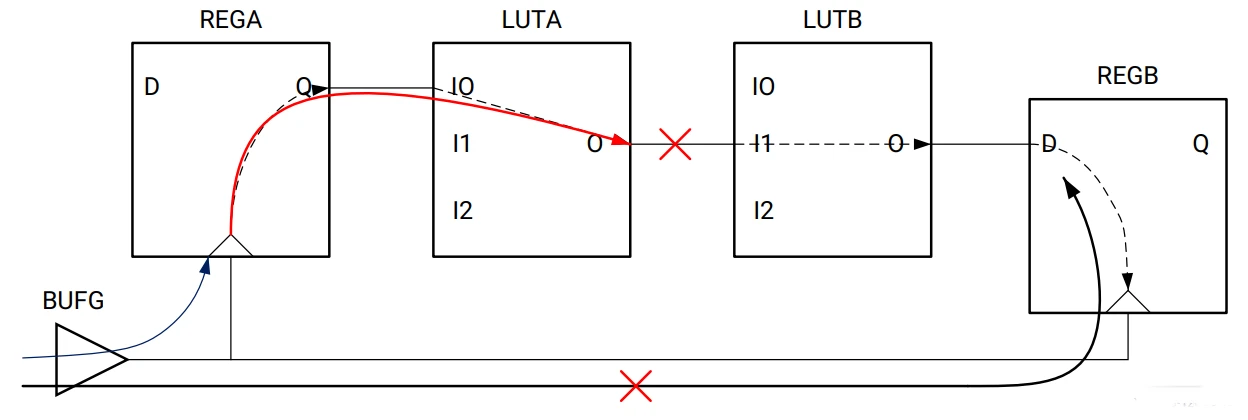

为了使得LUTA/O为有效的终点,时序分析工具将会断开LUTA/O后面的路径,因此,所有经过LUTA/O的setup/hold路径都会受影响,对于REGA/C为起点和LUTA/O为终点的路径,时钟偏斜将会很大。

在下图中,设置约束

set_max_delay 6 -from [get_pins LUTA/O] -to [get_pins REGB/D]由于LUTA/O不是有效的起点,将在LUTA/O处出现路径分段,LUTA/I0到LUTA/O的时序路径将断开。尽管约束只设置在了LUTA/O和REGB/D间,REGA/C到REGC/D的路径也受影响被断开。

路径分段与时序例外

路径分段也可能导致时序例外的优先级告警,特别是对于set_clock_groups和set_max_delay,如以下两个场景

场景1

set_max_delay <ns> -datapath_only -from <instance> -to <instance>最大延迟约束设置在两个instance中,如果instance设有set_clock_groups -asynchronous约束,当vivado选择instance的一个有效的起点时,set_max_delay约束将会被覆盖

场景2

set_max_delay <ns> -datapath_only -from <pin> -to <pin | instance>约束是从pin引脚到inst的引脚,此时,如果instance设有set_clock_groups -asynchronous约束,set_max_delay约束将不会被覆盖。原因是路径分段将让路径起点pin不再被认为是第一个时钟域所启动的起点,因此set_max_delay不会被覆盖,从而约束有效。

三、工程示例

3.1 工程代码

以跨时钟域路径ff1_reg/C到ff2_reg/D的路径为例,设计代码

- module timing(d1,d2,clk1,clk2,ce,ff2);

- input d1,d2,clk1,clk2,ce;

- output ff2;

- reg ff1,ff2;

- wire comb;

- always@(posedge clk1,negedge ce)

- begin

- if(!ce)

- begin

- ff1<=0;

- end

- else begin

- ff1<=d1;

- end

- end

- assign comb=ff1&d2;

- always@(posedge clk2,negedge ce)

- begin

- if(!ce)

- ff2<=0;

- else begin

- ff2<=comb;

- end

- end

- endmodule

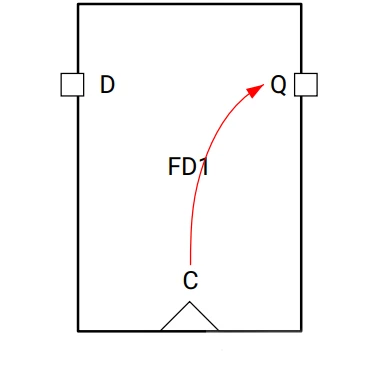

网表连接

约束设置

- set_max_delay -from [get_pins ff1_reg/C] -to [get_pins ff2_reg/D] 5.000 //设置clk的周期

- set_min_delay -from [get_pins ff1_reg/C] -to [get_pins ff2_reg/D] 2.000 //设置clk2的周期

- create_clock -period 10.000 -name clk1 -waveform {0.000 5.000} [get_ports clk1] //max_delay值为5

- create_clock -period 7.000 -name clk2 -waveform {0.000 3.500} [get_ports clk2] //min_delay值为2

3.2 时序报告

在report timing summary中,查看inter-clock paths中查看跨时钟域路径,在setup分析中,setup requirement即为设置的set_max_delay值5ns。

hold分析的requirement值为set_min_delay值2ns

在目的时钟路径上,时延值直接加上设置的时延值

总结:set_max_delay设置的值即为该路径的setup Requirments值,set_min_delay设置的值即为该路径的holdup Requirments值

四、参考资料

用户手册:ug903-vivado-using-constraints-en-us-2022.2.pdf

链接:https://pan.baidu.com/s/17AK_-J4wRXiFLtLTorlrwg?pwd=mylt

提取码:mylt