热门标签

热门文章

- 1JavaParser的快速介绍_java parser tutorial

- 2深入剖析 Android 网络开源库 Retrofit 的源码详解_android源码开放网络

- 3redis学习笔记7-阻塞_redis hugepage写操作 是什么

- 4A站 的 Swift 实践 ,收获总结。_swift 实践 改造

- 5推荐文章标题:利用FlutterFire打造跨平台的Firebase应用

- 6RabbitMQ MQTT TLS相关配置

- 7中兴新支点操作系统加入腾讯发起的OpenCloudOS开源社区:希望百花齐放_新支点默认字体都是开源字体吗

- 8Java 单链表的反转_单向链表反转java

- 9仓颉编程语言全攻略:学习秘籍+内测资格申请秘籍!_华为仓颉编程语言官网

- 10Variables Reference for vscode

当前位置: article > 正文

VIO你用对了吗_vio使用

作者:我家自动化 | 2024-06-11 18:39:26

赞

踩

vio使用

VIO(Virtual Input/Output)有两个主要功能

监测设计中的内部信号;

驱动设计中的内部信号。

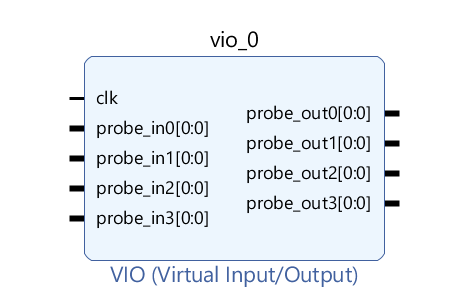

既然是Virtual(虚拟的),就表明这个输入或输出并不是真实存在于FPGA设计中。下图显示了VIO的输入、输出管脚。其中,输入、输出管脚最大可支持到256位。如果需要监测设计中的某个信号,则需要将该信号连接到VIO的输入端;如果需要驱动设计中的某个信号,则需要将该信号与VIO的输出端相连。

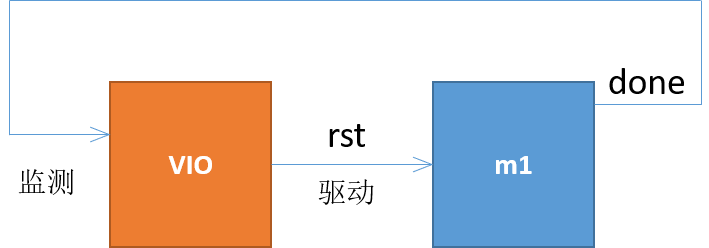

例如,需要监测模块m1的输出信号done,则将done信号连接到VIO的输入端probe_in0;同时需要驱动m1的复位信号,则将复位信号rst连接到VIO的输出端probe_out0。不难看出,就监测功能而言,VIO类似于一个简单的显示器,显示待监测信号的状态;就驱动功能而言,VIO类似于板卡上的一个按钮开关。

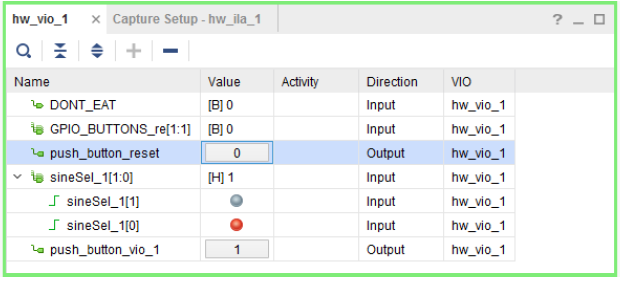

即使设计中只有VIO而没有ILA,Vivado也会生成相应的.ltx文件。打开Vivado Logic Analyzer之后,添加信号到VIO窗口,如下图所示,即可监测信号,或者改变驱动信号的值。

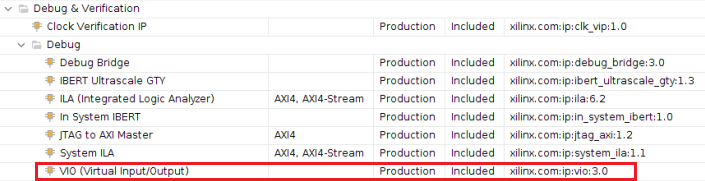

VIO以IP Core的形式存在于Vivado IP Catalog中,如下图所示。不同于ILA,VIO只能通过实例化的方式在设计中使用,而不能通过类似于ILA直接在综合后的网表中插入的方式使用。同时,也可以在Block Design中使用VIO。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/我家自动化/article/detail/704349

推荐阅读

相关标签